时序逻辑电路设计题

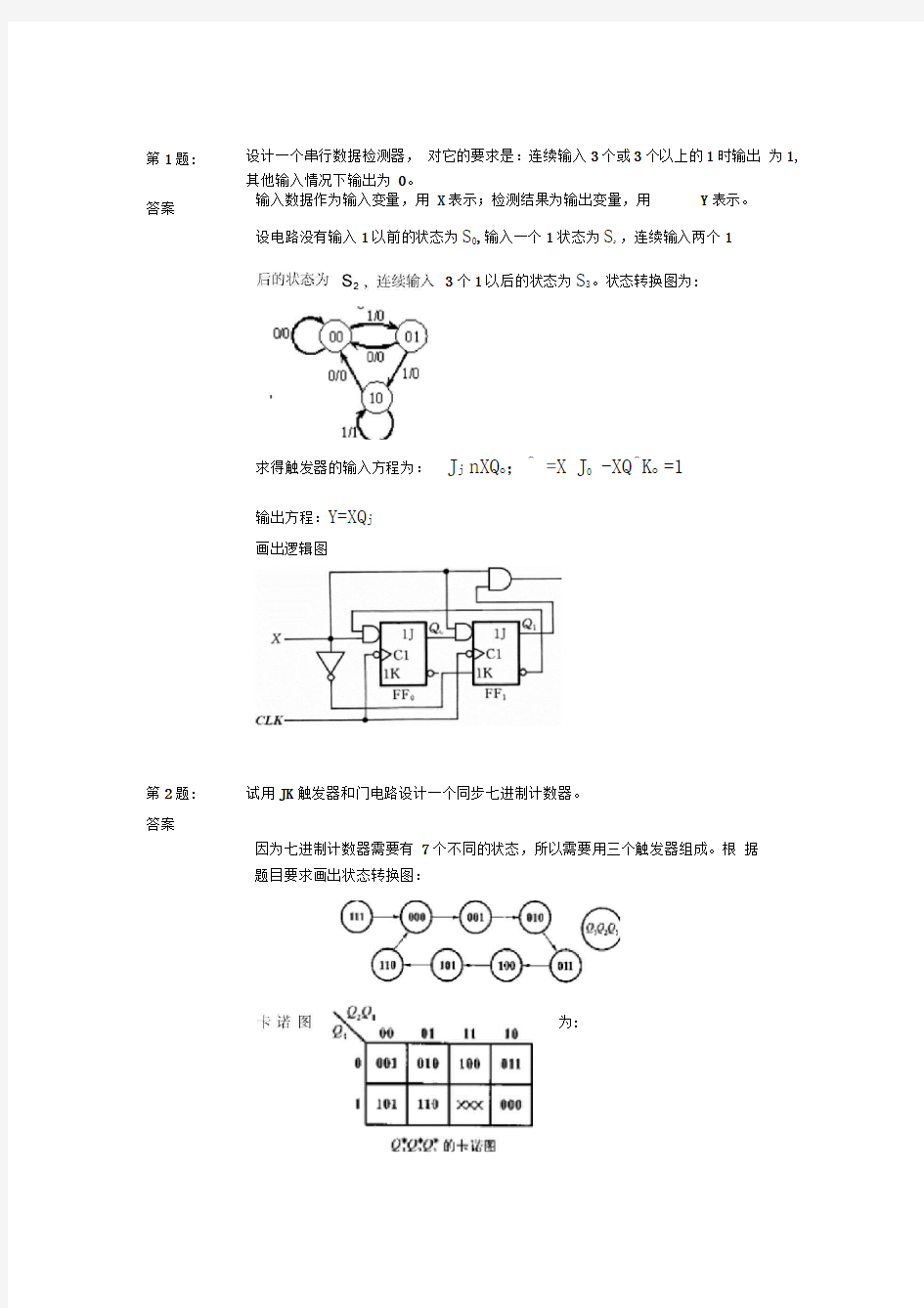

设计一个串行数据检测器, 对它的要求是:连续输入3个或3个以上的1时输出 为1,

其他输入情况下输出为 0。

输入数据作为输入变量,用 X 表示;检测结果为输出变量,用 Y 表示。 设电路没有输入1以前的状态为S 0,输入一个1状态为S ,,连续输入两个1

求得触发器的输入方程为: J j nXQ o ;^ =X J 0 -XQ^K o =1 输出方程:Y=XQ j 因为七进制计数器需要有 7个不同的状态,所以需要用三个触发器组成。根 据题目要求画出状态转换图:

为: 第1题: 答案

3个1以后的状态为S 3。状态转换图为: 第2题:

答案

试用JK 触发器和门电路设计一个同步七进制计数器。 画出逻辑图

从卡诺图得到的状态方程为: Q ; A O ;QZ ;Q0")Q ;"Q :)G 驱动方程为: b : =P ;P : + QWX (Q&jQ :mQi f j t =^.; & =仏 」人=Q“ Kg ) b =(山込八A ; = i 设计得到的逻辑电路图为: 2 爲 %

设计一 011”序列检测器,每当输入 011码时,对应最后一个 1,电路输出为1。

画出原始状态图(或称转移图)

输入端X :输入一串行随机信号

输出端Z :当X 出现011序列时,Z=1 ;否则Z=0

第3题:

答案

相关主题