《模式识别》线性分类器设计实验报告

《模式识别》实验报告

三、线性分类器实验

1.(a)产生两个都具有200 个二维向量的数据集X1 和X1 ’。向量的前半部分来自m1=[-5;0]的正态分布,并且S1=I 。向量的后半部分来自m2=[5;0]的正态分布,并且S1=I。其中I是一个2×2 的单位矩阵。

(b)在上面产生的数据集上运用Fisher 线性判别、感知器算法和最小平方误差判别算法,需要初始化参数的方法使用不同的初始值。

(c)测试每一种方法在X1 和X1 ’ 上的性能(错误率)。

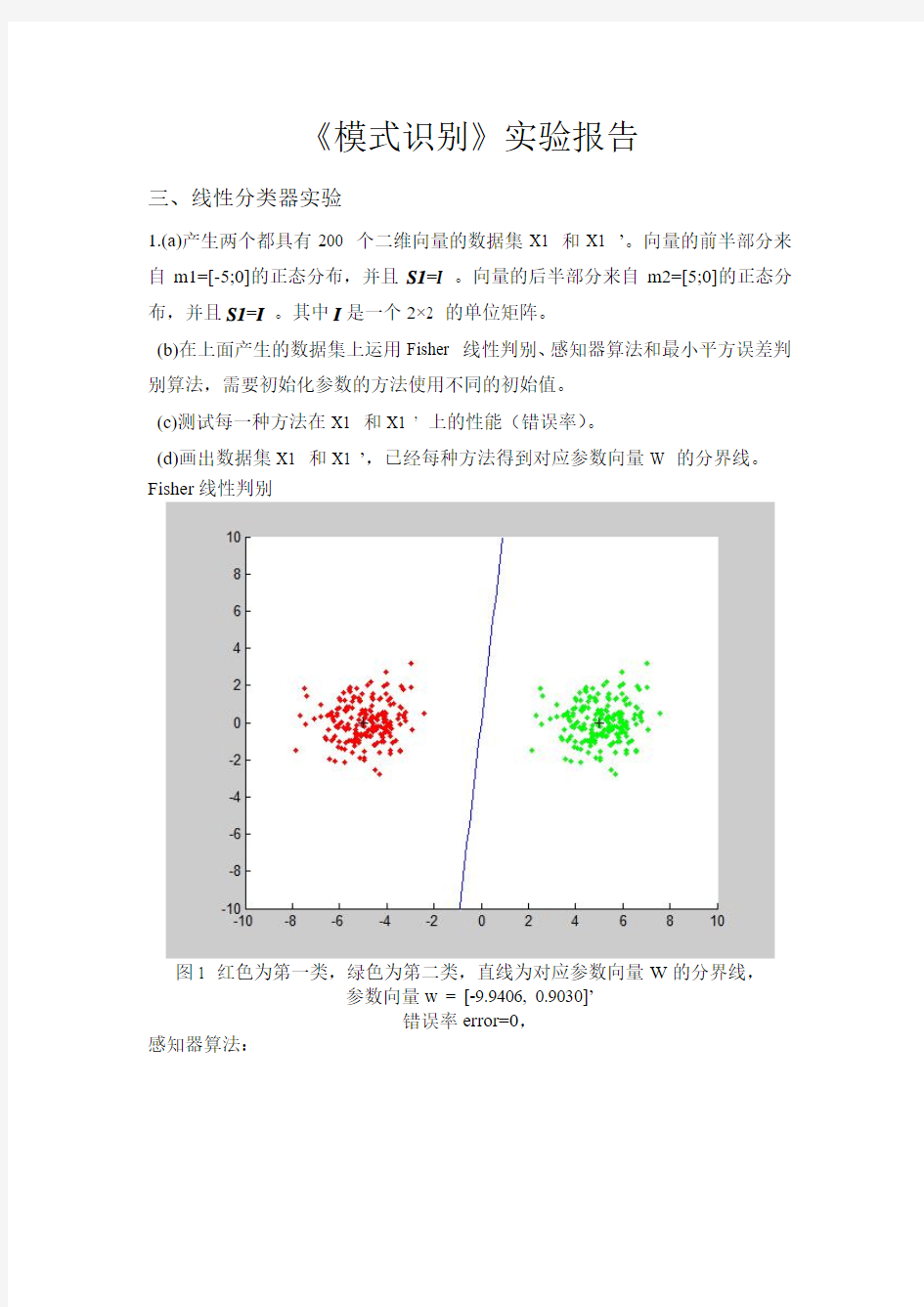

(d)画出数据集X1 和X1 ’,已经每种方法得到对应参数向量W 的分界线。Fisher线性判别

图1 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,

参数向量w = [-9.9406, 0.9030]’

错误率error=0,

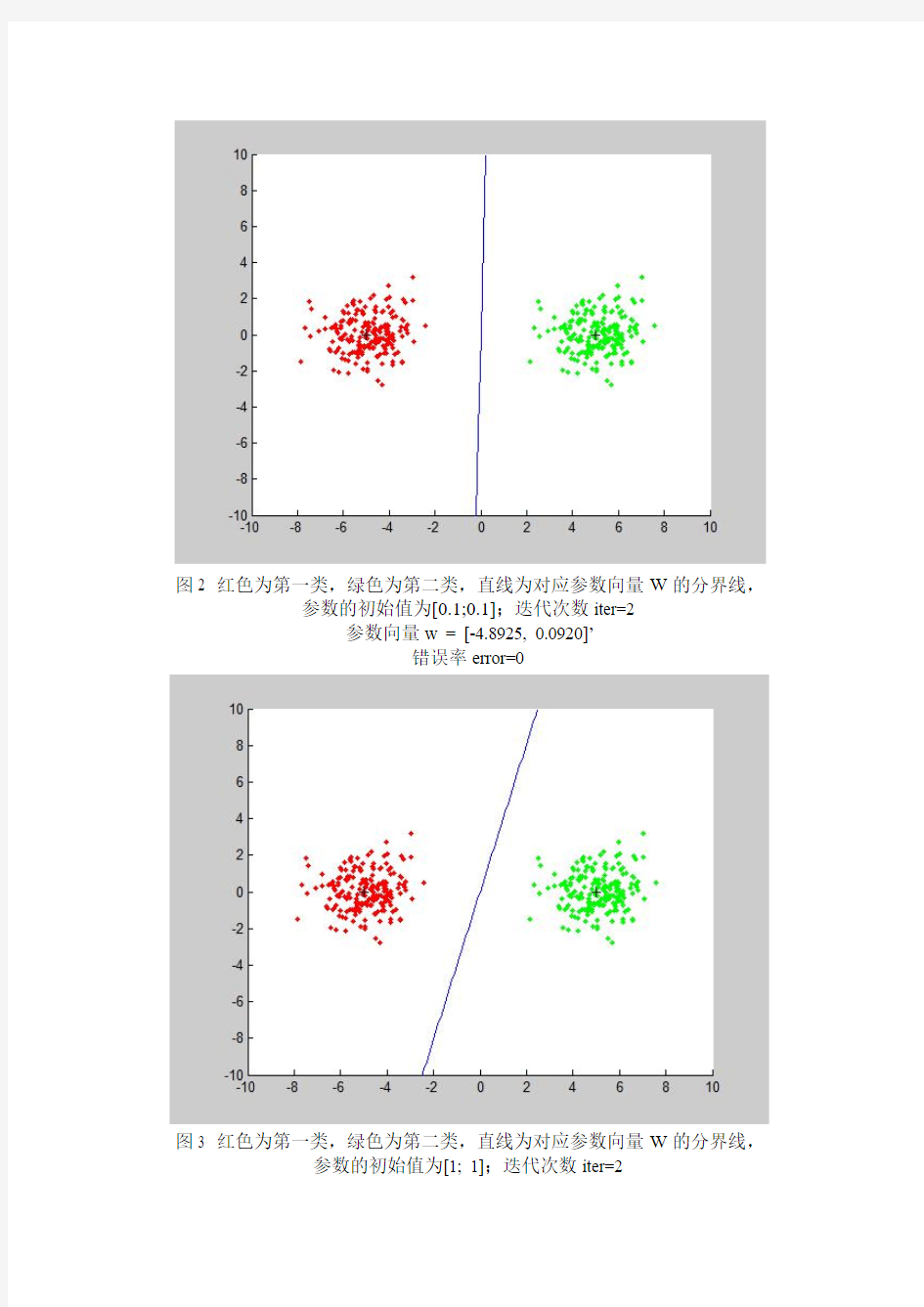

感知器算法:

图2 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[0.1;0.1];迭代次数iter=2

参数向量w = [-4.8925, 0.0920]’

错误率error=0

图3 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[1; 1];迭代次数iter=2

参数向量w = [-3.9925, 0.9920]’

错误率error=0

图4 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[10; 10];迭代次数iter=122

参数向量w = [-5.6569, 7.8096]’

错误率error=0

图5 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[50; 50];迭代次数iter=600

参数向量w = [-27.0945, 37.4194]’

错误率error=0

图6 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[50; 100];迭代次数iter=1190

参数向量w = [-54.0048, 74.5875]’

错误率error=0

最小平方误差判别算法:

图7 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[0.1; 0.1];参数向量w = [-0.1908, -0.0001]’

错误率error=0

图8 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[0.5; 0.5];参数向量w = [-0.1924, 0.1492]’

错误率error=0

图9 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[1; 0.5];参数向量w = [-0.1914, 0.0564]’

错误率error=0

图10 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[1; 1];参数向量w = [-0.1943, 0.3359]’

错误率error= 0.0050

2.重复1.中的实验内容,数据集为X2 和X2 ’。向量的前半部分来自m1=[-2;0]的正态分布,并且S1=I。向量的后半部分来自m2=[2;0]的正态分布,并且S1=I。Fisher线性判别

图11 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,

参数向量w = [-3.9763, 0.3612]’

错误率error=0.1125,

感知器算法:

图12 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[0.1;0.1];迭代次数iter=10000

参数向量w = [-0.2302, 0.0322]’

错误率error= 0.0200

图13 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[1;1];迭代次数iter=10000

参数向量w = [-0.0319, 0.0070]’

错误率error= 0.0225

图14 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[10;10];迭代次数iter=10000

参数向量w = [-0.0241, -0.0479]’

错误率error= 0.1900

最小平方误差判别算法:

参数的初始值为[0.1; 0.1];参数向量w = [-0.1908, -0.0001]’

错误率error=0.02

图16 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[0.5; 0.5];参数向量w = [-0.3505, 0.2484]’

错误率error= 0.0425

参数的初始值为[1; 0.5];参数向量w = [-0.3108, 0.2273]’

错误率error= 0.0450

3.重复1.中的实验内容,数据集为X3 和X3 ’。向量的前半部分来自[-1;0]的正态分布,并且S1=I。向量的后半部分来自[1;0]的正态分布,并且S1=I。Fisher线性判别

图18 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,

参数向量w = [-1.9881, 0 0.1806]’

错误率error= 0.2475,

感知器算法:

图19 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[0.1;0.1];迭代次数iter=10000

参数向量w = [-0.0187, 0.0175]’

错误率error= 0.2250

图20 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[1;1];迭代次数iter=10000

参数向量w = [-0.3430, 0.0430]’

错误率error= 0.1675

图21 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[10;10];迭代次数iter=10000

参数向量w = [-0.0332, 0.0061]’

错误率error= 0.1650

图22 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,

参数的初始值为[50;50];迭代次数iter=10000

参数向量w = [-0.3722, -0.0620]’

错误率error= 0.1725

最小平方误差判别算法:

图23 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[0.1; 0.1];参数向量w = [-0.2688, 0.0290]’

错误率error= 0.1650

图24 红色为第一类,绿色为第二类,直线为对应参数向量W的分界线,参数的初始值为[0.5; 0.5];参数向量w = [-0.1174, 0.2402]’

错误率error= 0.3425

4.讨论从以上1.~3.实验中获得的结果。

当样本明显线性可分时,三种判别方法都能将样本很好地区分,只是有初始化的感知器算法在不同的初始化下收敛到不同的局部最优参数值,且收敛次数随参数的变化而变化,最小平方误差判别算法在初始参数不同时收敛到的局部最优参数也不同。且通过图形可以明显看到,感知器算法和最小平方误差判别算法在初始参数较小的时候能收敛到较好的参数,随初始化参数的变大,最终参数越差,最后最小平方误差判别算法都不能完全正确区分两类样本了。

当样本线性不可分时,三种判别方法都不能将样本无差地区分,且同线性可分一样,初始化参数的不同,最终的参数也不同,初始化参数可影响分类算法的分来性能的好坏。

触发器功能的模拟实现实验报告-

武汉轻工大学数学与计算机学院 数字逻辑实验报告 学校:武汉轻工大学 院系:数学与计算机学院 班级:计算机类1304班 姓名:田恒 学号: 1305110089 指导老师:刘昌华 2014年12月10日

目录 1、实验名称 2、实验目的 3、实验原理 4、实验环境 5、实验内容 一、DFF仿真分析 二、“维持阻塞”型DFF仿真分析 三、思考练习 四、故障排除 五、实验总结

【实验名称】触发器功能的模拟实现 【实验目的】学习时序电路的设计,了解基本触发器的功能,利用QuartusII软件的原理图输入,设计一个钟控R-S触发器形成的D触发器和边沿触发型D触发器,并验证其功能。 【实验原理】(1)钟控R-S触发器,在时钟信号作用期间,当输入R、S同时为1时,触发器会出现状态不稳定现象。为了解决这个问题,对钟控R-S触发器的控制电路进行修改,用G4门的输出信号替换G3门的S输入信号,将剩下的输入R记作D,就形成只有一个输入端的D触发器。 (2)在上述D触发器的基础上增加“维持”、“阻塞”结构,从而形成“维持阻塞”型D触发器。

【实验环境】PC机(Windows xp,QuartusII) 【实验内容】QuartusII开发数字电路的设计流程完成DFF和“维持阻塞”型D触发器的原理设计输入,编译仿真和波形仿真。 一、DFF仿真分析: step1、启动QuartusII Step2、建立工作库目录文件夹以便设计工程项目的存储 Step3、输入设计:根据上部原理图完成原理图文件,截图如下: Step4、单击存盘命令新建工程 Step5、编译综合 Step6、仿真测试 Step7、仿真结果

电磁场HFSS实验报告

实验一? T形波导的内场分析 实验目的? 1、?熟悉并掌握HFSS的工作界面、操作步骤及工作流程。????? 2、?掌握T型波导功分器的设计方法、优化设计方法和工作原理。?实验仪器 1、装有windows 系统的PC 一台 2、或更高版本软件 3、截图软件 实验原理 本实验所要分析的器件是下图所示的一个带有隔片的T形波导。其中,波导的端口1是信号输入端口,端口2和端口3是信号输出端口。正对着端口1一侧的波导壁凹进去一块,相当于在此处放置一个金属隔片。通过调节隔片的位置可以调节在端口1传输到端口2,从端口1传输到端口3的信号能量大小,以及反射回端口1的信号能量大小。 T形波导 实验步骤 1、新建工程设置: 运行HFSS并新建工程:打开 HFSS 软件后,自动创建一个新工程: Project1,由主菜单选 File\Save as ,保存在指定的文件夹内,命名为Ex1_Tee;由主菜单选 Project\ Insert HFSS Design,

在工程树中选择 HFSSModel1,点右键,选择 Rename项,将设计命名为 TeeModel。 选择求解类型为模式驱动(Driven Model):由主菜单选HFSS\Solution Type ,在弹出对话窗选择Driven Model 项。 设置长度单位为in:由主菜单选 3D Modeler\Units ,在 Set Model Units 对话框中选中 in 项。。 2、创建T形波导模型: 创建长方形模型:在 Draw 菜单中,点击 Box 选项,在Command 页输入尺寸参数以及重命名;在Attribute页我们可以为长方体设置名称、材料、颜色、透明度等参数Transparent(透明度)将其设为。Material(材料)保持为Vacuum。 设置波端口源励:选中长方体平行于 yz 面、x=2 的平面;单击右键,选择 Assign Excitation\Wave port项,弹出 Wave Port界面,输入名称WavePort1;点击积分线 (Integration Line) 下的 New line ,则提示绘制端口,在绘图区该面的下边缘中部即(2,0,0)处点左键,确定端口起始点,再选上边缘中部即(2,0,处,作为端口终点。 复制长方体:展开绘图历史树的 Model\Vacuum\Tee节点,右键点击Tee项,选择 Edit\Duplicate\Around Axis,在弹出对话窗的Axis项选择Z,在Angel项输入90deg,在 Total Number 项输入2,点OK,则复制、添加一个长方体,默认名为TEE_1。重复以上步骤,在Angel项输入-90,则添加第3个长方体,默认名Tee_2.

静态存储器扩展实验报告

静态存储器扩展实验报告告圳大学实验报深

微机原理与接口技术 课程名称: 静态存储器扩展实验实验项目名称: 信息工程学院学院: 专业:电子信息工程

指导教师:周建华 32012130334 学号:班级:电子洪燕报告人:班 2014/5/21 实验时间: 实验报告提交时间:2014/5/26 教务部制. 一.实验目的与要求: 1. 了解存储器扩展的方法和存储器的读/写。 2. 掌握CPU对16位存储器的访问方法。

二.实验设备 PC机一台,TD-PITE实验装置或TD-PITC实验装置一套,示波器一台。 三.实验原理VCC28A141WE27A122A1326A73A8254A6存储器是用来存储信息的A924A55A1123A46OE22A3762256A10218A2CS209A1部件,是计算机的重要组成部D719A010D618D011D517D112D416D213D315GND14管组成的是由MOS分,静态RAM触发器电路,每个触发器可以存放1位

信息。只要不掉电,所储存的信息就不会丢失。因此,静态RAM工作稳定,不要外加刷新电路,使用方便。 但一般SRAM 的每一个触发器是由6个晶体管组成,SRAM 芯片的集成度不会太高,目前较常用的有6116(2K×8位),图4.1 62256引脚图6268位)622532位。本验平台上选. 用的是62256,两片组成32K×16位的形式,共64K字节。 62256的外部引脚图如图4.1所示。 本系统采用准32位CPU,具有16位外部

数据总线,即D0、D1、…、D15,地址总线为BHE#(#表示该信号低电平有效)、BLE #、A1、A2、…、A20。存储器分为奇体和偶体,分别由字节允许线BHE#和BLE#选通。 存储器中,从偶地址开始存放的字称为规则字,从奇地址开始存放的字称为非规则字。处理器访问规则字只需要一个时钟周期,BHE#和BLE#同时有效,从而同时选通存储器奇体和偶体。处理器访问非规则字却需要

湘潭大学计算机原理实验二ROM存储器与RAM存储器实验报告

计算机原理与设计 实验报告 实验二存储器实验 :XXX 学号:2013551728

班级:13级软件工程2班 实验日期:2014年10 月29 日 1.FPGA中ROM定制与读出实验 一.实验目的 1、掌握FPGA中ROM的设置,作为只读存储器ROM的工作特性和配置方法。 2、用文本编辑器编辑mif文件配置ROM,学习将程序代码以mif格式文件加载于ROM中; 3、在初始化存储器编辑窗口编辑mif文件配置ROM; 4、验证FPGA中ROM的功能。 二.实验原理 ALTERA的FPGA中有许多可调用的模块库,可构成如rom、ram、fifo等存储器结构。CPU 中的重要部件,如RAM、ROM可直接调用他们构成,因此在FPGA中利用嵌入式阵列块EAB 可以构成各种结构的存储器,ROM是其中的一种。ROM有5组信号:地址信号address[ ]、数据信号q[ ]、时钟信号inclock、outclock、允许信号memenable,其参数都是可以设定的。由于ROM是只读存储器,所以它的数据口是单向的输出端口,ROM中的数据是在对FPGA 现场配置时,通过配置文件一起写入存储单元的。图2-1-1中的ROM有3组信号:inclk——输入时钟脉冲;instruction[31..0]——lpm_ROM的32位数据输出端;a[4..0]——lpm_ROM的5位读出地址。 实验中主要应掌握以下三方面的内容: (1)ROM的参数设置; (2)ROM中数据的写入,即FILE初始化文件的编写;

(3)ROM的实际应用,在GW48_CP+实验台上的调试方法。 三.实验步骤 (1)新建工程。工程名是scinstmem.qpf。 (2)用初始化存储器编辑窗口编辑ROM配置文件(文件名.mif)。这里预先给出后面将要用到的指令存储器初始化文件:scinstmem.mif 。如下图,scinstmem.mif中的数据是机器指令代码。 scinstmem.mif中的数据 (3)模块设计。用图形编辑,使用工具Mega Wizard Plug-In Manager,定制指令存储器rom 宏功能块。设置地址总线宽度address[]和数据总线宽度q[],分别为5位和32位,并添加输入输出引脚,如图设置和连接。 ROM的结构图 在设置rom数据参数选择项file的对应窗口中(下图),用键盘输入ROM配置文件的路径(scinstmem.mif),然后设置在系统ROM/RAM读写允许,以便能对FPGA中的ROM在系统读写。

实验十四 存储器扩展机读写实验

实验十四存储器扩展机读写实验 一、实验目的 (1)通过阅读并测试示例程序,完成程序设计题,熟悉静态RAM的扩展方法。 (2)了解8086/8088与存储器的连接,掌握扩展存储器的读写方法。 二、实验内容 1.实验原理(62256RAM介绍) 62256是32*8的静态存储器,管脚如图所示。其中:A0~A14为地址线,DB0~DB7为数据线,/cs为存储器的片选,/OE为存储器数据输出选通信号,/WE为数据写入存储器信号。62256工作方式如下图。 /CS /WE /OE 方式DB-~DB7 H X X 未选中高阻 L H H 读写禁止高阻 L L H 写IN L H L 读OUT 2.实验内容 设计扩展存储电器的硬件连接图并编制程序,讲字符A~Z循环存入62256扩展RAM 中,让后再检查扩展存储器中的内容。 三、程序设计 编写升序,将4KB扩展存储器交替写入55H和0AAH。 程序如下: RAMADDR EQU 0000H RAMOFF EQU 9000H COUNT EQU 800H CODE SEGMENT ASSUME CS:CODE START: PROC NEAR MOV AX,RAMADDR MOV DS,AX MOV BX,RAMOFF MOV CX,COUNT MOV DL,55h MOV AX ,0AAH REP: MOV [BX],DL INC BX MOV [BX],AX INC BX LOOP REP JMP $ CODE ENDS END START 四、实验结果 通过在软件上调试,运行时能够看到内存地址的改变,证明此扩展的程序成功实现了。 五、实验心得

存储器管理实验报告.docx

操作系统实验报告 存储器管理 学院电信学院 专业计算机科学与技术 班级 14级计科一班 实验题目动态分区分配 实验组别第三组 指导老师曹华

一、实验目的 了解动态分区分配方式中使用的数据结构和分配算法,并进一步加深对动态分区存储管理方式及其实现过程的理解。 二、实验内容 用C语言分别实现采用首次适应算法和最佳适应算法的动态分区分配过程alloc()和回收过程free()。其中,空闲分区通过分区链来管理,在进行内存分配时,系统优先使用空闲区低端的空间。 请分别用首次适应算法和最佳适应算法进行内存块的分配和回收,要求每次分配和回收后显示出空闲内存分区链的情况。 三、实验主要仪器设备 软件环境:VC++6编程环境 四、实验原理及设计方案 1.实验原理: 可变分区调度算法有:最先适应分配算法,循环首次适应算法,最佳适应算法,最坏适应算法。 首次适应算法(First-fit):当要分配内存空间时,就查表,在各空闲区中查找满足大小要求的可用块。只要找到第一个足以满足要求的空闲块就停止查找,并把它分配出去; 如果该空闲空间与所需空间大小一样,则从空闲表中取消该项;如果还有剩余,则余下的部分仍留在空闲表中,但应修改区分大小和分区始址。 用户提出内存空间的申请:系统根据申请者的要求,按照一定的分配策略分析内存空间的使用情况,找出能满足请求的空闲区,分给申请者;当程序执行完毕或主动归还内存资源时,系统要收回它所占用的内存空间或它归还的部分内存空间。 最佳适应算法(Best-fit):当要分配内存空间时,就查找空闲表中满足要求的空闲块,并使得剩余块是最小的。然后把它分配出去,若大小恰好合适,则直按分配;若有剩余块,则仍保留该余下的空闲分区,并修改分区大小的起始地址。 内存回收:将释放作业所在内存块的状态改为空闲状态,删除其作业名,设置为空,并判断该空闲块是否与其他空闲块相连,若释放的内存空间与空闲块相连时,则合并为同一个空闲块,同时修改分区大小及起始地址。 每当一个进程被创建时,内存分配程序首先要查找空闲内存分区链,从中寻找一个合适的空闲块进行划分,并修改空闲内存分区链,系统根据回收区的首址,从空闲区链中找到相应的插入点,此时出现如下四种情况: (1)回收区与插入点的前一个空闲区F1相邻接,此时可将回收区直接与F1合并,并修改F1的大小; (2)回收区与插入点的后一个空闲分区F2相邻接,此时可将回收区直接与F2合并,并用回收区的首址作为新空闲区的首址,大小为二者之和; (3)回收区同时与插入点的前后两个空闲分区邻接,此时需将三者合并; (4)回收区不与任何一个空闲区邻接,此时应建一新的表项 2.主要数据结构的说明 定义一个空闲区说明表结构

实验六 触发器实验报告

实验五 触发器实验报告 [实验目的] 1. 理解Oracle 触发器的种类和用途 2. 掌握行级触发器的编写 [预备知识] 1. PL/SQL 程序设计 [实验原理] 1. 建立触发器 CREA TE [OR REPLACE] TRIGGER <触发器名> BEFORE|AFTER INSERT|DELETE|UPDA TE OF <列名> ON <表名> [FOR EACH ROW] WHEN (<条件>)

T型功分器的设计与仿真.

T型功分器的设计与仿真 1.改进型威尔金森功分器的工作原理 功率分配器属于无源微波器件,它的作用是将一个输入信号分成两个(或多个)较小功率的信号,工程上常用的功分器有T型结和威尔金森功分器。 威尔金森功分器是最常用的一种功率分配器。图1所示的为标准的二路威尔 金森等功率分配器。从合路端口输入的射频信号被分成幅度和相位都相等的两路信号,分别经过传输线Bl和BZ,到达隔离电阻两端,然后从两个分路端口输出,离电阻R两端的信号幅度和相位都相等,R上不存在差模信号,所以它不会消耗功率,如果我们不考虑传输线的损耗,则每路分路端口将输出二分之一功率的信号。 图1威尔金森功分器 但是这种经典威尔金森等功率分配器有几个缺点: 1、大功率应用的时候,要求隔离电阻的耗散功率大因此电阻的体积也会比较大 2、如果功分器应用于较高的频段,波长就会与大功率电阻的尺寸相比拟,这样就需要考虑电阻的分布参数。 3、为了提高功分器性能,就要尽量减小Bl和BZ这两段传输线之间的藕合,因此在实际设计时,要求四分之一波长传输线Bl、BZ之间的距离较大,在低频应用时,由于四分之一波长较长,占用面积还是太大了,此外,四分之一波长传输线Bl、BZ的阻抗较高,因此线宽较细,制板的相对误差更大[24]。为克服这些缺点,本文采用了一种改进型的威尔金森等功率分配器,如图2所示

图2 改进型威尔金森功分器 可以看到,它仅由四段传输线组成,没有隔离电阻。传输线A 、Cl 、CZ 的特 征阻抗均为Z0。传输线B 位于A 和Cl 、CZ 之间,它的电长度为四分之一波长, 特征阻抗为Z0/2。从合路端输入的信号,通过传输线B ,被分成幅度和相位相等的的两路信号,分别经过传输线Cl 和C2到达分路端口一和二,在整个结构中,传输线B 起到了阻抗变换的作用。从传输线A 、B 相接处向左看,输入阻抗为Z0。从传输线B 与C1、C2相接处向右看,输入阻抗为Z0/2。利用四分之一阻抗变换器的原理我们知道,传输线的特征阻抗为2/00Z Z ?,即Z0/2。因此,整个电路处于功率分配与合成时,在中心频点处,三个端口都能匹配良好,没有反射。这种改进型的结构克服了标准威尔金森功分器的一系列缺点,同时由于省略了隔离电阻,所以成本降低,也不存在电阻分布参数的问题,与传统威尔金森功分器相比,减少了一段四分之一波长传输线,另外,构成变换器的四分之一波长传输线B 的特征阻抗较低,线宽较宽,能有效降低制板误差。 2功分器的设计与仿真 通过前面的分析,我们知道改进型威尔金森功分器四段传输线特征阻抗之间 的比例关系。由此可得,传输线A 、C1和C2的特征阻抗均为50Ω,而传输线B 的特征阻抗为352/0=Z Ω 为了实现右旋圆极化,经过C2输出的信号要比经过Cl 的相位超前?90,即Cl 要比C2长λ4/1g (λg 为中心频率所对应的介质波长)。设计的功率分配器 如图3所示,传输线段B 的长度约为λ4/1g ,起阻抗变换的作用。传输线段

实验一扩展存储器读写实验

实验一:扩展存储器读写实验 一.实验要求 编制简单程序,对实验板上提供的外部存贮器(62256)进行读写操作。 二.实验目的 1.学习片外存储器扩展方法。 2.学习数据存储器不同的读写方法。 三.实验电路及连线 将P1.0接至L1。CS256连GND孔。 四.实验说明 1.单片机系统中,对片外存贮器的读写操作是最基本的操作。用户藉此来熟悉MCS51单片机编程的基本规则、基本指令的使用和使用本仿真实验系统调试程序的方法。 用户编程可以参考示例程序和流程框图。本示例程序中对片外存贮器中一固定地址单元进行读写操作,并比较读写结果是否一致。不一致则说明读写操作不可靠或该存储器单元不可靠,程序转入出错处理代码段(本示例程序通过熄灭一个发光二极管来表示出错)。读写数据的选用,本例采用的是55(0101,0101)与AA(1010,1010)。一般采用这两个数据的读写操作就可查出数据总线的短路、断路等,在实际调试用户电路时非常有效。 用户调试该程序时,可以灵活使用单步、断点和变量观察等方法,来观察程序执行的流程和各中间变量的值。 2.在I状态下执行MEM1程序,对实验机数据进行读写,若L1灯亮说明RAM读

写正常。 3.也可进入LCA51的调试工具菜单中的对话窗口,用监控命令方式读写RAM,在I状态执行SX0000↓ 55,SPACE,屏幕上应显示55,再键入AA,SPACE,屏幕上也应显示AA,以上过程执行效果与编程执行效果完全相同。 注:SX是实验机对外部数据空间读写命令。 4.本例中,62256片选接地时,存储器空间为0000~7FFFH。 五.实验程序框图 实验示例程序流程框图如下: 六.实验源程序: ORG 0000H LJMP START ORG 0040H START:

触发器实验报告

实验报告 课程名称:数字电子技术基础实验 指导老师: 周箭 成绩:__________________ 实验名称:集成触发器应用 实验类型: 同组学生姓名:__邓江毅_____ 一、实验目的和要求(必填) 二、实验内容和原理(必填) 三、主要仪器设备(必填) 四、操作方法和实验步骤 五、实验数据记录和处理 六、实验结果与分析(必填) 七、讨论、心得 实验内容和原理 1、D →J-K 的转换实验 设计过程:J-K 触发器和D 触发器的次态方程如下: J-K 触发器:n n 1+n Q Q J =Q K +, D 触发器:Qn+1=D 若将D 触发器转换为J-K 触发器,则有:n n Q Q J =D K +。 实验结果: J K Qn-1 Qn 功能 保持 1 1 0 1 置0 1 0 1 1 1 翻转 专业:电卓1501 姓名:卢倚平 学号: 日期:地点:东三

1 0 1 0 0 1 置1 1 1 实验截图: (上:Qn,下:CP,J为高电平时) 2、D 触发器转换为T’触发器实验 设计过程:D 触发器和T’触发器的次态方程如下: D 触发器:Q n+1= D , T’触发器:Q n+1=!Q n 若将D 触发器转换为T’触发器,则二者的次态方程须相等,因此有:D=!Qn。实验截图: (上:Qn,下:!Qn)CP为1024Hz 的脉冲。

3、J-K →D 的转换实验。 ①设计过程: J-K 触发器:n n 1+n Q Q J =Q K +, D 触发器:Qn+1=D 若将J-K 触发器转换为D 触发器,则二者的次态方程须相等,因此有:J=D ,K=!D 。 实验截图: (上:Qn ,下:CP ) (上:Qn ,下:D ) 4、J-K →T ′的转换实验。 设计过程: J-K 触发器:n n 1+n Q Q J =Q K +, T ’触发器:Qn+1=!Qn 若将J-K 触发器转换为T ’触发器,则二者的次态方程须相等,因此有:J=K=1 实验截图:

【原创】南京邮电大学 课程设计 Wilkinson(威尔金森)功分器的设计

南京邮电大学电子科学与工程学院电磁场与无线技术Wilkinson功分器 课题报告 课题名称 Wilkinson功分器 学院电子科学与工程学院 专业电磁场与无线技术 班级 组长 组员 开课时间 2012/2013学年第一学期

一、课题名称 Wilkinson(威尔金森)功分器的设计 二、课题任务 运用功分器设计原理,利用HFSS软件设计一个Wilkinson功分器,中心工作频率3.0GHz。 ?基本要求 实现一个单阶Wilkinson等功分设计,带内匹配≤-10dB,输出端口隔离≤-10dB,任选一种微波传输线结构实现。 ?进阶要求 多阶(N≥2),匹配良好(S11≤-15dB),不等分,带阻抗变换器(输出端口阻抗 不为50Ω),多种传输线实现。 三、实现方式 自选一种或者多种传输线实现,如微带线,同轴线,带状线等,要求输入输出端口阻抗为50Ω,要求有隔离电阻(通过添加额外的端口实现) 四、具体过程 1.计算基本参数 通过ADS Tool中的Linecalc这个软件来进行初步的计算。 在HFSS中选定版型为Rogers RT/duroid 5880 (tm),如具体参数下图

50Ω微带线计算 得到选取微带线宽度约为0.67mm。 70.7Ω微带线计算 得到选取微带线宽度约为0.34mm,由于微带线电长度与其宽度没有必然联系,所以两个分支微带线的长度根据具体情况进行更改。

2.绘制仿真模型 微带单阶功分器

◆微带参数:w50:阻抗为50Ω的微带线宽度;w2:两分支线宽度; l1,l2,l3,l4:各部分微带线长度; rad1,rad2:各部分分支线长度(即半环半径) ◆在本例中,需要调整的调整关键参数为w2,rad1,空气腔参数随关键参数相应调 整即可。 ◆根据计算,此处的吸收电阻值应该为100Ω,但是在实际情况中,选取97Ω。 微带多阶功分器

实习五虚拟存储器实验报告

实习五虚拟存储器 一、实习内容 模拟分页式虚拟存储管理中硬件的地址转换和缺页中断,以及选择页面调度算法处理缺页中断。 二、实习目的 在计算机系统中,为了提高主存利用率,往往把辅助存储器(如磁盘)作为主存储器的扩充,使多道运行的作业的全部逻辑地址空间总和可以超出主存的绝对地址空间。用这种办法扩充的主存储器称为虚拟存储器。通过本实习帮助同学理解在分页式存储管理中怎样实现虚拟存储器。 三、实习题目 本实习有三个题,其中第一题必做,第二、第三题中可任选一个。 第一题:模拟分页式存储管理中硬件的地址转换和产生缺页中断。 [提示]: (1) 分页式虚拟存储系统是把作业信息的副本存放在磁盘上,当作业被选中时,可把作业的开始几页先装入主存且启动执行。为此,在为作业建立页表时,应说明哪些页已在主存,哪些页尚未装入主存,页表的格式为: 其中,标志——用来表示对应页是否已经装入主存,标志位=1,则表示该页已经在主存,标志位=0,则表示该页尚未装入主存。 主存块号——用来表示已经装入主存的页所占的块号。 在磁盘上的位置——用来指出作业副本的每一页被存放在磁盘上的位置。 (2) 作业执行时,指令中的逻辑地址指出了参加运算的操作数存放的页号和单元号,硬件的地址转换机构按页号查页表,若该页对应标志为“1”,则表示该页已在主存,这时根据关系式: 绝对地址=块号 块长+单元号 计算出欲访问的主存单元地址。如果块长为2的幂次,则可把块号作为高地址部分,把单元号作为低地址部分,两者拼接而成绝对地址。按计算出的绝对地址可以取到操作数,完成一条指令的执行。若访问的页对应标志为“0”,则表示该页不在主存,这时硬件发“缺页中断”信号,由操作系统按该页在磁盘上的位置,把该页信息从磁盘读出装入主存后再重新执行这条指令。 (3) 设计一个“地址转换”程序来模拟硬件的地址转换工作。当访问的页在主存时,则形成绝对地址,但不去模拟指令的执行,而用输出转换后的地址来代替一条指令的执行。当访问的页不在主存时,则输出“*该页页号”,表示产生了一次缺页中断。该模拟程序的算法如图5-1。 (4) 假定主存的每块长度为128个字节;现有一个共七页的作业,其中第0页至第3

实验六 触发器实验报告

实验六触发器实验报告 触发器实验报告 [实验目的]1、理解Oracle触发器的种类和用途2、掌握行级触发器的编写 [预备知识]1、 PL/SQL程序设计 [实验原理]1、建立触发器 CREATE [OR REPLACE] TRIGGER <触发器名> BEFORE|AFTER INSERT|DELETE|UPDATE OF <列名> ON <表名> [FOR EACH ROW] WHEN (<条件>)

义,所有字段都是NULL引用示例::new、 customer_name, :old、customer_name3、行级触发器中的谓词在一个多条件触发的触发器中,使用谓词可以区分当前触发的操作的类型:inserting,updating,deleting。 示例: IF Inserting THEN 语句 ; END IF; IF Updating THEN 语句 ; END IF; IF Deleting THEN 语句 ; END IF;4、触发器的限制 SELECT 语句必须是 SELECT INTO 语句或内部游标声明。 行级触发器不可以对触发表进行查询,包括其调用的子过程中。 不允许 DDL 声明和事务控制语句。 如果由触发器调用存储子过程,则存储子程序不能包括事务控制语句。 :old 和 :new 值的类型不能是 LONG 和 LONG RAW。 [实验内容]1、给Customer表增加一列Savings,类型为int,来存放每个顾客的存款总额。A LTER TABLE customer ADD (saving varchar2(30));select * from customer;2、更新Customer表,使得Savings字段的值正确。 3、在Account表上增加一个行级触发器,当对account的balance进行update和insert一个记录时同步修改Customer的Savings字段,保证数据的一致性。

功分器的设计原理

设计资料项目名称:微带功率分配器设计方法 拟制: 审核: 会签: 批准: 二00六年一月

微带功率分配器设计方法 1. 功率分配器论述: 1.1定义: 功率分配器是一种将一路输入信号能量分成两路或多路信号能量输出的器件,也可反过来将多路信号能量合成一路输出,此时也可称为合路器。 1.2分类: 1.2.1功率分配器按路数分为:2路、3路和4路及通过它们级联形成的多路功率分配器。 1.2.2功率分配器按结构分为:微带功率分配器及腔体功率分配器。 1.2.2根据能量的分配分为:等分功率分配器及不等分功率分配器。 1.2.3根据电路形式可分为:微带线、带状线、同轴腔功率分配器。 1.3概述: 常用的功率分配器都是等功率分配,从电路形式上来分,主要有微带线、带状线、同轴腔功率分配器,几者间的区别如下: (1)同轴腔功分器优点是承受功率大,插损小,缺点是输出端驻波比大,而且输出端口间无任何隔离。微带线、带状线功分器优点是价格便宜,输出端口间有很好的隔离,缺点是插损大,承受功率小。(2)微带线、带状线和同轴腔的实现形式也有所不同:同轴腔功分器是在要求设计的带宽下先对输入端进行匹配,到输出端进行分路;而微带功分器先进行分路,然后对输入端和输出端进行匹配。

下面对微带线、带状线功率分配器的原理及设计方法进行分析。 2.设计原理: 2.1分配原理: 微带线、带状线的功分器设计原理是相同的,只是带状线的采用的是对称性空气填充或介质板填充,而微带线的主要采用的是非对称性部分介质填充和部分空气填充。下面我们以一分二微带线功率分配的设计为例进行分析。传输线的结构如下图所示,它是通过阻抗变换来实现的功率的分配。 图1:一分二功分器示意图 在现有的通信系统中,终端负载均为50Ω,也就是说在分支处的阻抗并联后到阻抗结处应为50Ω。如上图匹配网络,从输入端口看Ω==500Z Z in ,而Ω==50//21in in in Z Z Z ,且是等分的,所以1in Z =2in Z ,①处1in Z 、②处2in Z 的输入阻抗应为100Ω,这样由①、②处到输出终端50Ω需要通过阻抗变换来实现匹配。 2.2阶梯阻抗变换: 在微波电路中,为了解决阻抗不同的元件、器件相互连接而又不使其各自的性能受到严重的影响,常用各种形式的阻抗变换器。其中最简单又最常用的四分之一波长传输线阶梯阻抗变换器(图2)。它

存储器和IO扩展实验,计算机组成原理

科技学院 课程设计实验报告 ( 2014--2015年度第一学期) 名称:计算机组成原理综合实验题目:存储器和I/O扩展实验 院系:信息工程系 班级: 学号: 学生姓名: 指导教师:李梅王晓霞 设计周数:一周 成绩: 日期:2015 年1 月

一、目的与要求 1. 内存储器部件实验 (1)熟悉ROM芯片和RAM芯片在功能和使用方法等方面的相同和差异之处;学习用编程器设备向EEPROM芯片内写入一批数据的过程和方法。 (2)理解并熟悉通过字、位扩展技术实现扩展存储器系统容量的方案; (3)了解静态存储器系统使用的各种控制信号之间正常的时序关系; (4)了解如何通过读、写存储器的指令实现对58C65 ROM芯片的读、写操作; (5)加深理解存储器部件在计算机整机系统中的作用。 2. I/O口扩展实验 学习串行口的正确设置和使用。 二、实验正文 1.主存储器实验内容 1.1实验的教学计算机的存储器部件设计(说明只读存储器的容量、随机读写器的容量,各选用了什么型号及规格的芯片、以及地址空间的分布) 在教学计算机存储器部件设计中,出于简化和容易实现的目的,选用静态存储器芯片实现内存储器的存储体,包括唯读存储区(ROM,存放监控程序等) 和随读写存储区(RAM)两部分,ROM存储区选用4片长度8位、容量8KB 的58C65芯片实现,RAM存储区选用2片长度8位、容量2KB的6116芯片 实现,每2个8位的芯片合成一组用于组成16位长度的内存字,6个芯片被分 成3组,其地址空间分配关系是:0-1777h用于第一组ROM,固化监控程序, 2000-2777h用于RAM,保存用户程序和用户数据,其高端的一些单元作为监 控程序的数据区,第二组ROM的地址范围可以由用户选择,主要用于完成扩 展内存容量(存储器的字、位扩展)的教学实验。 1.2扩展8K字的存储空间,需要多少片58C65芯片,58C65芯片进行读写时的特殊要求 要扩展8K字的存储空间,需要使用2片(每一片有8KB容量,即芯片内由8192个单元、每个单元由8个二进制位组成)存储器芯片实现。对 58C65 ROM芯片执行读操作时,需要保证正确的片选信号(/CE)为低点平, 使能控制信号(/OE)为低电平,读写命令信号(/WE)为高电平,读58C65 ROM 芯片的读出时间与读RAM芯片的读出时间相同,无特殊要求;对58C65 ROM 芯片执行写操作时,需要保证正确的片选信号(/CE)为低电平,使能控制信 号(/OE)为高电平,读写命令信号(/WE)为低电平,写58C65 ROM芯片的 维持时间要比写RAM芯片的操作时间长得多。为了防止对58C65 ROM芯片执 行误写操作,可通过把芯片的使能控制引脚(/OE)接地来保证,或者确保读 写命令信号(/WE)恒为高电平。 1.3在实验中思考为何能用E命令直接写58C65芯片的存储单元,而A命令则有时不正确;

触发器实验报告

. . . . .. . 实验报告 课程名称:数字电子技术基础实验 指导老师: 周箭 成绩:__________________ 实验名称:集成触发器应用 实验类型: 同组学生姓名:__邓江毅_____ 一、实验目的和要求(必填) 二、实验内容和原理(必填) 三、主要仪器设备(必填) 四、操作方法和实验步骤 五、实验数据记录和处理 六、实验结果与分析(必填) 七、讨论、心得 实验内容和原理 1、D →J-K 的转换实验 设计过程:J-K 触发器和D 触发器的次态方程如下: J-K 触发器:n n 1 +n Q Q J =Q K +, D 触发器:Qn+1=D 若将D 触发器转换为J-K 触发器,则有:n n Q Q J =D K +。 实验结果: J K Qn-1 Qn 功能 0 0 0 0 保持 1 1 0 1 0 0 置0 1 0 1 1 0 1 翻转 1 0 1 0 1 置1 1 1 (上:Qn ,下:CP ,J 为高电平时) 2、D 触发器转换为T ’触发器实验 设计过程:D 触发器和T ’触发器的次态方程如下: D 触发器:Q n+1= D , T ’触发器:Q n+1=!Q n 若将D 触发器转换为T ’触发器,则二者的次态方程须相等,因此有:D=!Qn 。 实验截图: 专业:电卓1501 姓名:卢倚平 学号:3150101215 日期:2017.6.01 地点:东三404

实验名称:集成触发器应用实验 姓名: 卢倚平 学号: 2 (上:Qn ,下:!Qn )CP 为1024Hz 的脉冲。 3、J-K →D 的转换实验。 ①设计过程: J-K 触发器:n n 1 +n Q Q J =Q K +, D 触发器:Qn+1=D 若将J-K 触发器转换为D 触发器,则二者的次态方程须相等,因此有:J=D ,K=!D 。 实验截图: (上:Qn ,下:CP ) (上:Qn ,下:D ) 4、J-K →T ′的转换实验。 设计过程: J-K 触发器:n n 1 +n Q Q J =Q K +, T ’触发器:Qn+1=!Qn 若将J-K 触发器转换为T ’触发器,则二者的次态方程须相等,因此有:J=K=1 实验截图:

数据库存储器与触发器实验报告

南昌航空大学实验报 二0 一七年5月3日 课程名称:数据库概论实验名称:存储器与触发器 班级: XX X 姓名:XXX 同组人: 指导教师评定:________________________________________ 签名:__________________ 一、实验环境 1. Windows2000或以上版本; 2. SQLServer2000 或2005。 二、实验目的 1. 掌握存储过程的创建,修改,使用,删除; 2. 掌握触发器的创建,修改,使用,删除。 三、实验步骤及参考源代码 1.创建过程代码: CREATEPROCEDURI_P_Proc( @ccna varchar (10), @cnochar (4) OUTPU,T@cna varchar (10) OUTPU,T@pnavarchar (20) OUTPU,T@numint OUTPUT

AS SELECT@cna=cna, @cno=cp. cno, @pna=pna, @num=num FROMcp , customer , paper WHEREcustomer . cno=cp. cno ANDpaper . pno=cp. pno ANDcna =@ccna; 6.执行存储过程C_P_Pro,实现对李涛,钱金浩等不同顾客的订阅信息查询 execute C_P_Proc @nam=e' 李涛' execute C_P_Proc @nam=e' 钱金浩' 7,删除存储过程C_P_Prcc DROPPROCEDURCE_P_PROC (4)在DingBao数据库中针对PAPER创建插入触发器TR_PAPER_I删除触发器TR_PAPER_D修改触发器TR_PAPER_J具体要求如下。 <1>对PAPER的插入触发器:插入报纸记录,单价为负值或为空时,设定为10 元。 CREATE TRIGGER TR_PAPER_I ON paper FOR INSERT AS DECLARE @ippr FLOAT; declare @ipno int;

数电实验触发器及其应用

数电实验触发器及其应用 数字电子技术实验报告 实验三: 触发器及其应用 一、实验目的: 1、熟悉基本RS触发器,D触发器的功能测试。 2、了解触发器的两种触发方式(脉冲电平触发和脉冲边沿触发)及触发特点 3、熟悉触发器的实际应用。 二、实验设备: 1 、数字电路实验箱; 2、数字双综示波器; 3、指示灯; 4、74LS00、74LS74。 三、实验原理: 1、触发器是一个具有记忆功能的二进制信息存储器件,是构成多种时序 电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即“0”和“ 1 ”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。触发器有集成触发器和门电路(主要是“与非门” )组成的触发器。 按其功能可分为有RS触发器、JK触发器、D触发器、T功能等触发器。触发方式有电平触发和边沿触发两种。 2、基本RS触发器是最基本的触发器,可由两个与非门交叉耦合构成。 基本RS触发器具有置“ 0”、置“ 1”和“保持”三种功能。基本RS触发器

也可以用二个“或非门”组成,此时为高电平触发有效。 3、D触发器在CP的前沿发生翻转,触发器的次态取决于CP脉冲上升沿n+1来到之前D端的状态,即Q = D。因此,它具有置“ 0”和“T两种功能。由于在CP=1期间电路具有阻塞作用,在CP=1期间,D端数据结构变RS化,不会影响触发器的输出状态。和分别是置“ 0”端和置“ 1” DD 端,不需要强迫置“ 0”和置“ 1”时,都应是高电平。74LS74(CC4013, 74LS74(CC4042均为上升沿触发器。以下为74LS74的引脚图和逻辑图。 馬LD 1CP 1云IQ LQ GM) 四、实验原理图和实验结果: 设计实验: 1、一个水塔液位显示控制示意图,虚线表示水位。传感器A、B被水浸沿时

实验五_存储器设计

计算机组成原理 实验五《存储器设计》 实验报告 姓名:吴速碘黄紫微 学号:13052053 13052067 班级:计算机二班 日期2015、5、25

实验五存储器设计 一、实验目的 1、掌握RAM和ROM的Verilog语言描述方法; 2、学习用宏模块的方法定制RAM和ROM。 二、实验任务 1、设计并实现一个128*16 的单端口的RAM; 2、设计并实现一个128*16的ROM; 3、设计并实现一个双端口的128*16的RAM 4、设计并实现一个16*32的FIFO。 5、设计并实现正弦信号发生器,见“正弦信号发生器实验指南”。 三、实验步骤 1 编写Verilog代码(见附页) 2功能仿真 进行分析与综合,排除语法上的错误 建立波形仿真文件,输入激励 生成功能仿真网表 进行功能仿真,观察输出结果 3选择器件 DE2_70开发板的使用者请选择EP2C70F896C6 4绑定管脚 5 下载验证 DE2_70开发板的下载:使用USB-Blaster进行下载 四、实验内容 五、实验思考题 1、分析存储器采用三态输出的原因是什么? 存储器的输出端是连接在数据总线上的。数据总线相当于一条车流频繁的大马路,必须在绿灯条件下,车辆才能进入这条大马路,否则要撞车发生交通事故。同 理,存储器中的数据是不能随意传送到数据总线上的。例如,若数据总线上的数 据是“1”(高电平5V),存储器中的数据是“0”(低电平0V),两种数据若碰到一 起就会发生短路而损坏单片机。因此,存储器输出端口不仅能呈现“l”和“0”两 种状态,还应具有第三种状态“高阻"态。呈“高阻"态时,输出端口相当于断开,对数据总线不起作用,此时数据总线可被其他器件占用。当其他器件呈“高阻”态 时,存储器在片选允许和输出允许的条件下,才能将自己的数据输出到数据总线 上。 2、单端口和双端口的区别是什么? 单端口ram是ram的读写只有一个端口,同时只能读或者只能写。 双端口ram是ram读端口和写端口分开,一个端口能读,另一个端口可以同时写。 3、什么情况下考虑采用双端口存储器?