实验报告

课程名称:EDA技术与FPGA应用设计课设题目:2位十进制计数器

实验地点:信息学院楼CPLD实验室专业班级:

学号:

学生姓名:

指导教师:张文爱

2016年4月1日

实验二2位十进制计数器

一、实验目的

1.熟悉ispDesignEXPERT System、QuartusII的原理图设计流程的全过程。

2.学习简单时序电路的设计方法。

3.学习EDA设计的仿真和硬件测试方法。

二、实验原理

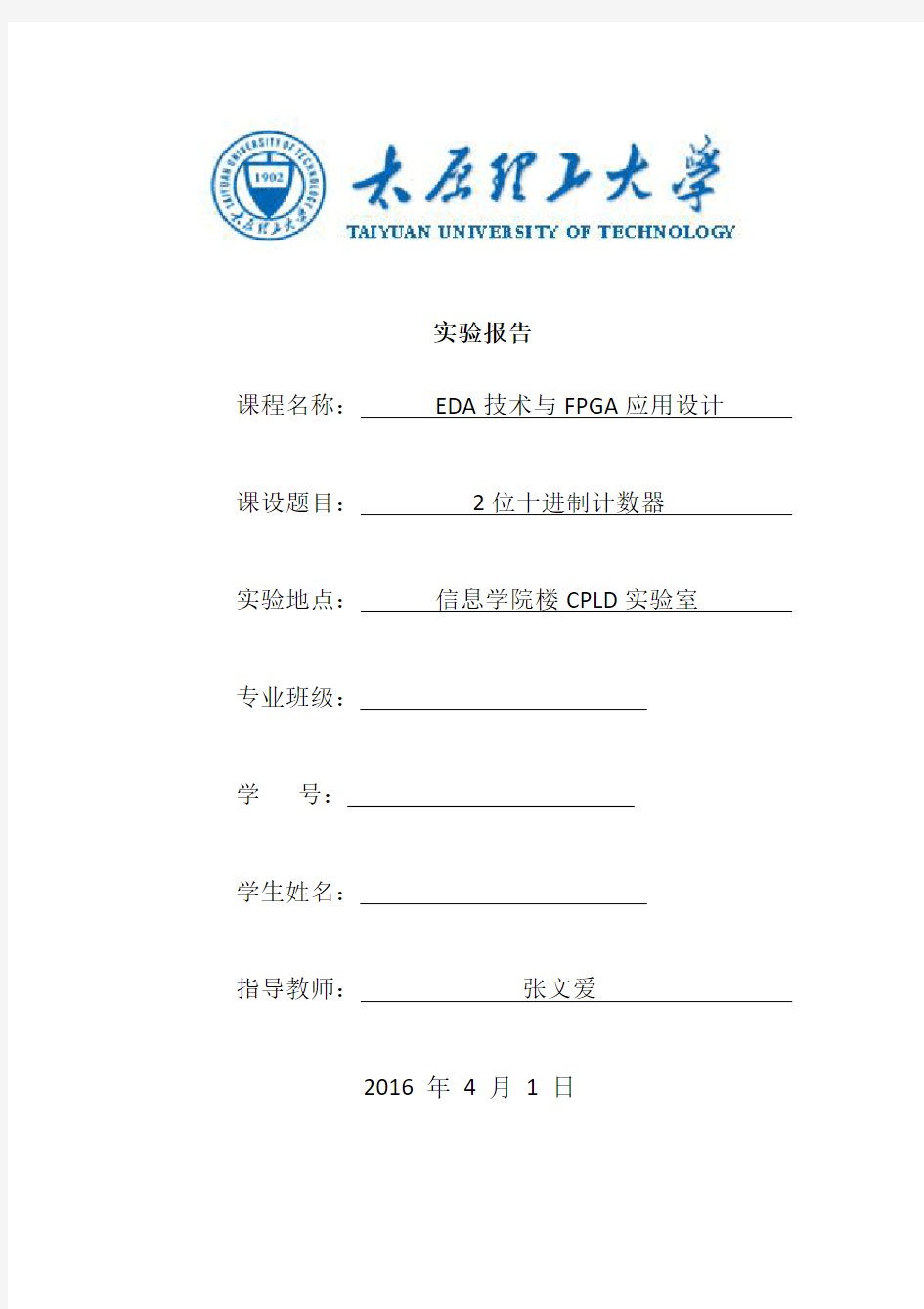

2位十进制计数器参考原理图如图1所示,也可以采用其他元件实现。

图1.用74LS390设计一个有时钟使能的2位十进制计数器

三、实验任务

(1)设计2位十进制计数器电路。

(2)在EDA环境中输入原理图。

(3)对计数器进行仿真分析、引脚锁定、硬件测试。

四、实验步骤

1、设计电路原理图

设计含有时钟使能及进位扩展输出的十进制计数器。可以选用双十进制计数器74LS390或者十进制计数器74LS160和其他一些辅助元件来完成。

2、计数器电路的实现。

绘制过程中应特别注意图形设计规则中信号标号和总线的表达方式。若将一根细线变成一粗线显示的总线,可以先单机使其变红,再选Option选项中的Line Style;若

在某线上加信号标号,也应该点击该线某处使其变成红色,然后键入标号名称,标有相同标号的线段可视为连接线段,不必直接连接。总线可以以标号方式进行连接。

3、编程测试。

五、实验结果

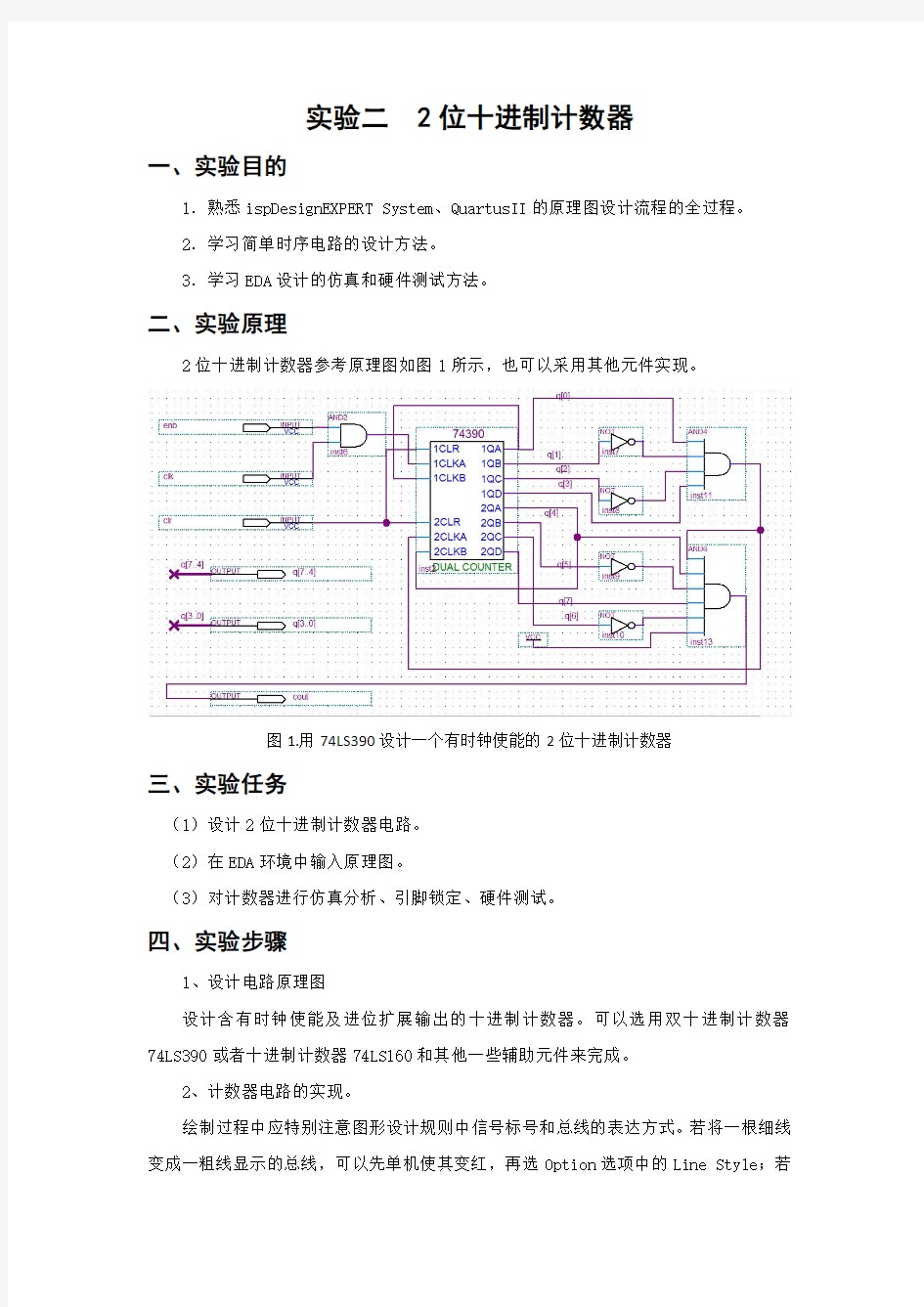

图2.用74LS390设计一个有时钟使能的2位十进制计数器

六、实验感想

通过本次实验学会了简单时序电路的设计方法。学会了使用QuartusII软件调用元器件库进行原理图设计的方法和设计流程。这次实验让我学会了用FPGA设计电路并且学会了FPGA的设计过程和实现方法。提高了动手能力,加深了对所学知识的理解。这次EDA实验,提高了动手能力,加深了对所学知识的理解。

4位全加器实验报告

四位全加器 11微电子黄跃21 【实验目的】 采用modelsim集成开发环境,利用verilog硬件描述语言中行为描述模式、结构描述模式或数据流描述模式设计四位进位加法器。 【实验内容】 加法器是数字系统中的基本逻辑器件。多位加法器的构成有两种方式:并行进位和串行进位方式。并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。 实现多位二进制数相加的电路称为加法器,它能解决二进制中1+1=10的功能(当然还有 0+0、0+1、1+0). 【实验原理】

表2 全加器逻辑功能真值表 图4 全加器方框图 图5 全加器原理图 多位全加器连接可以是逐位进位,也可以是超前进位。逐位进位也称串行进位,其逻辑电路简单,但速度也较低。 四位全加器 如图9所示,四位全加器是由半加器和一位全加器组建而成: 图9 四位全加器原理图 【实验步骤】 (1)建立新工程项目: 打开modelsim软件,进入集成开发环境,点击File→New project建立一

个工程项目adder_4bit。 建立文本编辑文件: 点击File→New在该项目下新建Verilog源程序文件 并且输入源程序。 (2)编译和仿真工程项目: 在verilog主页面下,选择Compile— Compile All或点击工具栏上的按钮启动编译,直到project出现status栏全勾,即可进行仿真。 选择simulate - start simulate或点击工具栏上的按钮开始仿真,在跳出来的 start simulate框中选择work-test_adder_4bit测试模块,同时撤销Enable Optimisim前的勾,之后选择ok。 在sim-default框内右击选择test_adder_4bit,选择Add Wave,然后选择simulate-run-runall,观察波形,得出结论,仿真结束。 四位全加器 1、原理图设计 如图9所示,四位全加器是由半加器和一位全加器组建而成: 图9 四位全加器原理图 【仿真和测试结果】 下图为四位全加器的仿真图:

java实验报告完整版

实验报告 (计算机与信息工程学院实验中心) 学期: 2014-2015 课程名称:《Java程序设计实验》 班级:信息1202 姓名:方逸梅 学号: 31 指导老师:费玉莲

《Java程序设计》 独立实验教学安排 一、实验的教学方式、安排及实验环境 (一)教学方式 对照本课程的实验教材,实验一至实验十一,由教师提示实验原理、方法、步骤等内容,在教师的指导下,学生独立完成程序设计及调试工作。实验十二的内容由学生自行设计完成。 (二)教学安排 学时数:30课时 学时安排:每次实验3学时,从学期第五周开始,共十次上机实验。 (三)实验环境 实验环境为JDK 。 (四)具体安排 地点:信息大楼实验室。 辅导:每个班次一名辅导老师,原则上由任课老师担任。 登记:实验完成,由辅导老师登记实验纪录。 学生:实验做完,完成实验报告内容,并在学期末上交实验册。 老师:批改实验,成绩与平时成绩一起占期末的30%。 二、实验的具体内容和要求 见实验报告。

浙江工商大学 计算机与信息工程学院实验报告(1)日期:地点:成绩: ━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━ 实验目的、实验原理和内容: 一、实验目的:熟悉Java开发环境及简单程序Java设计。 二、实验原理:SDK 的下载与安装,设置环境变量,安装java 虚拟机,使用Eclipse,编译Java 源程序,运行Java 程序。 三、实验内容及要求: 1.下载、安装并设置Java SDK 软件包。 2.熟悉Eclipse 编辑软件。 3.掌握运行Java 程序的步骤。 4.分别编写Application和Applet程序,显示字符串”Hello Java!欢迎使用!”。 要求:请同学把预备知识、步骤、程序框图、调试好的程序及存在的问题写在下面(不够可以附页)。 程序一 public class hello { public static void main(String[] args) { for(int i=0;i<=4;i++) { "Hello java! 欢迎使用!"); } }

太原理工大学计算机网络实验报告

本科实验报告 课程名称:计算机网络B 实验地点:行勉楼 专业班级:学号 学生姓名: 指导教师: 实验成绩: 2016年 6 月 14 日

实验3 VLAN基本配置 一、实验目的 掌握交换机上创建VLAN、分配静态VLAN成员的方法。 二、实验任务 1、配置两个VLAN:VLAN 2和VLAN 3并为其分配静态成员。 2、测试VLAN分配结果。 三、实验设备 Cisco交换机一台,工作站PC四台,直连网线四条,控制台电缆一条。 四、拓扑结构 五、实验结果 PC0到PC1 想通 PC0到PC2 不通,不在相同VLAN PC2到PC3 不通,网段不同。 Switch#sh run Building configuration... Current configuration : 1127 bytes ! version 12.1 no service timestamps log datetime msec no service timestamps debug datetime msec no service password-encryption ! hostname Switch ! ! spanning-tree mode pvst ! interface FastEthernet0/1

! interface FastEthernet0/2 switchport access vlan 2 ! interface FastEthernet0/3 switchport access vlan 2 ! interface FastEthernet0/4 switchport access vlan 2 ! interface FastEthernet0/5 switchport access vlan 3 ! interface FastEthernet0/6 switchport access vlan 3 ! interface FastEthernet0/7 switchport access vlan 3 ! 六、实验心得 输入容易出现错误。重复输入次数多。

实验一四位串行进位加法器的设计实验报告

实验一四位串行进位加法器的设计 一、实验目的 1.理解一位全加器的工作原理 2.掌握串行进位加法器的逻辑原理 3.进一步熟悉Quartus软件的使用,了解设计的全过程, 二、实验内容 1.采用VHDL语言设计四位串行进位的加法器 2.采用画原理图的方法设计四位串行进位加法器 三、实验步骤 1、使用VHDL语言设计 1.打开File—>New Project Wizard输入文件名adder4保存在D盘内,打开File—>New—>VHDL File,从模版中选择库的说明,use语句的说明,实体的说明,结构体的说明,编写VHDL代码,然后保存、编译。打开File—>New—>Other File—>Vector Waveform File,查找引脚,从Edit中选择End Time 输入40、ns 保存。从Assignments—>Settings—>Simulator Settings —>Functional 然后Processing—>Generate Functional Simnlation Netlist —>确定。选择Start Simulation保存最后的波形图,打开File —>close关闭工程。 底层文件: LIBRARY ieee;

USE fadder IS PORT ( a, b,cin : IN STD_LOGIC; s, co : OUT STD_LOGIC ); END fadder; ARCHITECTURE arc1 OF fadder IS BEGIN s<=a xor b xor cin; co<=((a xor b)and cin)or(a and b); END arc1; 顶层文件: LIBRARY ieee; USE adder4 IS PORT ( c0: IN STD_LOGIC; a,b : IN STD_LOGIC_VECTOR(3 DOWNTO 0); s : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); c4 : OUT STD_LOGIC );

大学物理实验报告书(共6篇)

篇一:大学物理实验报告1 图片已关闭显示,点此查看 学生实验报告 学院:软件与通信工程学院课程名称:大学物理实验专业班级:通信工程111班姓名:陈益迪学号:0113489 学生实验报告 图片已关闭显示,点此查看 一、实验综述 1、实验目的及要求 1.了解游标卡尺、螺旋测微器的构造,掌握它们的原理,正确读数和使用方法。 2.学会直接测量、间接测量的不确定度的计算与数据处理。 3.学会物理天平的使用。 4.掌握测定固体密度的方法。 2 、实验仪器、设备或软件 1 50分度游标卡尺准确度=0.02mm 最大误差限△仪=±0.02mm 2 螺旋测微器准确度=0.01mm 最大误差△仪=±0.005mm 修正值=0.018mm 3 物理天平 tw-0.5 t天平感度0.02g 最大称量 500g △仪=±0.02g 估读到 0.01g 二、实验过程(实验步骤、记录、数据、分析) 1、实验内容与步骤 1、用游标卡尺测量圆环体的内外径直径和高各6次; 2、用螺旋测微器测钢线的直径7次; 3、用液体静力称衡法测石蜡的密度; 2、实验数据记录表 (1)测圆环体体积 图片已关闭显示,点此查看 (2)测钢丝直径 仪器名称:螺旋测微器(千分尺)准确度=0.01mm估读到0.001mm 图片已关闭显示,点此查看 图片已关闭显示,点此查看 测石蜡的密度 仪器名称:物理天平tw—0.5天平感量: 0.02 g 最大称量500 g 3、数据处理、分析 (1)、计算圆环体的体积 1直接量外径d的a类不确定度sd ,sd=○ sd=0.0161mm=0.02mm 2直接量外径d的b类不确定度u○ d. ud,= ud=0.0155mm=0.02mm 3直接量外径d的合成不确定度σσ○ σd=0.0223mm=0.2mm 4直接量外径d科学测量结果○ d=(21.19±0.02)mm d = 5直接量内径d的a类不确定度s○

加法器实验报告文档2篇

加法器实验报告文档2篇 Adder experiment report document 编订:JinTai College

加法器实验报告文档2篇 小泰温馨提示:实验报告是把实验的目的、方法、过程、结果等记录下来,经过整理,写成的书面汇报。本文档根据实验报告内容要求展开说明,具有实践指导意义,便于学习和使用,本文下载后内容可随意修改调整及打印。 本文简要目录如下:【下载该文档后使用Word打开,按住键盘Ctrl键且鼠标单击目录内容即可跳转到对应篇章】 1、篇章1:加法器实验报告文档 2、篇章2:加法器的基本原理实验报告文档 篇章1:加法器实验报告文档 【实验名称】 【目的与要求】 1.掌握1位全加器的设计 2.学会1位加法器的扩展【实验内容】 1.设计1位全加器

2.将1位全加器扩展为4位全加器 3.使4位的全加器能做加减法运算 【操作步骤】 1.1位全加器的设计 (1)写出1位全加器的真值表 (2)根据真值表写出表达式并化简 (3)画出逻辑电路 (4)用quartusII进行功能仿真,检验逻辑电路是否正确,将仿真波形截图并粘贴于此 (5)如果电路设计正确,将该电路进行封装以用于下一个环节 2.将1位全加器扩展为4位全加器 (1)用1位全加器扩展为4位的全加器,画出电路图 (2)分别用两个4位补码的正数和负数验证加法器的正确性(注意这两 个数之和必须在4位补码的数的范围内,这两个数包括符号在内共4位),用quartusII进行功能仿真并对仿真结果进行截图。

3.将4位的全加器改进为可进行4位加法和减法的运算器 (1)在4位加法器的基础上,对电路进行修改,使该电路不仅能进行加 法运算而且还能进行减法运算。画出该电路 (2)分别用两个4位补码的正数和负数验证该电路的正确性(注意两个 数之和必须在4位补码的数的范围内),用quartusII 进行功能仿真并对仿真结果进行截图。 【附录】 篇章2:加法器的基本原理实验报告文档【按住Ctrl键点此返回目录】 一、实验目的 1、了解加法器的基本原理。掌握组合逻辑电路在Quartus Ⅱ中的图形输入方法及文本输入方法。 2、学习和掌握半加器、全加器的工作和设计原理

化学实验报告完整版

化学实验报告 HUA system office room 【HUA16H-TTMS2A-HUAS8Q8-HUAH1688】

化学实验报告 化学是一门以实验为基础的学科。化学上的许多理论和定律都是从实验中发现归纳出来的。同时,化学理论的应用、评价也有赖于实验的探索和检验。虽然到了近代乃至现代,化学的飞速进步已经产生了各种新的研究方法,但是,实验方法仍然是化学不可缺少的研究手段。新课程改革将科学探究作为突破口,科学探究不但是一种重要的学习方式,同时也是中学化学课程的重要内容,它对发展学生的科学素养具有不可替代的作用。而化学实验是科学探究的重要形式。 用化学实验的方法学习化学,既符合化学的学科特点也符合学生学习化学的认识特点,是化学教学实施素质教育的基本手段。新课程标准提倡学生独立进行或合作开展化学实验研究。通过化学实验能激发学生的学习兴趣,帮助学生通过使用探究形成化学概念、理解化学基础理论、掌握化学知识和技能,培养学生的科学态度和价值观,帮助学生发展思维能力和训练实验技能,从而达到全面提高学生的科学素养的目的。 一、对新课程标准下的中学化学实验的认识 《普通高中化学课程标准》明确了高中化学课程的基本理念:立足于学生适应现代生活和未来发展的需要,着眼于提高21世纪公民的科学素养,构建“知识与技能”、“过程与方法”、“情感态度与价值观”相融合的高中化学课程目标体系。“知识与技能”即过去的“双基”;“过程与方法”是让学生掌握学习的方法,学会学习;“情感态度与价值观”是人文关怀的体现。所以新的课程理念的核心是“让学生在知识探索的过程中,在知识、学法、人文等方面得到发展。”其中第5条特别强调:“通过以化学实验为主的多种探究活动,使学生体验科学研究的过程,激发学习化学的兴趣,强化科学探究的意识,促进学习方式的转变,培养学生的创新精神和实践能力。”[1]高中化学课程由2个必修模

太原理工大学web实验报告资料

本科实验报告 课程名称:Web开发实用技术基础 实验项目:HTML语言 网页程序设计Javascript Request与Response对象的应用 Application与Session对象的应用 实验地点:实验室211 专业班级:学号: 学生姓名: 指导教师: 2015年11月5日

学院名称学号实验成绩 学生姓名专业班级实验日期 课程名称Web开发实用技术基础实验题目HTML语言 一.实验目的和要求 1.掌握常用的HTML语言标记; 2.利用文本编辑器建立HTML文档,制作简单网页。 3.独立完成实验。 4.书写实验报告书。 二.实验内容 1.在文本编辑器“记事本”中输入如下的HTML代码程序,以文件名sy1.html保存,并在浏览器中运行。(请仔细阅读下列程序语句,理解每条语句的作用) 源程序清单如下:

Example

A simple HTML document

Welcome to the world of HTML This is a simple HTML document.It is to give you an outline of how to write HTML file and how the

markup tags work in the

HTML file Following is three chapters

Following is items of the chapter two | item | content |

计组-加法器实验报告

半加器、全加器、串行进位加法器以及超前进位加法器 一、实验原理 1.一位半加器 A和B异或产生和Sum,与产生进位C 2.一位全加器 将一位半加器集成封装为halfadder元件,使用两个半加器构成一位的全加器 3.4位串行进位加法器 将一位全加器集成封装为Fulladder元件,使用四个构成串行进位加法器

4.超前进位加法器(4位) ⑴AddBlock 产生并行进位链中的ti(即Cthis)和di(即Cpass),以及本位结果Sum ⑵进位链(Cmaker) 四位一组并行进位链,假设与或非门的级延迟时间为1.5ty,与非门的延迟时间为1ty,在di和ti产生之后,只需2.5ty就可产生所有全部进位

⑶超前进位加法器 将以上二者结合起来即可完成,A和B各位作为各个AddBlock的输入,低一位的进位Ci-1作为本位AddBlock的C-1的输入。各个AddBlock输出的C_this和C_pass作为对应的Cmaker的thisi和passi的输入。

二、实验器材 QuartusII仿真软件,实验箱 三、实验结果 1.串行进位加法器结果 2.超前进位加法器结果

四、实验结果分析 1.实验仿真结果显示串行加法器比超前进位加法器快,部分原因应该是电路结构优化 不到位。另外由于计算的位数比较少,超前进位加法链结构较复杂,所以优势没体现出来,反倒运作的更慢一点。当位数增加的时候,超前进位加法器会比串行的更快。 2.波形稳定之前出现上下波动,应该与“竞争冒险”出现的情况类似,门的延迟和路径 的不同导致了信号变化时到达的时间有先有后,因此在最终结果形成前出现了脉冲尖峰和低谷;另外也可能部分原因由于电路结构优化的不到位所致

(完整版)初中生物实验报告单.docx

实验报告单 实验时间年月日(星期)班级学生姓名 实验内容练习使用显微镜 说出显微镜的主要结构的名称和用途。 实验目的练习使用显微镜,学会规范操作显微镜。 尝试使用低倍镜观察到清晰的物像。 实验器材显微镜、写有“上”字的玻片、擦镜纸、纱布。 实验报告单实验时间年月日(星期)班级学 实验内容观察人和动物细胞的基本 学会制作人口腔上皮细胞临时装片。 实验目的用显微镜观察动物细胞的形态结构。 初步学会画细胞结构图。 显微镜、载玻片、盖玻片、0.9%生理盐水、碘液、 实验器材 吸水纸、其他动物细胞的永久装片。 实验步骤 1、取镜安放实 2、对光 3、放置玻片验 标本 步 4、观察 骤 实验步骤 5、收放 结 论 实验过程讨论分析 取显微镜时,左手握 显微镜是贵重仪器,双手取镜是为了。 住,右手托 安放显微镜略偏左的目的是: 住。安放显微镜应略 。 偏。 转动转换器,使低倍物镜对准当外界光源暗时,应选用光圈对准通光孔,同时选 孔。用反光镜。 把要观察的玻片放在 尽量使要观察的标本正对通光孔中央,这样物像容易 上,尽量使要观察的标本正对 在中找到。 中央。 转动粗准焦螺旋,使镜筒缓缓 眼睛应从侧面注视的目的是:避免 。 降,直至为 镜筒上升切忌太快,因为只有在 止,眼睛应从侧面注 位置上,物象才清晰。若镜筒上升太快,极易错过 视。 焦距。 时针转动粗准焦螺旋, 要将视野右下方的物像移到视野中央,则推移装片的 使镜简缓缓上升直到看清物像为 方向是。 止。再转动 “上”字装片在显微镜下呈图像。说明显微镜成像 准焦螺旋,使物像更清晰。 是。 实验过程讨论分析 实验后,把显微镜擦拭干净。 转动转换器使两个物镜。镜 筒降至处,反光镜放在 实 验 成 绩 实验步骤实验过程 为什 ①擦干净载玻片和盖玻片。 ②在载玻片中央,滴一滴 碎屑 实浓度一般是。 抹要均 1、制作人口腔 ③用消毒牙签的一端在口腔 侧壁轻刮几下。 验上皮细胞临时装避免 片。 ④把牙签上附有碎屑的一端, 放在载玻片的水滴中涂抹几下。 步⑤盖上盖玻片。 气泡与 ⑥在盖玻片一侧加在 骤 另一侧用吸水纸吸。 2、是微镜观察 人口腔上皮细胞 实验步骤实验过程讨论分 按生物绘图要求,画出人体口腔上皮细胞的结构 结图,并注明各部分结构的名称。实 验 成 论绩 指导教师: _________________实验教 指导教师: _________________实验教师:_______________

2014太原理工大学C++实验报告

本科实验报告 课程名称:C++面向对象程序设计 实验项目:C++语言编程 实验地点:明向校区 专业班级:软件1431 学号:201400XXXX 学生姓名:白建兴 指导教师:崔晓红 2015年5月10日

1.运行例题程序: #include using namespace std; void fn1(int z=5); int x=1,y=2; int main() { cout<<"Begin. . ."<>p[i]; if(p[i]>0) plus++; else if(p[i]!=0) minus++; } cout<<"正数的个数:"<实验一 4位全加器的设计

实验一4位全加器的设计 一、实验目的: 1 熟悉QuartusⅡ与ModelSim的使用; 2 学会使用文本输入方式和原理图输入方式进行工程设计; 3 分别使用数据流、行为和结构化描述方法进行四位全加器的设计; 4 理解RTL视图和Technology Map视图的区别; 5 掌握简单的testbench文件的编写。 二、实验原理: 一个4位全加器可以由4个一位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的进位输入信号cin相接。 三、实验内容: 1.QuartusII软件的熟悉 熟悉QuartusⅡ环境下原理图的设计方法和流程,可参考课本第4章的内容,重点掌握层次化的设计方法。 2.设计1位全加器原理图 设计的原理图如下所示:

VHDL源程序如下(行为描述):-- Quartus II VHDL Template -- Unsigned Adder library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity f_add is port ( a : in std_logic; b : in std_logic; ci : in std_logic; y : out std_logic; co : out std_logic ); end entity; architecture rtl of f_add is begin (co,y)<=('0',a)+('0',b)+('0',ci); end rtl;

FPGA一位全加器设计实验报告

题目:1位全加器的设计 一.实验目的 1.熟悉QUARTUSII软件的使用; 2.熟悉实验硬件平台的使用; 3.掌握利用层次结构描述法设计电路。 二.实验原理 由于一位全加器可由两个一位半加器与一个或门构成,首先设计半加器电路,将其打包为半加器模块;然后在顶层调用半加器模块组成全加器电路;最后将全加器电路编译下载到实验箱,其中ain,bin,cin信号可采用实 验箱上SW0,SW1,SW2键作为输入,并将输 入的信号连接到红色LED管 LEDR0,LEDR1,LEDR2上便于观察,sum,cout 信号采用绿色发光二极管LEDG0,LEDG1来 显示。 三.实验步骤 1.在QUARTUSII软件下创建一工程,工程名为full_adder,芯片名为EP2C35F672C6; 2.新建Verilog语言文件,输入如下半加器Verilog语言源程序; module half_adder(a,b,s,co); input a,b; output s,co; wire s,co; assign co=a & b; assign s=a ^ b; Endmodule 3.保存半加器程序为,进行功能仿真、时序仿真,验证设计的正确性。 其初始值、功能仿真波形和时序仿真波形分别如下所示

4.选择菜单File→Create/Update→Create Symbol Files for current file,创建半加器模块; 5.新建一原理图文件,在原理图中调用半加器、或门模块和输入,输出引脚,按照图1所示连接电路。并将输入ain,bin,cin连接到FPGA的输出端,便于观察。完成后另保存full_adder。 电路图如下 6.对设计进行全编译,锁定引脚,然后分别进行功能与时序仿真,验证全加器的逻辑功能。其初始值、功能仿真波形和时序仿真波形分别如下所示

八位加法器设计实验报告

实验四:8位加法器设计实验 1.实验目的:熟悉利用quartus原理图输入方法设计简单组合电路,掌握层次化设计方法。 2.实验原理:一个八位加法器可以由八个全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的最低进位输入信号cin相接。 3.实验任务:完成半加器,全加器,八位加法器设计,使用例化语句,并将其设计成一个原件符号入库,做好程序设计,编译,程序仿真。 1)编译成功的半加器程序: module h_adder(a,b,so,co); input a,b; output so,co; assign so=a^b; assign co=a&b; endmodule 2)编译成功的全加器程序: module f_adder(ain,bin,cin,cout,sum); output cout,sum;input ain,bin,cin; wire net1,net2,net3; h_adder u1(ain,bin,net1,net2); h_adder u2(.a(net1),.so(sum),.b(cin),.co(net3));

or u3(cout,net2,net3); endmodule 3)编译成功的八位加法器程序: module f_adder8(ain,bin,cin,cout,sum); output [7:0]sum; output cout;input [7:0]ain,bin;input cin; wire cout0, cout1, cout2 ,cout3, cout4,cout5,cout6; f_adder u0(.ain(ain[0]),.bin(bin[0]),.cin(cin),.sum(sum[0]) ,.cout(cout0)); f_adder u1(.ain(ain[1]),.bin(bin[1]),.cin(cout0),.sum(sum[1 ]),.cout(cout1)); f_adder u2(.ain(ain[2]),.bin(bin[2]),.cin(cout1),.sum(sum[2 ]),.cout(cout2)); f_adder u3(.ain(ain[3]),.bin(bin[3]),.cin(cout2),.sum(sum[3 ]),.cout(cout3)); f_adder u4(.ain(ain[4]),.bin(bin[4]),.cin(cout3),.sum(sum[4

4位全加器实验报告.doc

四位全加器 11微电子黄跃1117426021 【实验目的】 采用modelsim集成开发环境,利用verilog硬件描述语言中行为描述模式、结构描述模式或数据流描述模式设计四位进位加法器。 【实验内容】 加法器是数字系统中的基本逻辑器件。多位加法器的构成有两种方式:并行进位和串行进位方式。并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。 实现多位二进制数相加的电路称为加法器,它能解决二进制中1+1=10的功能(当然还有 0+0、0+1、1+0). 【实验原理】 全加器 除本位两个数相加外,还要加上从低位来的进位数,称为全加器。图4为全 加器的方框图。图5全加器原理图。被加数A i 、加数B i 从低位向本位进位C i-1 作 为电路的输入,全加和S i 与向高位的进位C i 作为电路的输出。能实现全加运算 功能的电路称为全加电路。全加器的逻辑功能真值表如表2中所列。 信号输入端信号输出端 A i B i C i S i C i 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1

表2 全加器逻辑功能真值表 图4 全加器方框图 图5 全加器原理图 多位全加器连接可以是逐位进位,也可以是超前进位。逐位进位也称串行进位,其逻辑电路简单,但速度也较低。 四位全加器 如图9所示,四位全加器是由半加器和一位全加器组建而成: 图9 四位全加器原理图 【实验步骤】 (1)建立新工程项目: 打开modelsim软件,进入集成开发环境,点击File→New project建立一

大学计算机实验报告范例(完整版)

报告编号:YT-FS-1587-65 大学计算机实验报告范例 (完整版) After Completing The T ask According To The Original Plan, A Report Will Be Formed T o Reflect The Basic Situation Encountered, Reveal The Existing Problems And Put Forward Future Ideas. 互惠互利共同繁荣 Mutual Benefit And Common Prosperity

大学计算机实验报告范例(完整版) 备注:该报告书文本主要按照原定计划完成任务后形成报告,并反映遇到的基本情况、实际取得的成功和过程中取得的经验教训、揭露存在的问题以及提出今后设想。文档可根据实际情况进行修改和使用。 一、实验题目 文件和文件夹的管理 二、实验目的 1.熟悉Windows XP的文件系统。 2.掌握资源管理器的使用方法。 3.熟练掌握在Windows XP资源管理器下,对文件 (夹)的选择、新建、移动、复制、删除、重命名的 操作方法。 三、实验内容 1.启动资源管理器并利用资源管理器浏览文件。 2.在D盘创建文件夹 3.在所创建文件夹中创建Word文件。 4.对所创建文件或文件夹执行复制、移动、重命

名、删除、恢复、创建快捷方式及设置共享等操作。 四、实验步骤 (一)文件与文件夹管理 1.展开与折叠文件夹。右击开始,打开资源管理器,在左窗格中点击“+”展开,点击“—”折叠 2.改变文件显示方式。打开资源管理器/查看,选择缩略、列表,排列图标等 班/王帅、王鹏 3.建立树状目录。在D盘空白处右击,选择新建/文件夹,输入经济贸易学院,依次在新建文件夹中建立经济类1103 4..创建Word并保存。打开开始/程序/word,输入内容。选择文件/另存为,查找D盘/经济贸易学院/1103班/王帅,单击保存 5.复制、移动文件夹 6.重命名、删除、恢复。右击文件夹,选择重命名,输入新名字;选择删除,删除文件 7.创建文件的快捷方式。右击王帅文件夹,选择

太原理工大学数值计算方法实验报告

本科实验报告 课程名称:计算机数值方法 实验项目:方程求根、线性方程组的直接解法、线性方程组的迭代解法、代数插值和最小二乘拟合多项式 实验地点:行勉楼 专业班级:******** 学号:********* 学生:******** 指导教师:誌,冬华 2016年4 月8 日

y = x*x*x + 4 * x*x - 10; return y; } float Calculate(float a,float b) { c = (a + b) / 2; n++; if (GetY(c) == 0 || ((b - a) / 2) < 0.000005) { cout << c <<"为方程的解"<< endl; return 0; } if (GetY(a)*GetY(c) < 0) { return Calculate(a,c); } if (GetY(c)*GetY(b)< 0) { return Calculate(c,b); } } }; int main() { cout << "方程组为:f(x)=x^3+4x^2-10=0" << endl; float a, b; Text text; text.Getab(); a = text.a; b = text.b; text.Calculate(a, b); return 0; } 2.割线法: // 方程求根(割线法).cpp : 定义控制台应用程序的入口点。// #include "stdafx.h" #include"iostream"

心得体会 使用不同的方法,可以不同程度的求得方程的解,通过二分法计算的程序实现更加了解二分法的特点,二分法过程简单,程序容易实现,但该方法收敛比较慢一般用于求根的初始近似值,不同的方法速度不同。面对一个复杂的问题,要学会简化处理步骤,分步骤一点一点的循序处理,只有这样,才能高效的解决一个复杂问题。

java实验报告完整版

实验报告 (计算机与信息工程学院实验中心) 学期: 2014-2015 课程名称: 《Java程序设计实验》 班级: 信息1202 姓名: 方逸梅 学号: 1212100231 指导老师: 费玉莲 《Java程序设计》 独立实验教学安排 一、实验的教学方式、安排及实验环境 (一)教学方式 对照本课程的实验教材,实验一至实验十一,由教师提示实验原理、方法、步骤等内容,在教师的指导下,学生独立完成程序设计及调试工作。实验十二的内容由学生自行设计完成。 (二)教学安排 学时数:30课时 学时安排:每次实验3学时,从学期第五周开始,共十次上机实验。 (三)实验环境 实验环境为JDK 1、6。

(四)具体安排 地点:信息大楼实验室。 辅导:每个班次一名辅导老师,原则上由任课老师担任。 登记:实验完成,由辅导老师登记实验纪录。 学生:实验做完,完成实验报告内容,并在学期末上交实验册。 老师:批改实验,成绩与平时成绩一起占期末的30%。 二、实验的具体内容与要求 见实验报告。

浙江工商大学 计算机与信息工程学院实验报告(1)日期:地点:成绩: ━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━实验目的、实验原理与内容: 一、实验目的:熟悉Java开发环境及简单程序Java设计。 二、实验原理:SDK 的下载与安装,设置环境变量,安装java 虚拟机,使用Eclipse,编译Java 源程序,运行Java 程序。 三、实验内容及要求: 1. 下载、安装并设置Java SDK 软件包。 2. 熟悉Eclipse编辑软件。 3.掌握运行Java 程序的步骤。 4.分别编写Application与Applet程序,显示字符串”Hello Java!欢迎使用!”。 要求:请同学把预备知识、步骤、程序框图、调试好的程序及存在的问题写在下面(不够可以附页)。 程序一 public class hello { public static void main(String[] args) { for(int i=0;i<=4;i++) { System、out、println("Hello java! 欢迎使用!"); } } } 结果示意图1

CMOS数字集成电路设计_八位加法器实验报告

CMOS数字集成电路设计课程设计报告 学院:****** 专业:****** 班级:****** 姓名:Wang Ke qin 指导老师:****** 学号:****** 日期:2012-5-30

目录 一、设计要求 (1) 二、设计思路 (1) 三、电路设计与验证 (2) (一)1位全加器的电路设计与验证 (2) 1)原理图设计 (2) 2)生成符号图 (2) 3)建立测试激励源 (2) 4)测试电路 (3) 5)波形仿真 (4) (二)4位全加器的电路设计与验证 (4) 1)原理图设计 (4) 2)生成符号图 (5) 3)建立测试激励源 (5) 4)测试电路 (6) 5)波形仿真 (6) (三)8位全加器的电路设计与验证 (7) 1)原理图设计 (7) 2)生成符号图 (7) 3)测试激励源 (8) 4)测试电路 (8) 5)波形仿真 (9) 6)电路参数 (11) 四、版图设计与验证 (13) (一)1位全加器的版图设计与验证 (13) 1)1位全加器的版图设计 (13) 2)1位全加器的DRC规则验证 (14) 3)1位全加器的LVS验证 (14) 4)错误及解决办法 (14) (二)4位全加器的版图设计与验证 (15) 1)4位全加器的版图设计 (15) 2)4位全加器的DRC规则验证 (16) 3)4位全加器的LVS验证 (16) 4)错误及解决办法 (16) (三)8位全加器的版图设计与验证 (17) 1)8位全加器的版图设计 (17) 2)8位全加器的DRC规则验证 (17) 3)8位全加器的LVS验证 (18) 4)错误及解决办法 (18) 五、设计总结 (18)

实验报告要求和格式完整版

编号:TQC/K633 实验报告要求和格式完整 版 Daily description of the work content, achievements, and shortcomings, and finally put forward reasonable suggestions or new direction of efforts, so that the overall process does not deviate from the direction, continue to move towards the established goal. 【适用信息传递/研究经验/相互监督/自我提升等场景】 编写:________________________ 审核:________________________ 时间:________________________ 部门:________________________

实验报告要求和格式完整版 下载说明:本报告资料适合用于日常描述工作内容,取得的成绩,以及不足,最后提出合理化的建议或者新的努力方向,使整体流程的进度信息实现快速共享,并使整体过程不偏离方向,继续朝既定的目标前行。可直接应用日常文档制作,也可以根据实际需要对其进行修改。 实验报告要求 1. 认真完成实验报告,报告要用中国海洋大学实验报告纸,作图要用坐标纸。 2. 报告中的电路图、光路图、表格必须用直尺画,数据使用钢笔、圆珠笔不得使用铅笔。 3. 应在理解的基础上简单扼要的书写实验原理,不提倡大段抄书。 4. 应结合具体的实验现象和问题进行讨论。 实验报告格式

数电实验三加法器

实验三一.实验目的 1.掌握全加器的工作原理与逻辑功能。 2.掌握全加器的应用。 二.实验设备及器材 数字电路实验箱稳压电源 74LS00 CD4008B 三.实验原理 全加器是中规模组合逻辑器件,它实现二进制数码的加法运算。 表1 全加器真值表 CD4008B为四位加法器,其逻辑符号如图2,A3、A2、A1、A0和B3、B2、B1、B0为两个四位二进制数,CI为进位输入端,CO为进位输出端。 图2 全加器主要用于数值运算,i位全加器可以实现两个i位二进制数的加法运算。另外,全加器也可以实现组合逻辑函数,如用全加器实现四位二进制数向BCD码的转换。 四.实验内容

1.按照全加器真值表,利用逻辑电平产生电路及逻辑电平指示电路验证CD4008B的逻辑功能,画出测试电路图。 A3、A2、A1、A0和B3、B2、B1、B0为两个四位二进制数:加数和被加数,CIN为进位输入,S3、S2、S1、S0为输出的和,CON为进位输出端。 2.连接 B/BCD码转换电路,验证其实验结果是否与真值表一致。 二进制码转换为BCD码时,9以前即0000—1001,二进制数B和BCD码二者相等。但九以后,即1010—1111,需要给B加6(0110)才能和BCD码在数值上相等。因此利用四位全加器实现转换时,以四位二进制数作为被加数,而加数在四位二进制数为0000—1001时为0000,为1001—1111时为 0110,这样就可实现B/BCD的转换。 图3 B/BCD码转换电路 验证得其实验结果与真值表一致 3.设计电路,完成1位十进制数的相加运算,使实现7+9=?,6+4=?,和