北航verilog实验报告

北京航空航天大学

电子电路设计数字部分实验报告

实验一简单组合逻辑设计 (2)

实验二简单分频时序逻辑电路的设计 (3)

一.实验目的:1.掌握最基本组合逻辑电路的实现方法。 (3)

2.学习时序电路测试模块的编写。 (3)

3.学习综合和不同层次的仿真。 (3)

实验三利用条件语句实现计数分频时序电路 (5)

实验四阻塞赋值与非阻塞赋值的区别 (7)

实验五用always块实现较复杂的组合逻辑: (10)

实验六在 Verilog HDL中使用函数 (12)

实验七在Verilog HDL中使用任务(task) (14)

实验八利用有限状态机进行时序逻辑的设计 (17)

实验九楼梯灯 (19)

实验思考与总结 (29)

学院:

学号:

姓名:

实验一简单组合逻辑设计

一.实验目的:

1.掌握基本组合逻辑电路的实现方法。

2.初步了解两种基本组合逻辑电路的生成方法。

3.学习测试模块的编写。

4.通过综合和布局布线了解不同层次仿真的物理意义。

二.实验设备:

安装的PC机。

三.实验内容:

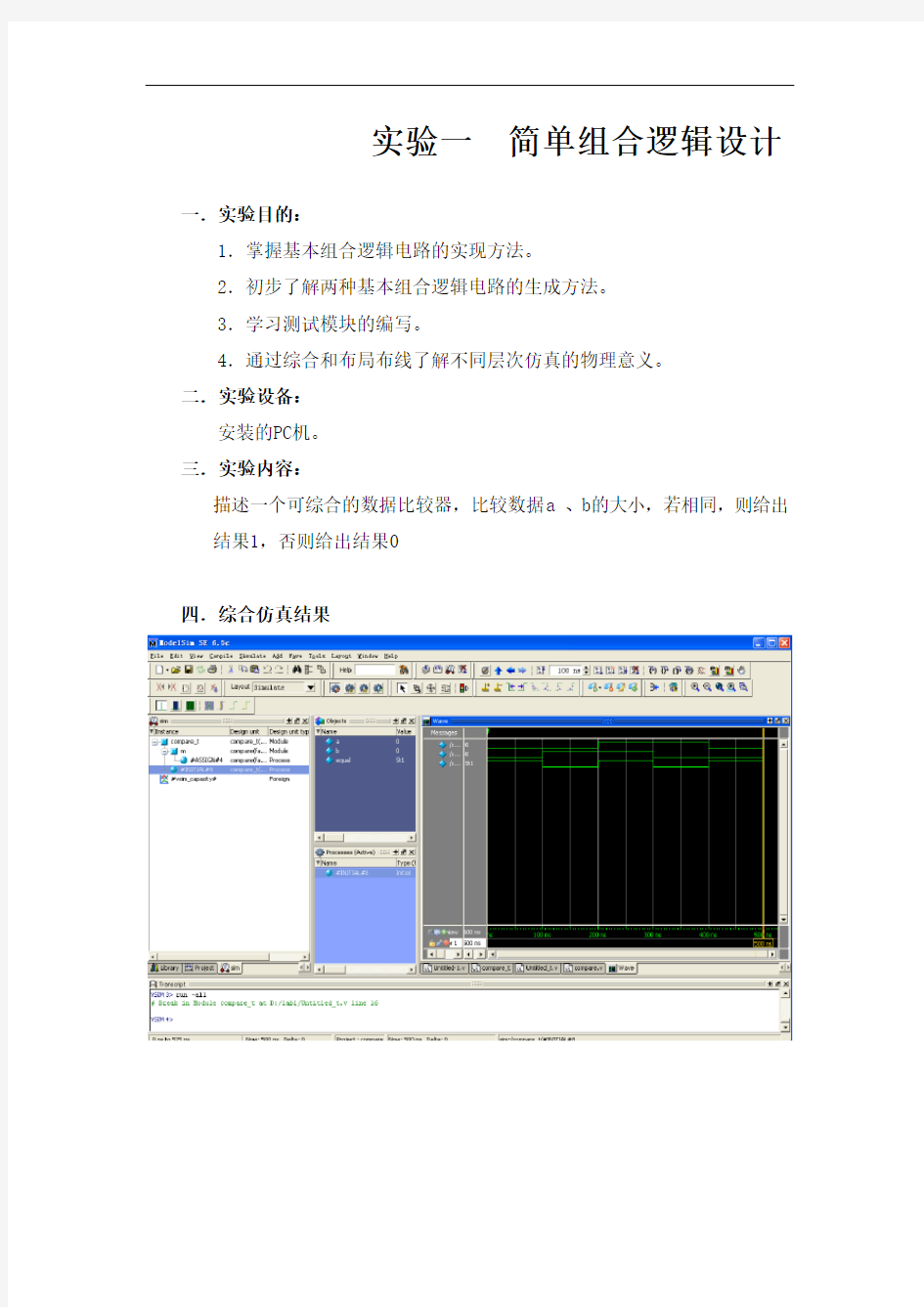

描述一个可综合的数据比较器,比较数据a 、b的大小,若相同,则给出结果1,否则给出结果0

四.综合仿真结果

实验二简单分频时序逻辑电路的设计

一.实验目的:1.掌握最基本组合逻辑电路的实现方法。

2.学习时序电路测试模块的编写。

3.学习综合和不同层次的仿真。

二.实验设备:

安装的PC机。

三.实验内容:

用always块和@(posedge clk)或@(negedge clk)的结构表述一个1/2分频器的可综合模型,观察时序仿真结果

四.实验代码

module half_clk(reset,clk_in,clk_out);

input clk_in,reset;

output clk_out;

reg clk_out;

always@(posedge clk_in)

begin

if(!reset)

clk_out=0;

else

clk_out=~clk_out;

end

endmodule

`timescale 1ns/100ps

`define clk_cycle 50

module top;

reg clk,reset;

wire clk_out;

always #`clk_cycle clk=~clk;

initial

begin

clk=0;

reset=-1;

#10 reset=0;

#110 reset=1;

#100000 $stop;

end

half_clk m0(.reset(reset),.clk_in(clk),.clk_out(clk_out)); endmodule

五.综合仿真结果

实验三利用条件语句实现计数分频时序电路

一.实验目的:

1.掌握条件语句在简单时序模块设计中的使用。

2.学习在Verilog模块中应用计数器。

3.学习测试模块的编写、综合和不同层次的仿真。

二.实验设备:

安装Modelsim-6.5c的PC机。

三.实验内容:

仿真一个可综合风格的分频器,将10MB的时钟分频为500KB的时钟,定义一个计数器,原理同1/2分频器一样,只不过分频变为1/20。

四.实验代码

module fdivision(RESET,F10M,F500K);

input RESET,F10M;

output F500K;

reg F500K;

reg[7:0]j;

always @(posedge F10M)

if(!RESET)

begin

F500K <= 0;

j<=0;

end

else

begin

if(j==9)

begin

j<=0;

F500K =~ F500K;

end

else

j<=j+1;

end

endmodule

`timescale 1ns/1ps

`define clk_cycle 50

module division_Top;

reg F10M,RESET;

wire F500K_clk;

always #`clk_cycle F10M=~F10M;

initial

begin