数字逻辑课程教学大纲

《数字逻辑》教学大纲

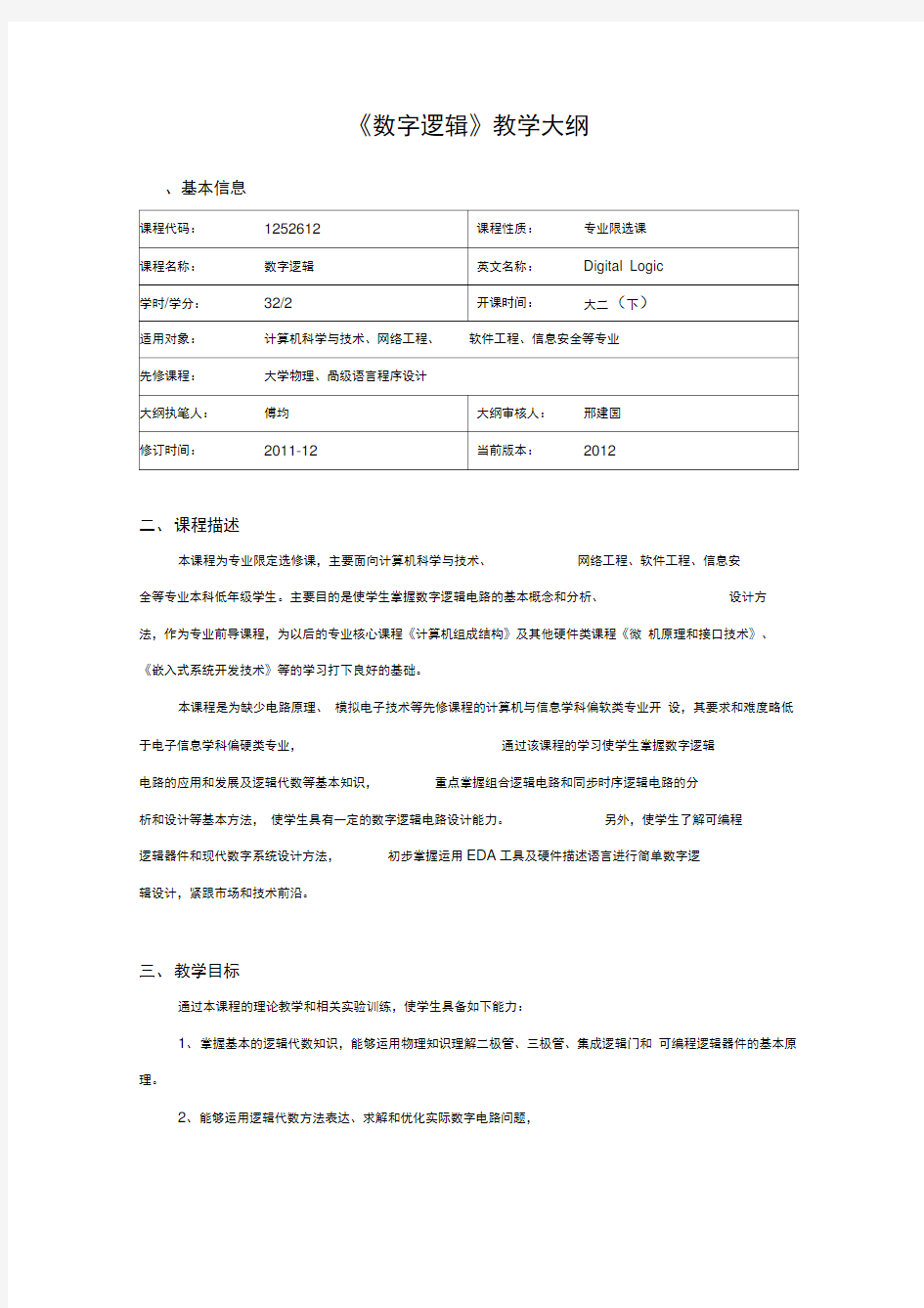

、基本信息

二、课程描述

本课程为专业限定选修课,主要面向计算机科学与技术、网络工程、软件工程、信息安

全等专业本科低年级学生。主要目的是使学生掌握数字逻辑电路的基本概念和分析、设计方

法,作为专业前导课程,为以后的专业核心课程《计算机组成结构》及其他硬件类课程《微机原理和接口技术》、《嵌入式系统开发技术》等的学习打下良好的基础。

本课程是为缺少电路原理、模拟电子技术等先修课程的计算机与信息学科偏软类专业开设,其要求和难度略低于电子信息学科偏硬类专业,通过该课程的学习使学生掌握数字逻辑

电路的应用和发展及逻辑代数等基本知识,重点掌握组合逻辑电路和同步时序逻辑电路的分

析和设计等基本方法,使学生具有一定的数字逻辑电路设计能力。另外,使学生了解可编程

逻辑器件和现代数字系统设计方法,初步掌握运用EDA工具及硬件描述语言进行简单数字逻

辑设计,紧跟市场和技术前沿。

三、教学目标

通过本课程的理论教学和相关实验训练,使学生具备如下能力:

1、掌握基本的逻辑代数知识,能够运用物理知识理解二极管、三极管、集成逻辑门和可编程逻辑器件的基本原理。

2、能够运用逻辑代数方法表达、求解和优化实际数字电路问题,

3、能够分析小规模、中规模组合逻辑电路和时序逻辑电路,掌握各种逻辑门、基本触

发器、中规模集成器件的功能及基本应用。

4、能够利用逻辑门、基本触发器、中规模集成器件和可编程逻辑器件设计一定功能的组合逻辑电路和时序逻辑电路,并进行优化。

5、能够应用专业EDA软件设计一定功能的数字系统,并能进行仿真和验证。

四、课程目标对毕业要求的支撑

五、教学容

第1章绪论(支撑课程目标1)

重点容:数制和编码的概念,各种不同数制间的转换方法,二进制的运算及原、反、补码数的表示及转换,二-十进制代码(BCD代码)。

难点容:建立模拟信号和数字信号的概念,二进制的运算及原、反、补码数的表示。

教学容:掌握数制及其转换,编码的概念,了解常用码的一些应用,熟悉数字编码的转换。

1.1数字电路逻辑设计概述

1.2数制及其转换

1.3二-十进制代码(BCD 代码) 1.4算术运算与逻辑运算

第2章 逻辑函数及其简化 (支撑课程目标1、2)

重点容:逻辑代数的各种表达形式,逻辑代数的三个规则和常用公式,

逻辑代数的化简

方法,卡诺图法。

难点容:简单逻辑命题建立逻辑函数的方法。

教学要求:掌握逻辑代数基本定理、基本规则和常用公式,掌握用代数法和卡诺图法简 化逻辑函数的方法,掌

握由简单逻辑命题建立逻辑函数的方法。

2.1逻辑代数

22逻辑函数的简化

3.1晶体管的开关特性 3.2 TTL 集成逻辑门

第4章 组合逻辑电路 (支撑课程目标 3、4)

重点容:组合逻辑电路概念、组合逻辑电路的分析与设计方法,全加器、编码器、译码 器、数值比较器、数据选择器等常用组合逻辑功能器件, 采用常用的小规模、中规模集成器

件进行组合逻辑电路设计。

难点容:组合逻辑电路的冒险现象,产生冒险的原因,判断与避免冒险的方法。

教学要求:掌握全加器、编码器、译码器、数值比较器、数据选择器等常见中规模组合 逻辑器件的逻辑功能与应用,掌握采用小规模和中规模集成器件的组合逻辑电路设计方法, 理解组合逻辑电路的冒险现象以及如何避免冒险。

4.1组合逻辑电路分析

第3章集成逻辑门

(支撑课程目标1)

重点容: 二极管与三极管的开关特性。 TTL 集成逻辑门的主要外部特性。 难点容: 二极管和三极管的开关特性,

TTL 集成逻辑门的工作原理。

教学要求: :了解二极管和三极管的开关特性,掌握通用数字集成电路的分类,了解

门的工作原理、 主要外特性。

TTL

4.2组合逻辑电路设计 4.3组合逻辑电路的冒险现象

第5章集成触发器 (支撑课程目标3、4)

重点容:基本触发器、钟控触发器、主从触发器、边沿触发器的电路结构与功能特点, 触发器逻辑功能的描述方法,触发器类型转换。

难点容:钟控T 触发器的空翻与主从 J-K 触发器主触发器的一次翻转现象。 教学要求:理解集成触发器电路组成和工作原理,

掌握集成触发器功能的描述方法和脉

冲工作特性,了解不同类型集成触发器的转换方法。重点掌握集成触发器的应用。

5.1基本触发器 5.2钟控触发器 5.3主从触发器 5.4边沿触发器

第6章 时序逻辑电路 (支撑课程目标 3、4)

重点容:时序电路的分析方法:驱动方程、输入方程、状态转移方程、状态转移表、状 态转移图和时序图,常用时序电路:寄存器、移位寄存器、同步计数器等。时序电路的设计 方法:设计原则和一般步骤, 采用小规模集成器件设计同步计数器, 采用中规模集成器件设

第7章 VHDL 与数字逻辑设计 (支撑课程目标 3、4、5)

重点容:VHDL 语言的基本结构、数据类型、语句和设计方法。 难点容:可编程逻辑器件,现代数字系统设计方法,

VHDL 中的并行语句。

计任意模值计数(分频)器。

难点容:小规模同步时序逻辑电路分析方法, 频)器的方法。

教学要求:掌握时序逻辑电路的基本概念, 法,掌握采用中规模集成器件实现任意模值计数

6.1时序逻辑电路概述 6.2时序逻辑电路分析 6.3时序逻辑电路设计

采用中规模集成器件实现任意模值计数(分

掌握小规模同步时序逻辑电路分析和设计方 (分频)器的方法。

教学要求:了解可编程逻辑器件和现代数字系统设计方法,掌握运用 硬件描述语言进行

简单数字逻辑设计。

7.1可编程逻辑器件和硬件描述语言概述 7.2 VHDL 基本数据类型和运算操作符 7.3 VHDL 中的顺序语句和并行语句 7.4 VHDL 数字逻辑电路设计举例

六、教学安排

该课程每周2学时,16周,32学时为课堂授课教学时间。

实验实践单独设课,同时开

设开放实验。建议教学进度如下:

七、课实验容、要求及学时

没有课实验,基础实验单独开设,

VHDL 实验通过开放实验开设。

请删除此黄色高亮。如果有课实验,请填写下表;如果没有,则删除下表,并用文字适当说 明。 八、教学方法与手段

以课堂理论教学为主,实验实践为辅。课堂理论教学以多媒体课件为主, 黑板板书为辅。

EDA 工具及VHDL

在教学过程中注重能力的培养,以实际应用系统为例,提高理论教学实用性,提高学生分析

和解决实际问题的能力。另外,本课程开设Blackboard电子教学平台,学生可以进行自主

学习、提交作业、讨论问题。鼓励学生参加开放实验,在平时VHDL实验作业基础上进一步提高EDA设计能力。

九、考核方式及成绩评定

考核方式:期末考试闭卷,平时作业、出勤、课堂情况,VHDL实验作业。

成绩评定标准:总成绩(百分制)=平时成绩X 30%+ VHDL实验X 10% +期末考试成

绩X 60%。

十、教材及主要参考书