EDA实验一 七人表决器

河北科技大学

实验报告

2013级电信专业132 班学号130701213 2016年5月23日

姓名田继辉同组人指导教师于国庆

实验名称实验一七人表决器成绩

实验类型设计型批阅教师

一、实验目的

(1)掌握MUXPLUS II语言输入的设计过程。

(2)初步了解VHDL语言。

(3)熟悉FPGA项目设计的基本流程。

二、实验原理:

用七个开关作为表决器的7个输入变量,输入变量为逻辑“1”时表示表决者“赞同”;

输入变量为逻辑“0”时表示表决者“不赞同”;输出逻辑“1”时,表示表决“通过”;

输出逻辑“0”时,表示表决“不通过”;当表决器的七个输入变量中有4个及以上为“1”

时,则表决器输出为“1”,否则为“0”。

表决器输入采用试验箱K1~K16,输出采用试验箱L15、L16指示;同意红灯亮,否则黄灯亮。

三、实验内容及步骤

1.打开MUXPLUS II VHDL编辑器,完成七人表决器的设计。包括VHDL程序输入、编译、综合。

实验程序如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY vote7 IS

PORT

( men : IN std_logic_vector(6 downto 0);

pass,stop : buffer std_logic

);

END vote7;

ARCHITECTURE behave OF vote7 IS

BEGIN

stop<=not pass;

PROCESS (men)

variable temp:std_logic_vector(2 downto 0);

BEGIN

temp:="000";

for i in 0 to 6 loop

if(men(i)='1') then

temp:=temp+1;

else

temp:=temp+0;

end if;

end loop;

pass<=temp(2);

END PROCESS;

END behave;

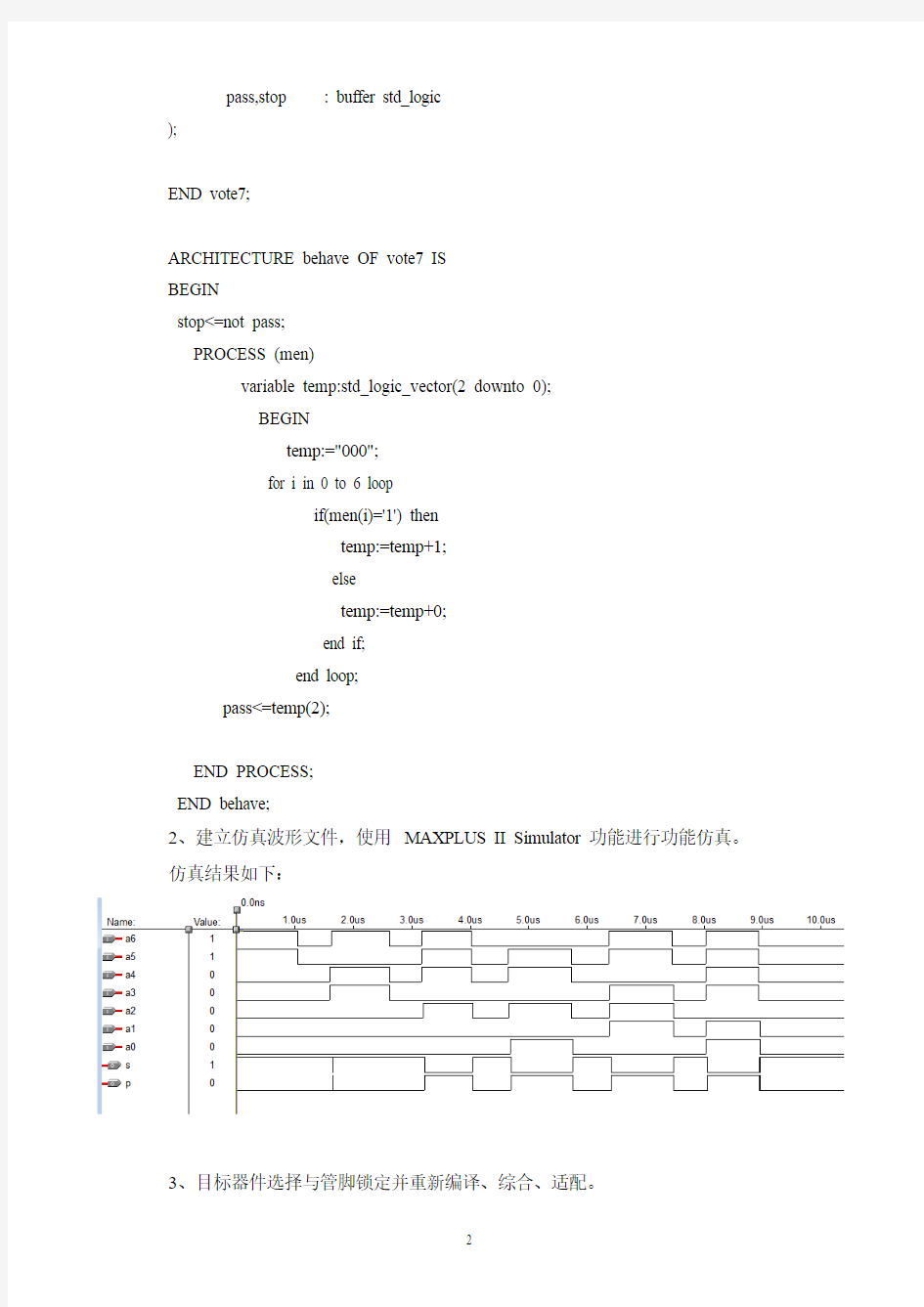

2、建立仿真波形文件,使用MAXPLUS II Simulator功能进行功能仿真。仿真结果如下:

3、目标器件选择与管脚锁定并重新编译、综合、适配。

FPGA型号:EP1K100QC208-3

引脚绑定:

4、下载并验证结果

将编译好的程序进行一系列的元件引脚绑定之后,Programmer –> Configuration 成功,测试按键发现有个键按下去了但是并未显示想要的结果,于是更换别的LK按键指示灯,这次达到了预期的效果。接着画仿真电路图,设置End time=60.0μs,按照实验要求设计出七人表决器的仿真波形,Simulator一下,结果在意料之外。检查不出什么毛病,请教她人才明白:原来是忘了保存。最后结果如预料一般很完美,但按下的按键多于三个(即四个或四个以上)时,指示灯会亮,从而实现少数服从多数的结果。

四、实验结果与总结

表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。七人表决器由七个人来投票,当同意的票数大于或者等于4人时,则认为同意;反之,当否决的票数大于或者等于4人时,则认为不同意。实验中用7个拨挡开关来表示七个人,当对应的拨挡开关输入为‘1’时,表示此人同意;否则若拨挡开关输入为‘0’时,则表示此人反对。表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮,;否则,如果表决的结果为反对,则LED不会被点亮。同时用七段显

示数码管来显示赞成的人数和反对的人数。

由于第一次是接触MAX+plusⅡ,英文版的,导致刚开始操作时无从下手。虽然老师有在亲切和蔼地为同学们讲述操作流程和如何使用,但有时候还是没有跟上,问旁边的同学也不会。这就到了考验一个人学习能力的时候了,通过向他人请教和自己摸索,终于熟悉了一系列的操作步骤。当到了Floorplan Editor绑定元件引脚这一步时,竟然没有改显示的引脚界面图……因为还要选择设备为——EP1K100QC208-3,和外围硬件箱芯片相匹配。第一阶段在不断地尝试与调试、不断地请教与重做中完成了,脑门子都已是大汗淋漓。第二阶段的画仿真电路图,有了前面一系列的探索与尝试,这一步很快就完成了。只是要将其缩小到μm级而不是nm级,只为了更符合要求,看起来也美观一些。虽然忘记了时间要有所延迟以便更贴近于实际生活,不过总的来说也算大功告成了。

只有实践才是检验真理的唯一标准,同理,只有通过亲自动手实验你才能真正学到点东西。你不去做,你永远不知道真相。人类的智慧也是无穷无尽的,在EDA领域,不仅创造了FPGA 现场可编程逻辑门阵列这种技术,而且还开发了VHDL超高速集成电路硬件描述语言这一门编程语言,使得人机自动化技术的发展愈发趋于完善。科学与技术的未来是无限的,需要每一位感兴趣的信息学子与IT人士共同探索。这次实验,不仅是一次简单的一两个小时的实验,更是我们学习向前推进的一大步。

四选一、四位比较器、加法器、计数器、巴克码发生器、七人表决器

EDA实验报告 姓名: 学号: 班级:

实验14选1数据选择器的设计 一、实验目的 1.学习EDA软件的基本操作。 2.学习使用原理图进行设计输入。 3.初步掌握器件设计输入、编译、仿真和编程的过程。 4.学习实验开发系统的使用方法。 二、实验仪器与器材 1.EDA开发软件一套 2.微机一台 3.实验开发系统一台 4.打印机一台 三、实验说明 本实验通过使用基本门电路完成4选1数据选择器的设计,初步掌握EDA设计方法中的设计输入、编译、综合、仿真和编程的过程。实验结果可通过实验开发系统验证,在实验开发系统上选择高、低电平开关作为输入,选择发光二极管显示输出电平值。 本实验使用Quartus II 软件作为设计工具,要求熟悉Quartus II 软件的使用环境和基本操作,如设计输入、编译和适配的过程等。 实验中的设计文件要求用原理图方法输入,实验时,注意原理图编辑器的使用方法。例如,元件、连线、网络名的放置方法和放大、缩小、存盘、退出等命令的使用。学会管脚锁定以及编程下载的方法等。 四、实验要求 1.完成4选1数据选择器的原理图输入并进行编译; 2.对设计的电路进行仿真验证; 3.编程下载并在实验开发系统上验证设计结果。 五、实验结果 4选1数据选择器的原理图: 仿真波形图:

管脚分配:

实验2 四位比较器 一、实验目的 1.设计四位二进制码比较器,并在实验开发系统上验证。 2.学习层次化设计方法。 二、实验仪器与器材 1.EDA 开发软件 一套 2.微机 一台 3.实验开发系统 一台 4.打印机 一台 5.其它器件与材料 若干 三、实验说明 本实验实现两个4位二进制码的比较器,输入为两个4位二进制码0123A A A A 和 0123B B B B ,输出为M (A=B ),G (A>B )和L (A七人表决器实验报告

七人表决器 一.实验目的 1.掌握Quartus II软件安装,熟悉Quartus II操作环境。 2.初步了解VHDL语言。 3.学习使用行为级描述方法设计电路。 二.实验原理 七人表决器 使用7个电平开关作为表决器的7个输入变量,输入为电平“1”时表示表决者“赞同”,输入为电平“0”时表示表决者“不赞同”。当表决器的7个输入变量中有不少于4个输入变量输入“1”,那么表决结果输出逻辑高电平,表示表决“通过”,否则,输出逻辑低电平,表示表决“不通过”。 七人表决器的可选设计方案非常多,可以采用使用全加器的组合逻辑。使用VHDL 进行设计的时候,可以选择行为级描述、寄存器级描述,结等方法。 当采用行为级描述的时候,采用一个变量记载选举通过的总人数。当这个变量的数值大于等于4时,表决通过,绿灯亮;否则表决不通过,黄灯亮。因此,设计时,需要检查每一个输入的电平,并且将逻辑高电平的输入数目进行相加,并且进行判断,从而决定表决是否通过。 二.实验内容 1.安装Quartus II软件,熟悉Quartus II操作环境。 2.使用VHDL实现上述描述。 3.波形仿真。 4.生成元件以及RTL 四.设计提示 1.初次接触VHDL应该注意程序的框架结构,数据类型和运算操作符。 2.了解变量和信号的区别。 3.了解进程内外语句的顺序和并行执行的区别。 4.设计文本的端口可如下:

《VHDL 语言与数字逻辑电路设计》实验指导书 - 2 – 设计文本: LIBRARY IEEE; library ieee; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_unsigned.ALL; ENTITY vote7 IS PORT( men:in std_logic_vector(6 downto 0); LedPass,LedFail:OUT std_logic ); END vote7; ARCHITECTURE behave OF vote7 IS signal pass:std_logic; BEGIN PROCESS(men) variable temp:std_logic_vector(2 downto 0); BEGIN temp:="000"; for i in 0 to 6 loop if(men(i)='1')then temp:=temp+1; else temp:=temp+0; end if; end loop; pass<=temp(2); END PROCESS; LedPass<='1' WHEN pass='1'ELSE '0'; LedFail<='1' WHEN pass='0'ELSE '0'; --库和程序包 --实体 --结构体 --结束

单片机七人表决器

一.方案设计 1.设计题目:七人表决器。 2.实训要求 利用AT89S51单片机设计并制作会议表决计票器电路。具体要求如下: 1、可供57个人进行表决,每个人有一个“同意”和一个“反对”按键,表决时两个键先按下的一个有效,若再按另一个键将清楚前一次按键的效能;每次表决每个按键只能是第一次按的有效,多按的次数无效,除非前一次按键的效能已被清楚或没有生效。 2、会议主持人可利用按键控制表决开始和结束;开始表决后,点亮黄色指示灯,表示可以进行表决,同时清楚原来的表决结果;结束表决后显示表决结果;“同意”多于“反对”点亮绿色指示灯,反之点亮红色指示灯。 3、在实现上述功能的基础上增加“同意”数和“反对”数的显示。 二.硬件电路设计和原理。 1.硬件设计思路: 设计题目为5—7人表决器,题目选为七人表决器,七个按键表示同意,七个按键表示反对,各按键与单片机的输入端口相连,因此可选用单片机的四个I/O口,因为在单片机内部P1和P2都有上啦电阻,而P0没有上啦电阻,要在外部加上一个上拉电阻,为了简化电路,把P1和P2口选为按键同意和反对的输入端,因为表决考试和结束要

利用主持人按键来控制,我采用外部中断0和外部中断一来控制其开始和结束;设计要求中需要四张灯,分别为2个红灯,一个黄灯,一个绿灯,其中三个灯用于输出显示,可用单片机的I/O口,另外一个红灯作为电源灯来显示,判断是否通电,因为P1口和P2口用做按键的同意和反对,把P2剩余的I/O口与三个灯连接,分别连接在P2.3,P2.4,P2.5口,因为P0口是低电平有效所以我的P0口与LED现实器相连用于显示反对与同意的人数的多少,采用动态显示的方式,为了保证两个显示器不再相同时间显示相同的数字,所以LED显示器的公共端受另外一组信号的控制,采用延时的方式让它们分别显示出来。 2.元件参数确定: 设计中需要四盏灯,分别为两个红灯,一个绿灯,一个黄灯,P0口的输出端输出高电平一般为5伏左右,最大电流为五毫安,因此必须加上限流电阻,我选用的是470欧的电阻,然后将单片机的最小系统加入此次的电路中。 3.元件清单: 14个开关用于7人同意与反对按键,另外两个开关用做控制投票开始和结束的总开关。 电容:用于单片机的最小系统。 发光二极管:用于表示投票开始与结束,和最后同意与反对票数的对比情况。 电阻:用于限流。

8位全加器实验报告

实验1 原理图输入设计8位全加器 一、实验目的: 熟悉利用QuartusⅡ的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个8位全加器的设计把握利用EDA软件进行电子线路设计的详细流程。 二、原理说明: 一个8位全加器可以由8个1位全加器构成,加法器间的进位可以串行方式实现。即将低位加法器的进位输出cout与其相邻的高位加法器的最低进位输入信号cin相接。而一个1位全加器可以按照本章第一节介绍的方法来完成。 三、实验内容: 1:完全按照本章第1节介绍的方法与流程,完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真。 2:建立一个更高的原理图设计层次,利用以上获得的1位全加器构成8位全加器,并完成编译、综合、适配、仿真和硬件测试。 四、实验环境: 计算机、QuartusII软件。 五、实验流程: 实验流程: 根据半加器工作原 理,建立电路并仿 真,并将元件封装。 ↓ 利用半加器构成一位 全加器,建立电路并 仿真,并将元件封 装。 ↓ 利用全加器构成8位全 加器,并完成编译、综 合、适配、仿真。 图1.1 实验流程图

六、实验步骤: 1.根据半加器工作原理建立电路并仿真,并将元件打包。(1)半加器原理图: 图1.2 半加器原理图(2)综合报告: 图1.3 综合报告: (3)功能仿真波形图4: 图1.4 功能仿真波形图

时序仿真波形图: 图1.5 时序仿真波形图 仿真结果分析:sout为和信号,当a=1,b=0或a=0,b=1时,和信号sout为1,否则为0.当a=b=1时,产生进位信号,及cout=1。 (4)时序仿真的延时情况: 图1.6 时序仿真的延时情况 (5)封装元件: 图1.7 元件封装图 2. 利用半加器构成一位全加器,建立电路并仿真,并将元件封装。 (1)全加器原理图如图: 图2.1 全加器原理图

EDA 1位全加器实验报告

南华大学 船山学院 实验报告 (2009 ~2010 学年度第二学期) 课程名称EDA 实验名称1位全加器 姓名学号200994401 专业计算机科学与 班级01 技术 地点8-212 教师

一、实验目的: 熟悉MAX+plus 10.2的VHDL 文本设计流程全过程 二、实验原理图: ain cout cout ain bin sum cin bin sum cin f_adder or2a f e d u3 u2u1b a c co so B co so B h_adder A h_adder A 三、实验代码: (1)LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY f_adder IS PORT (ain ,bin ,cin : IN STD_LOGIC; cout ,sum : OUT STD_LOGIC ); END ENTITY f_adder; ARCHITECTURE fd1 OF f_adder IS COMPONENT h_adder PORT ( a ,b : IN STD_LOGIC; co ,so : OUT STD_LOGIC); END COMPONENT ; COMPONENT or2a PORT (a ,b : IN STD_LOGIC; c : OUT STD_LOGIC); END COMPONENT ; SIGNAL d ,e ,f : STD_LOGIC; BEGIN u1 : h_adder PORT MAP(a=>ain ,b=>bin ,co=>d ,so=>e); u2 : h_adder PORT MAP(a=>e , b=>cin , co=>f ,so=>sum); u3 : or2a PORT MAP(a=>d , b=>f , c=>cout);

七人表决器

学院名称电子技术基础课程设计报告 七人表决器电路设计报告 学生姓名__ _____ 学号 专业 指导教师 系别__ _ 年月日

一、评语(根据学生答辩情况及其报告质量综合评定)。 二、评分 指导教师签字: 年月日

摘要 本次设计的七人表决器,是投票系统中的客户端,是一种代表投票或举手表决的表决装置。表决时,与会的有关人员只要按动各自表决器上“赞成”“反对”“弃权”的某一按钮,相应灯的明亮即显示出表决结果。在七人表决器中七个人分别用手指拨动开关 SW1、SW2、SW3、SW4、SW5、SW6、SW7 来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方)不同意就把自己的指拨开关拨到低电平(下方)。表决结果用 LED(高电平亮)显示,如果决议通过那么发光二极管会发亮;如果不通过那么发光二极管就不亮;如果对某个决议有任意四到七人同意,那么此决议通过,发光二极管就会发亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,发光二极管就不会亮。根据设计与制作的主要内容按照设计题目,以及所学的组合逻辑所学的知识及数字电路和嵌入式的知识完成七人表决器的设计,使之能够满足表决时少数服从多数的表决规则,根据逻辑真值表和逻辑表达式完成表决功能。首先根据七人多数表决电路列出真值表,进行化简,写出逻辑表达式,画出逻辑图。

目录 1 概述 (1) 2 系统总体方案及硬件设计 (2) 2.1电路的总体原理框图 (2) 2.2元件选择 (2) 3 各模块设计 (3) 3.1投票按键部分电路设计 (3) 3.2输入转换部分及控制电路 (3) 3.3票数统计部分及控制电路 (4) 3.4票据分析与结果显示分 (5) 3.5总体电路 (7) 4 软件仿真 (8) 5 课程设计体会 (9) 参考文献(按照标准格式) (10)

EDA设计实验报告

摘要 通过实验学习和训练,掌握基于计算机和信息技术的电路系统设计和仿真方法。要求: 1. 熟悉multisim软件的使用,包括电路图编辑、虚拟仪器仪表的使用和掌握常见电路分析 方法。2. 能够运用multisim软件对模拟电路进行设计和性能分析,掌握eda设计的基本方 法和步骤。multisim常用分析方法:直流工作点分析、直流扫描分析、交流分析。掌握设计 电路参数的方法。复习巩固单级放大电路的工作原理,掌握静态工作点的选择对电路的影响。 了解负反馈对两级放大电路的影响,掌握阶梯波的产生原理及产生过程。 关键字:电路仿真 multisim 负反馈阶梯波 目次 实验一 (1) 实验二............................................................................................. 11 实验三 (17) 实验一单级放大电路的设计与仿真 一、实验目的 1. 设计一个分压偏置的单管电压放大电路,要求信号源频率5khz(峰值10mv) , 负载电阻5.1kω,电压增益大于50。 2. 调节电路静态工作点(调节电位计),观察电路出现饱和失真和截止失真的输出 信号波形,并测试对应的静态工作点值。 3. 调节电路静态工作点(调节电位计),使电路输出信号不失真,并且幅度尽可能 大。在此状态下测试: ①电路静态工作点值; ②三极管的输入、输出特性曲线和? 、 rbe 、rce值;③电路的输入电阻、输出电 阻和电压增益;④电路的频率响应曲线和fl、fh值。 二、实验要求 1. 给出单级放大电路原理图。 2. 给出电路饱和失真、截止失真和不失真且信号幅度尽可能大时的输出信号波形 图,并给出三种状态下电路静态工作点值。 3. 给出测试三极管输入、输出特性曲线和? 、 rbe 、rce值的实验图,并给出 测试结果。 4. 给出正常放大时测量输入电阻、输出电阻和电压增益的实验图,给出测试结果 并和理论计算值进行比较。 5. 给出电路的幅频和相频特性曲线,并给出电路的fl、fh值。 6. 分析实验结果。 三、实验步骤 实验原理图: 饱和失真时波形: 此时静态工作点为: 所以,i(bq)=4.76685ua i(cq)=958.06700ua u(beq)=0.62676v u(ceq)=0.31402v 截止失真时波形: 此时静态工作点为: 所以,i(bq)=2.07543ua i(cq)=440.85400ua u(beq)=0.60519v u(ceq)=5.54322v 最大不失真时波形:篇二:eda课程设计实验报告电子电工实习 华北电力大学

三人表决器EDA实验

三人表决器 1、实验目的 掌握在Quartus Ⅱ开发环境下,运用硬件描述语言输入法对“三人表决器”进行设计输入、编译、调试和仿真的方法。 “三人表决器”电路的输入为SW1、SW2 和SW3,输出为L3 和L4,位宽均为1 位。当SW1、SW2 和SW3中有超过2个以上的输入为1时,要求熟悉整个设计流程,从打开、建立文档、编辑、编译、建立激励信号波形及最后仿真的整个过程。 2、实验内容 (1)在Quartus Ⅱ开发环境下,建立工程,并将三人表决器的硬件描述语言程序输入; (2)完成编译、调试和仿真,分析实验仿真结果,并判断其正确性。 3、教学形式 (1)本实验为验证型实验,学生在实验前预习实验指导书; (2)指导教师应该在实验前阐述实验目的、内容、方法和步骤,并且就实验中的难点和注意事项进行一定的说明; (3)实验结束之后,学生按照实验报告的书写格式自行完成实验报告。 4、应达到的实验能力标准 (1)能熟练地在Quartus Ⅱ开发环境下,建立工程,并将三人表决器的硬件描述语言程序输入; (2)能熟练地进行编译和调试,排除编译后的错误; (3)正确地在仿真之前进行功能仿真的设置,并熟练地完成功能仿真; (4)掌握基于ACEX1K系列EP1K30TC144-3器件的时序仿真方法。 5、实验原理 三个人分别用拨位开关SW1、SW2、SW3 来表示自己的意愿,如果对某决议同意,各人就把自己的拨位开关拨到高电平,不同意就把自己的拨位开关拨到低电平。表决结果用LED (高电平亮)显示,如果决议通过那么实验板上L3 灯亮;如果不通过那么实验板上L3 灯不亮;如果对某个决议有任意二到三人同意,那么此决议通过,L3 亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L3 灯不亮。 6、实验步骤 双击Quartus4. 2 图标,启动Quartus4. 2,并新建工程

七人表决器

EDA技术课程设计设计题目:七人表决器设计 院系:电气信息学院 专业年级:电子信息工程2010级 学生姓名:XXX 学号:XXXXXXX 指导教师:XXXXX 时间:2013年1月13日

用VHDL 设计七人表决器 一、实验目的 1、熟悉 VHDL 的编程。 2、熟悉七人表决器的工作原理。 3、进一步了解实验系统的硬件结构。 二、实验原理 所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。 七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4 时,则认为同意;反之,当否决的票数大于或者等于4时,则认为不同意。实验中用7个拨动开关来表示七个人,当对应的拨动开关输入为‘1’时,表示此人同意;否则若拨动开关输入为‘0’,则表示此人反对。表决的结果用一个LED表示,若表决的结果为同意,则 LED 被点亮;否则,如果表决的结果为反对,则 LED 不会被点亮。同时,数码管上显示通过的票数。 三、实验内容 本实验就是利用实验系统中的拨动开关模块和LED模 块以及数码管模块来实现一个简单的七人表决器的功能。 拨动开关模块中的K1~K7表示七个人,当拨动开关输入为 ‘1’时,表示对应的人投同意票,否则当拨动开关输入为

‘0’时,表示对应的人投反对票;LED 模块中 LED1 表示七人表决的结果,当 LED1 点亮时,表示此行为通过表决;否则当 LED1 熄灭时,表示此行为未通过表决。同时通过的票数在数码管上显示出来。 四、硬件系统组成框图 五、VHDL程序实现 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity bjq7 is

EDA课程设计----八位二进制全加器

EDA设计说明书 课程名称:EDA技术实用教程 设计题目:八位二进制全加器 院系:电子信息与电气工程学院学生姓名: 学号: 专业班级: 指导教师:李响 2011 年6 月1

1. 设计目的 熟悉利用QuartusⅡ的原理图输入法设计简单的组合电路,掌握层次化设计的方法,并通过一个八位全加器的设计把握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。 2. 设计原理 2.1 一位全加器的原理 一位全加器可以用两个半加器及一个或门连接而成,因此需要首先完成半加器的设计。在本设计中,将采用原理图输入法来完成设计。 一位全加器的设计步骤: ①为本项工程设计建立文件夹; ②输入设计项目和存盘; ③将设计项目设计成可调用的元件; ④设计全加器顶层文件; ⑤将设计项日设置成工程和时序仿真。 2.2 八位全加器的原理 一个八位全加器可以由八个一位全加器构成,加法器之间的进位可以用串行方式实现,即将低位加法器的进位输出cout 与相邻的高位加法器的最低进位输入信号cin 相接。 3. 设计方案与仿真 3.1 一位全加器的设计与仿真 全加器的实现是以半加器的实现为基础的,因此,要设计全加器应首先设计一个一位的半加器。半加器的实现方案为: ①为此项工程建立文件夹; ②在基本元件库中,选中需要的元件,将元件(包含元件and2、not 、xnor 和输 入输出引脚input、output)调入原理图编辑窗口中;

③将己设计好的原理图文件存盘; ④将所设计的半加器设置成可调用的元件。 用原理图输入法所设计的半加器原理图如图3-1所示,利用QuartusⅡ软件平台,根据图3-1所示电路,可生成一个半加器元件符号,如图3-2所示。在半加器的基础上,为了建立全加器的顶层文件,必须再打开一个原理图编辑窗口,方法同上。其中,所选择的元件包含半加器、或门和输入输出引脚,由此可得到如图3-3所示的全加器原理图;进而可生成个全加器元件符号,如图3-4所示。 图3-1 半加器原理图图3-2 半加器元件符号 图3-3 全加器原理图图3-4 全加器元件符号按照一位全加器原理图连接电路,通过编译、仿真所得的波形图如图3-5所示: 图3-5 一位全加器时序仿真波形 根据图3-5可知,当输入信号ain 、bin 、cin 全是低电平时,输出信号sum 和cout 全是低电平;当输入信号ain 、bin 、cin 中有且只有一个为高电平时,输出信号sum 为高电平,输出信号cout 为低电平;当输入信号ain 、bin 、cin 中有两个为

七人表决器实验报告

竭诚为您提供优质文档/双击可除七人表决器实验报告 篇一:哈工大电工学新技术实践实验报告-7人表决器 总成绩: 一、设计任务 1、有七人参与表决,显示赞同者个数。 2当赞同者达到及超过4人时,绿灯显示表示通过。 二、设计条件 本设计基于软件multisim10.0.1进行仿真,在电机楼实验室20XX5进行验证。 三、设计要求 1、熟悉74Ls161,74Ls151,数码管的工作原理。 2、设计相应的电路图,标注元件参数,并进行仿真验证。 四、设计内容 1.电路原理图(含管脚接线)电路原理图如图1所示 图1电路原理图 2.计算与仿真分析

仿真结果如图2、3、4所示 图2仿真结果 图4仿真结果 4.调试流程 调试流程如图5所示 图5调试流程 5.设计和使用说明 74Ls151芯片为互补输出的8选1数据选择器,引脚排列如图6所示,功能见表1。选择控制端(地址端)为c~A,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Y,g为使能端,低电平有效。 (1)使能端g=1时,不论c~A状态如何,均无输出(Y=0,w=1),多路开关被禁止。 (2)使能端g=0时,多路开关正常工作,根据地址码c、b、A的状态选择D0~D7中某一个通道的数据输送到输出端Y。如:cbA=000,则选择D0数据到输出端,即Y=D0。如:cbA=001,则选择D1数据到输出端,即Y=D1,其余类推。 图674Ls151引脚排列 表174Ls151功能表 74Ls161功能: (1)异步置“0”功能:接好电源和地,将清除端接低

电平无论其他各输入端的状态如何,测试计数器的输出端,如果操作无误Q3~Q0均为0。 (2)预置数功能:将清除端接高电平,预置控制端接低电平,数据输入端D3~D0置0011,在cp的上升沿作用后,测试输出端Q3~Q0的电平。如果操作准确,D3~D0的数据为0011,说明D3~D0的数据已预置到Q3~Q0端。 (3)计数和进位功能:将LD、cr、ceT、cep端均接高电平,cLK端输入单脉冲,记录输出端状态。如果操作准确,每输入一个cp 脉冲,计数器就进行一 篇二:课程设计报告---七人表决器设计 电子综合设计 题目 学院 专业 班级学生姓名指导教师 七人抢答器设计计信学院电子信息工程 20XX年6月18日 一、设计原理 所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。七人表决器顾名思义就是由七个人

七人表决器实验

3.3实验三七人表决器设计 3.3.1实验目的 1、掌握用QuartusII软件设计基本数字系统流程及注意事项。 2、进一步熟练掌握程序的编译、仿真、生成模块及芯片引脚号码锁定方法。 3、掌握分层设计的方法和注意事项 4、在实验报告中,总结数字系统设计步骤及注意事项。 3.3.2实验内容 基于QuartusII软件及VHDL语言实现七人表决器。当参与表决的7人中有4个或4个以上赞同时,表决器输出“1”表示通过,否则输出“0”表示不通过,并显示赞成和反对的人数。用7个开关作为表决器的7个输入变量,数码管显示人数,LED灯显示是否通过。 本实验4学时。 3.3.3实验仪器 ZY11EDA13BE型实验箱。 3.3.4实验原理 分析实验要求,七人表决器系统主要由两个模块构成:投票计数模块和数码管显示模块。 一、建立项目 (1)新建文件夹。路径及文件名中不可出现汉字。 (2)新建项目。一个数字系统可以由多个模块构成,使所有模块连接在一起的总文件叫做顶层文件,只有顶层文件名可以且必须与项目名相同。项目取名为bjq7。 (3)选择芯片

二、建立文件 首先,建立各个VHDL功能模块。 1.投票计数模块。 (1)新建VHDL文件 编辑VHDL程序。投票计数模块输入为七个电平开关input,输出为同意的人数agree,反对的人数disagree,是否通过指示灯y,程序清单如下: library ieee;

use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity BJQ is port(input:in std_logic_vector(6downto0);七个输入开关agree:out std_logic_vector(3downto0);同意的人数 disagree:out std_logic_vector(3downto0);不同意的人数 y:out std_logic);是否通过标志 end; architecture one of BJQ is begin process(input) variable cnt:integer range0to7; variable cnt0:integer range0to7; begin cnt:=0; for i in6downto0loop if input(i)='1'then cnt:=cnt+1; end if; end loop; cnt0:=7-cnt; if cnt>3then y<='0'; else y<='1'; end if; case cnt is when0=>agree<="0000"; when1=>agree<="0001"; when2=>agree<="0010"; when3=>agree<="0011"; when4=>agree<="0100"; when5=>agree<="0101"; when6=>agree<="0110"; when7=>agree<="0111"; when others=>agree<="0000"; end case; case cnt0is when0=>disagree<="0000"; when1=>disagree<="0001"; when2=>disagree<="0010"; when3=>disagree<="0011"; when4=>disagree<="0100"; when5=>disagree<="0101"; when6=>disagree<="0110"; when7=>disagree<="0111";

eda实验报告

一位全加器 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; -- Uncomment the following lines to use the declarations that are -- provided for instantiating Xilinx primitive components. --library UNISIM; --use UNISIM.VComponents.all; entity adder is port(a,b,cin:in std_logic; co,so:out std_logic); end adder; architecture Behavioral of adder is signal temp1,temp2:std_logic; begin temp1<= a xor b; temp2<= temp1 and cin; so<= temp1 xor cin; co<= temp2 OR (a AND b); end Behavioral; 四位全加器 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; -- Uncomment the following lines to use the declarations that are -- provided for instantiating Xilinx primitive components. --library UNISIM; --use UNISIM.VComponents.all; entity counter10 is

三人表决器实验

三人表决器实验 我们实验采取3种输入方式:原理图方式,VHDL方式,VerilogHDL.你可以只看一种.下面我分别一一介绍 三人表决器的功能描述 三个人分别用手指拨动开关SW1、SW2、SW3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方),不同意就把自己的指拨开关拨到低电平(下方)。表决结果用LED(高电平亮)显示,如果决议通过那么实验板上L2(黄灯)亮;如果不通过那么实验板上L1(红灯)亮;如果对某个决议有任意二到三人同意,那么此决议通过,L2亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1亮。 采用原理图设计三人表决器 我们根据三人表决器的直值表,可以通过卡诺图化简可以得到: L2=SW1SW2+SW1SW3+SW2SW3 L1=_L2 那么我们可以在MAX+plusII中用原理图实现上面的三人表决器 ~ 下面仅把和VHDL不同的详细写下,相同或基本相同的就一带而过: (1)打开MAX+plusII (2)新建一个图形文件:File菜单>new 新建文件时选择Graphic Editor file

点OK (3)输入设计文件 我们现在在图形文件中输入电路,我们这个电路需要AND2、OR3、NOT三个逻辑门电路和输入输出端,你可以 Symbol ->Enter Symbol(或者双击空白处) 弹出窗口: %

在Symbol Name中输入and2,点OK 同样可以加入or3、input、output、not 对input、output,鼠标左键双击PIN_NAME,那么PIN_NAME被选中,并且变黑,然后输入你要改的名字,如SW1 把元件拖动到合适位置,将光标放到元件的引线出,可以发现光标变为十字星,此时摁住左键就可以进行连线。

课程设计试验报告三人表决器

武汉纺织大学《数字逻辑》课程设计报告 题目:三裁判表决器 院系:数学与计算机学院 专业班级:计科094 学号:0904681223 学生姓名:李勤 指导教师:朱勇 2011年 5 月20 日

一、 引言 通过对传统数字电路的设计,掌握对数字逻辑设计概念的熟悉。 二、系统介绍: 主要仪器是TOS-2数字电路实验系统。选用的芯片是74LS151 8-1数据选择器。通过设计好的逻辑表达式,在TOS--2数字电路上选择好个个需要连入的拐脚,进行连线。实现三人表决器的功能。 三、设计任务及设计原理: 引脚图 功能表 设计有三个变量输入A ,B C ,二个输出 W ,F,其中F=W , 逻辑表达式: F=ABC C AB C B A BC A +++。A,B,C 通过三个开关相接,把D0---D7设置好之后, 16 15 14 13 12 11 10 9 74LS151 1 2 3 4 5 6 7 8V CC D 4 D 5 D 6 D 7 A 0 A 1 A 2D 3 D 2 D 1 D 0 Y Y S GND 输 入输 出D A 2 A 1 A 0 S Y Y × × × × 1D 0 0 0 0 0 D 1 0 0 1 0 D 2 0 1 0 0D 3 0 1 1 0D 4 1 0 0 0D 5 1 0 1 0D 6 1 1 0 0D 7 1 1 1 00 1D 0 0D D 1 1D D 2 2D D 3 3D D 4 4D D 5 5D D 6 6D D 7 7D

就可以通过调节开关来输入。输出接到一个LED灯,如果通过,那么灯就亮,否则的话,灭。 74LS151 0 G A A B B C C D0 D1 Y Y 0 D3 D3 W D4 1 D5 D6 D7 方法之一 四、代码清单:(机房答辩,提交代码) 只需要连线,无代码。 五、程序调试心得体会: 第一次线连接好之后,首先试验的是逻辑功能的正确性。用了两个LED灯,来作为输出,三个开关组合成A,B,C的八种状态。确保正确性之后,在进行的验证三人表决器。试验顺利,没有遇到困难。 六、参考文献: [1] 朱勇,数字逻辑,中国铁道出版社,2007.12 [2] 夏宇闻,Verilog DHL 入门,北京航空大学出版社,2007.5 七、致谢:感谢同学袁盼的一起合作,在连线过程中遇到问题时,一起商量。

EDA技术基础实验报告

EDA技术基础实验报告 学院:信息科学与技术学院 班级: 姓名: 学号:

实验一 MAX—plusII及开发系统使用 一、实验目的 1、熟悉利用MAX-plusⅡ的原理图输入方法设计简单的组合电路 2、掌握层次化设计的方法 3、熟悉DXT-BⅢ型EDA试验开发系统的使用 二、主要实验设备 PC 机一台(中档以上配置),DXT-B3 EDA实验系统一台。 三、实验原理 数字系统设计系列实验是建立在数字电路基础上的一个更高层次的设计性实验。它是借助可编程逻辑器件(PLD),采用在系统可编程技术(ISP),利用电子设计自动化软件(EDA),在计算机(PC)平台上进行的。 因为本实验是在计算机平台上进行,因此实验方式,实验手段和实验仪器与传统的实验有很大的区别,主要体现在以下几个方面: 1、实验器材集中化,所有实验基本上在一套实验设备上进行。 传统的实验每作完一个实验,实验器材基本上都要变动(个别除外)。而做本实验时,只要在计算机上把不同的程序输进去,其它步骤所有实验都一致; 2、实验耗材极小(基本上没有耗材); 3、在计算机上进行,自动化程度高,人机交互性好,修改、验证实验简单; 4、下载后,实验结果清晰; 5、实验仪器损耗少,维护简单; 下面,就本套实验设备做一个简单的介绍。 1、Max+PlusII软件的安装步骤: 第一步:系统要求 奔3CPU以上,128M内存以上,4G 以上硬盘,98 操作系统(98或Me操作系统才可以下载,其他操作系统下载必须安装驱动,否则只能仿真,如果只是进行仿真的话,对系统没要求) 第二步:安装 点击安装可执行文件进行安装,安装完毕后会弹出一对话框,点击是或否都可以。 第三步:将安装文件夹中的License 文件夹打开,里面有一个License.bat 注册文件,

三人表决器实验报告

电子技术与仿真 项目报告 项目名称:三人表决器的制作 专业班级:电气1 2 1 姓名:刘斌 学号: 2 4 指导教师:张琴 江西工业工程职业技术学院电工电子实训中心

一、项目目的 正确理解数字电路的要求,能知道与门、或门、非门的含义;做到了解要用到的每个芯片的引脚是什么门电路,可以去图书馆查阅书籍也可上网去阅读相关的网页资料。做到能真正了解电路的构造原理,这样才可以更好学好这门电路的元器件的应用。 二、项目要求 1)判断正确的引脚位置; 2)理解数字电路的原理,掌握操作步骤,能正确安装所选定的电路; 3)掌握测试仪表仪器检测原件的使用及调整; 4)会根据测试结果分析故障产生的原因; 5)会利用原理图纸,判断具体故障的原因; 6)必须得出实验的仿真结果; 7)根据自己所仿真的电路原理图画出实物装配图。 三、项目内容 1、原理图 2、工作原理介绍 电路由74LS08的三个与门电路和74LS32两个或门电路构成,当A、B、C中任意两人按下按钮后,工作电路向74ls08中任意一个与门电路输入端输入两个高电平,输出端Y输入进74ls32任意一个或门电路中;电路只要满足一个条件即输出端有电压输

出;所以发光二极管能点亮。 3、元件清单 4、芯片 ① 74LS08 实物图 引脚图 真值表 元件序号 主要参数 数 量 R1 1K Ω 3 R2 360Ω 1 U1 74LS08 1 U2 74LS32 1 按钮开关 3 发光二极管 1 A B Y 0 0 0 0 1 0 1 0 0 1 1 1

实物图引脚图 真值表 5、电路板安装 A B Y 000 011 101 111

四人表决器电路设计

名称:综合训练项目一题目:四人表决器电路设计 专业: 班级: 姓名: 学号: 辽宁工程技术大学 《数字电子技术》 综合训练项目一成绩评定表

《综合训练项目一》任务书 一、综合训练题目 四人表决器电路设计 二、目的和要求 1、目的:会运用不同类型门电路或中、小规模集成电路,设计简单组合电路,学习仿真软件应用,学习word文档制作。 2、要求:设计一个四人表决器,按少数服从多数规则,三人或三人以上同意,则通过。利用绿、红两种颜色灯代表是否通过,并用数码管显示同意人数;用门电路或中规模集成电路译码器、数选器、加法器等完成控制任务;有研究方案比较,能够应用相关仿真软件绘制逻辑图,用仿真软件验证电路功能。 成果形式:每小组提交综合训练报告一份;现场或视频答辩;有能力的同学制作实物。 上交时间:在讲授完第四章中的组合电路设计知识点后的一周之内提交。 三、训练计划 项目综合训练课下1周,课上1节。 第1天:针对选题查资料,确定整体设计方案; 第2~3天:学习Multisim仿真软件,熟悉Visio绘图软件。 第4~5天:论证电路设计,利用仿真软件仿真设计电路,观察能否达到设计要求;; 第6~7天:按格式要求编写整理设计报告。 四、设计要求 1. 每名同学按照自己分配的任务要求完成训练。 2. 绘图统一采用Visio2010。 指导教师: 日期:2017 年月 日

四人表决器在我们生活中应用非常广泛,比如表决等。掌握四人表决器的工作原理,对我们理解和掌握表决器具有重要意义。 本次的课程设计就是利用数字电子技术的知识做一个四人表决器。在mulitisim软件中,利用集成电路,通过四片74LS183和一片74LS48芯片连接到LED数码管上,一个显示赞成人数;再通过与门和非门,实现通过与否的判决。经过仿真,符合四人表决的功能。 关键词:四人表决器;74LS183;74LS84;LED数码管

EDA实验报告

一MAX –plusII及开发系统使用 一、实验目的 1、熟悉利用MAX-plusⅡ的原理图输入方法设计简单的组合电路 2、掌握层次化设计的方法 3、熟悉DXT-BⅢ型EDA试验开发系统的使用 二、主要实验设备 PC 机一台(中档以上配置),DXT-B3 EDA实验系统一台。 三、实验原理 数字系统设计系列实验是建立在数字电路基础上的一个更高层次的设计性实验。它是借助可编程逻辑器件(PLD),采用在系统可编程技术(ISP),利用电子设计自动化软件(EDA),在计算机(PC)平台上进行的。 因为本实验是在计算机平台上进行,因此实验方式,实验手段和实验仪器与传统的实验有很大的区别,主要体现在以下几个方面: 1、实验器材集中化,所有实验基本上在一套实验设备上进行。 传统的实验每作完一个实验,实验器材基本上都要变动(个别除外)。而做本实验时,只要在计算机上把不同的程序输进去,其它步骤所有实验都一致; 2、实验耗材极小(基本上没有耗材); 3、在计算机上进行,自动化程度高,人机交互性好,修改、验证实验简单;

4、下载后,实验结果清晰; 5、实验仪器损耗少,维护简单; 下面,我们就本套实验设备做一个简单的介绍。 (一)Max+plusⅡ10.0的使用。 1、Max+PlusII软件的安装步骤: 第一步:系统要求 奔3CPU以上,128M内存以上,4G 以上硬盘,98 操作系统(98或Me操作系统才可以下载,其他操作系统下载必须安装驱动,否则只能仿真,如果大家只进行仿真的话,对系统没要求) 第二步:安装 点击安装可执行文件进行安装,安装完毕后会弹出一对话框,点击是或否都可以。 第三步:将安装文件夹中的License 文件夹打开,里面有一个License.bat 注册文件,将此文件复制到你的安装目录下(你的安装目录可放在任一个驱动器下,然后建立一个Max10的文件夹,将系统安装在此文件夹中,安装后此文件夹中会有三个文件夹)的任一个文件夹中,要清楚位置。 第四步:注册 启动Max+PlusII 软件,可以从开始-->程序-->Altera-->Max+PlusII 打开,也可以建立一个快捷方式在桌面上。启动软件后, 会有弹出一个对话框,点击是或否都可以,然 后进入系统。点击菜单中的Options,然后选 中License菜单项,打开弹出一个注册对话框, 在注册文件路径中打开你第三步中复制位置的 License 文件,然后点击OK,注册完毕。 2、 max+plusⅡ软件基本设计流程