第6章 定时器相关模块

第6章定时器相关模块

本章导读:本章讲述了计数器/定时器的一般工作原理,介绍K60N512的定时接口模块(PDB、 FTM、PIT、LPTMR、CMT和RTC )的基本功能与编程基础,并给出具体的例子,读者要仔细体会各种不同的使用方法,并将这些方法运用到具体的应用中。本章知识点有①计数器/定时器的工作原理;②可编程延时模块PDB;③Flex定时器FTM;④周期中断定时器PIT;

⑤低功耗定时器LPTMR;⑥载波调制传输接口 CMT;⑦实时时钟RTC。

6.1计数器/定时器的基本工作原理

在嵌入式应用系统中,有时要求能对外部脉冲信号或开关信号进行计数,这可通过计数器来完成。有些设备要求每间隔一定时间开启并在一段时间后关闭,有些指示灯要求不断地闪烁,这可利用定时信号来完成。个人计算机也经常要用到定时信号,如系统日历时钟的计时、产生不同频率的声源等。在计算机系统屮,计数与定时问题的解决方法是一致的,只不过是同一个问题的两种表现形式。

实现计数与定时的基本方法有三种:完全硬件方式、完全软件方式、可编程计数器/定时器。

1.完全硬件方式

在过去的许多仪器仪表或设备中,需要进行延时、定时或计数,经常使用数字逻辑电路实现, 即完全用硬件电路实现计数/定时功能,若要改变计数/定时的要求,必须改变电路参数,通用性和灵活性差。在微型电子计算机出现以后,特別是随着单片微型计算机的发展与普及,这种完全硬件方式实现定时与计数的方法已较少使用。

2.完全软件方式

在计算机中,通过编程利用计算机执行指令的时间实现定时,称为完全软件方式,简称软件方式。在这种方式中,一般是根据所需要的时间常数来设计一个延时子程序,延时子程序中包含一定的指令,设计者要对这些指令的执行时间进行精确的计算和测试,以便确定延时时间是否符合要求。当时间常数比较大时,常常将延时子程序设计为一个循环程序,通过循环常数和循环体内的指令来确定延时时间。这样,每当延时子程序结束以后,可以直接转入下而的操作,也可以用输出指令产生一个信号作为定时输出。这种方法的优点是节省硬件。主要缺点是执行延时程序期间,CPU一直被占用,所以降低了CPU的使用效率,也不容易提供多作业环境;另外,设计延时子程序时,要用指令执行时间来拼凑延时时间,显得比较麻烦。不过,这种方法在实际应用中还是经常使用的,尤其是在已有系统上作软件开发时,以及延时时间较小而重复次数又较少的情况。在计算机控制软件开发过程中,作为粗略的延时,经常使用软件方法来实现定时。

3.可编程计数器/定时器

利用专门的可编程计数器/定时器实现计数与定时,克服了完全硬件方式与完全软件方式的缺点,综合利用了它们各自的优点,其计数/定时功能可由程序灵活地设置,设定之后与CPU 并行地工作,不占用CPU的工作时间。应用可编程计数器/定时器,在简单的软件控制下,可以产生准确的时间延时。这种方法的主要思想是根据需要的定时时间,用指令对计数器/定时器设置定时常数,并用指令启动计数器/定时器开始计数,当计数到指定值时,便自动产生一个定时输出。在计数器/定时器开始工作以后,CPU不必去管它,而可以去做其他工作。这种方法最突出的优点是计数时不占用CPU的时间,如果利用计数器/定时器产生中断

信号还可以建立多作业的环境,所以可大大提高CPU的利用率。加上计数器/定时器本身的开销并不很大,因此这种方法在微机应用系统中得到了广泛的使用。

K60的定时器接口模块包括了六个子模块:可编程延迟模块PDB、Flex定时器模块FTM、周期中断定时器模块PIT、低功耗定时器模块LPTMR、载波调制发射器模块CMT,以及实时时钟模块RTC。下面逐个介绍这几个模块。

6.2可编程延迟模块PDB

6.2.1P D B的基础知识

可编程延迟模块(Programmable Delay Block, PDB)可以提供从内部/外部触发源、可编程间隔到A/D转换(Analog To Digital Convert, ADC)的硬件触发,也可以提供D/A转换模块(Digital-to-Analog Converter, DAC)间隔触发的可控时延,这样就可以为ADC转换和DAC输出提供精确的时间。由于本章涉及ADC与DAC的内容,读者可以先阅读后面的章节再进行本节的学习。另外,PDB模块还可以选择性提供脉冲输出。

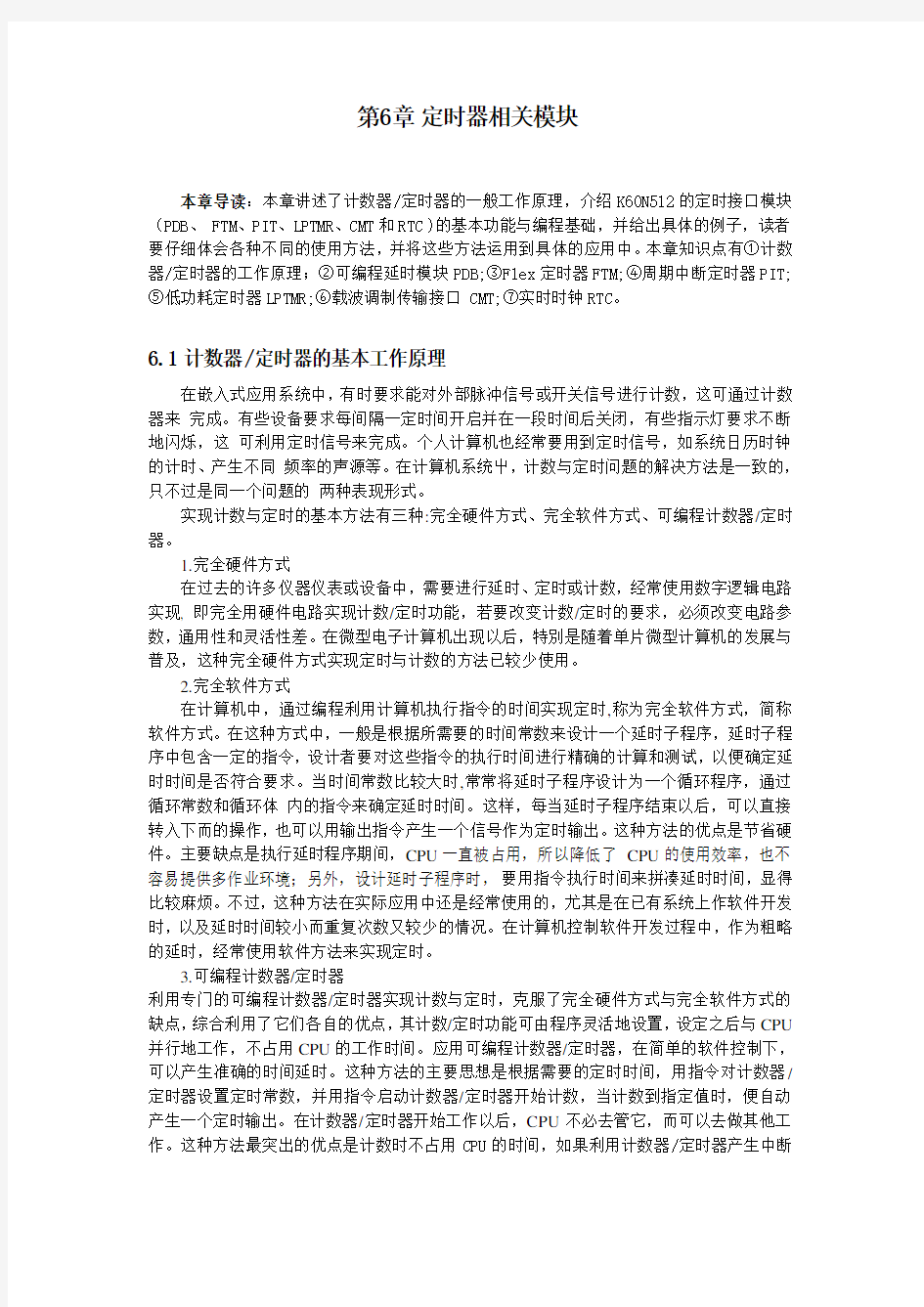

PDB模块包含高达15种输入触发中断源和软件触发中断源、8路的可配置用于ADC触发的PDB通道、8路的DAC内部触发源和8路的脉冲输出。PDB结构框图如图6-1所示。

在图中,只显示了PDB通道n,DAC间隔触发器x以及脉冲输出y (用虚线框表示),没有显示PDB使能控制逻辑与时序错误中断逻辑。

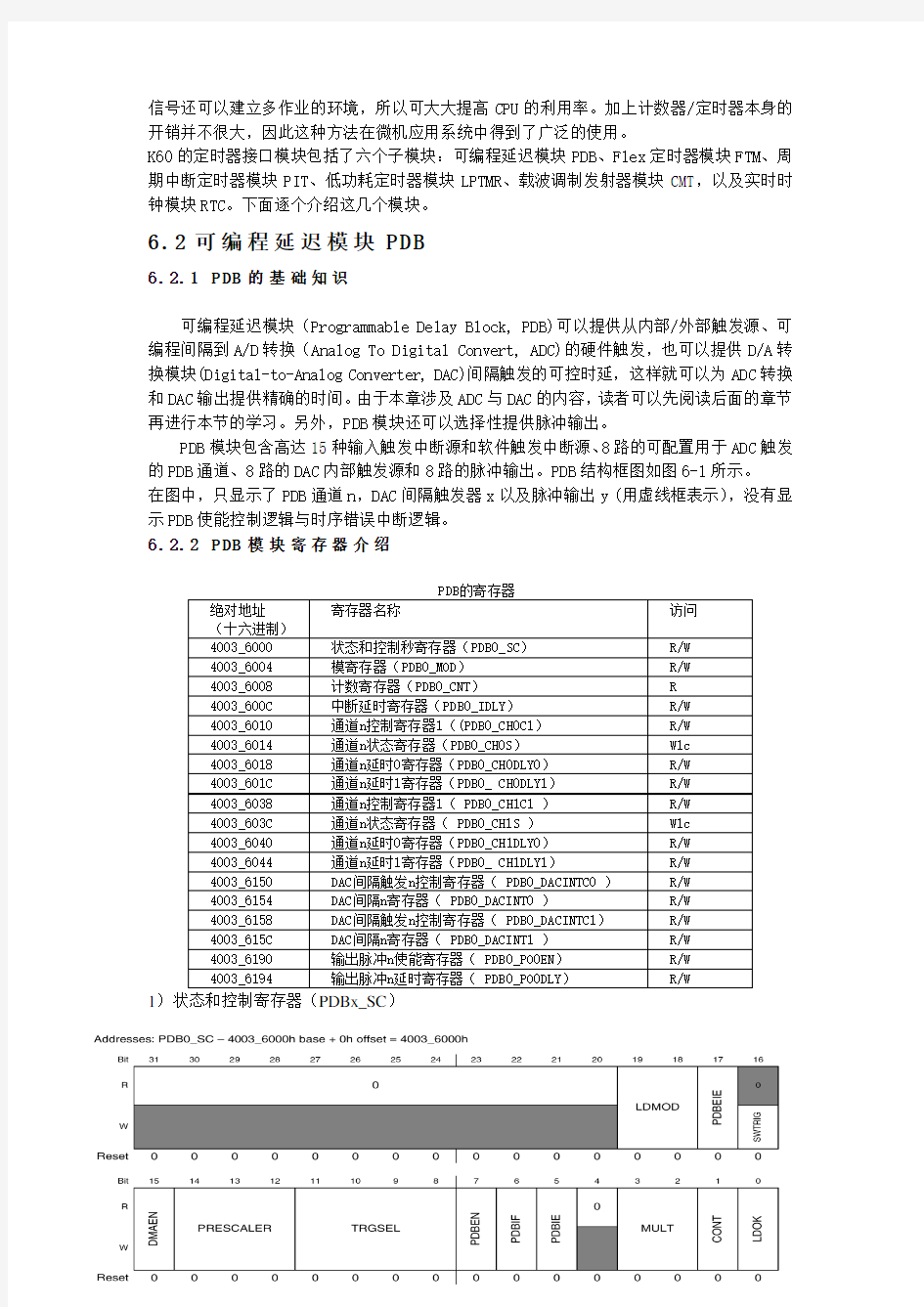

6.2.2P D B模块寄存器介绍

1)状态和控制寄存器(PDBx_SC)

2)模寄存器(PDBx_MOD)

PDBx_MOD位寄存器

位描述

31-16:预留预留,只读,值为0

4)中断延时寄存器(PDBc_IDL Y)

5)通道n控制寄存器1(PDBx_CHnC1)

每个PDB通道都有一个控制寄存器——CHnC1,用来控制每个PDB通道的功能。

6)通道n状态寄存器(PDBx_CHnS)

8)通道n延时1寄存器(PDBx_CHnDL Y1)

功能同通道n延时0寄存器,不再赘述。

9)DAC间隔触发器n控制寄存器(PDBx_DACINTCn)

10)DAC间隔n寄存器(PDBx_DACINTn)

11)脉冲输出n使能寄存器(PDBx_POnEN)

12)脉冲输出n延时寄存器(PDBx_POnDL Y)

6.2.3 PDB模块概要与编程要点

1.PDB输入触发源选择

PDB有多达15个输入触发源,叫做Trigger-In 0?14,在图6-1中可以看到,它们与

片上或片下事件源相连。通过PDB状态控制寄存器SC的软件触发位(SWTRIG)可以将PDB 设置为软件触发,通过SC的输入触发源选择位域(TRIGSEL)可以使能触发输入源Trigger-In 0到14 中的某一个,或者是软件触发。SC[TRIGSEL]的取值范围为0000?1111,其中0000?1110对应触发源Trigger-In 0到14,1111对应软件触发。详细信息参见本章阅读材料。

2. DAC间隔触发器输出

PDB可以产生间歇的触发,周期性的更新DAC输出。当产生输入触发事件且DACINTCx[EXT] 等于零时,复位DAC间隔计数器x并重新开始计数。当间隔计数器x的值等于DACINTx寄存器设置的值时,DAC间隔触发器x会输出一个脉冲来更新DACx,该脉冲的脉宽等于一个外设时钟周期。如果置位DACINTCx[EXT],将旁路DAC间隔计数器,而且在检测到DAC外部输入触发有上升沿之后,DAC间隔触发器x会输出一个脉冲。清位DACINTCx[TOE]将禁止DAC 间隔计数器和DAC间隔触发器。当PDB计数器等于PDB模寄存器MOD的值时,复位DAC间隔计数器。因此当PDB计数器归零时,DAC间隔计数也会重新开始。在图6-1可以看到DAC间隔触发输出框图。

3.脉冲输出

PDB可以输出宽度可配置的脉冲。当PDB计数器的值等于PDB脉冲输出y延时寄存器DLY1的值时,脉冲输出为高;当计数器达的值等于PDB脉冲输出y延时寄存器DLY2的值时,脉冲输出为低。由图6-1也可以看到脉冲输出框图。

图6-1 PDB结构框图

6.2.3 PDB构件设计及测试实例

(省略)

6.3 Flex定时器FTM

6.3.1 FTM的基础知识

弹性定时器模块(FlexTimer Module, FTM)是一个支持输入捕捉、输出比较、产生可用来控制电机的PWM信号和电源管理应用的通道定时器。它建立在飞思卡尔8位微控制器HCS08 定时器PWM模块——TPM上,并且在低功耗和向后兼容TPM的基础上进行功能扩展,增加了有符号的加法计数器、故障控制输入、增强了触发功能和极性控制来满足电机控制、

电源转换等的需要。所有与TPM模块相同的特性完全向后兼容,FTM在相同的核心平台下不需要对代码做任何改变就可以实现相同的功能。

FTM具有可选的时钟源,可以是系统时钟、固定频率时钟或者外部时钟;具有1、2、4、8、16、32、64、128预分频;一个可以进行无符号或有符号计数的16位计数器,为FTM提供定时参考;每一个通道都可配置为输入捕捉、输出比较或者边缘对齐的PWM模式;每个通道的极性都可以配置,并产生溢出中断、通道中断、故障中断等中断。当TOIE=l 且TOF=l 时,产生定时器溢出中断,当ChnIE=l且CHnF=l时,产生通道(n)中断,当FAULTIE=1且FAULTF=1时,产生故障中断。图6-2显示了 FTM模块结构,其中心组件为16位计数器。

6.3.2 FTM模块寄存器介绍

FTM寄存器非常多,我们这里只列举常用的8个。

1)状态和控制寄存器(FTMx_SC)

SC包含溢出状态标志和控制位,用来配置中断使能、FTM配置、时钟源和预分频因子。这些控制和这个模块的所有通道相关。

2)计数器(FTMx_CNT)

CNT寄存器包含FTM计数器的值。复位清CNT寄存器,写任何值到COUNT中会将计数器更新为它的初始值(CNTIN),当激活BDM时,FTM计数器冻结。

3)模寄存器(FTMx_MOD)

模寄存器包含FTM计数器的模值。FTM计数器达到模寄存器的值后,在下个时钟周期置位溢出标志(TOF),FTM计数器的下一个值取决于所选的计数方式。

写MOD寄存器会将值锁存到缓冲区中,MOD寄存器会根据写缓冲区中的值更新寄存器。

如果FTMEN=0,通过写SC寄存器可能复位写一致机制,推荐在写MOD寄存器之前初始化FTM计数器。

FTMx_MOD位域描述

位描述

31-16:预留预留,只读,值为0

15-0:MOD 模值

4)通道n状态和控制寄存器(FTMx_CnSC)

CnSC包含了通道中断状态标志和控制位,用于配置中断使能、通道配置和引脚功能。

5)通道n值寄存器(FTMx_CnV)

这些寄存器包括了输入捕捉模式下捕捉的FTM计数器的值或者输出比较模式下的匹配值。在输入捕捉、捕捉测试和双边沿捕捉模式,写CnV无效。在输出比较模式下,写CnV 寄存器将会把写入的值装载到缓冲中。

该寄存器包括FTM计数器的初始值,写该寄存器会将值装载到缓冲区中。

7)捕捉和比较状态寄存器(FTMx_STA TUS)

该寄存器包括了对每个FTM通道的状态标志CHnF位的副本。通过读该寄存器可以得到所有通道的CHnF位的值。写0x00到该寄存器可以清掉所有的CHnF位的值。当通道上有事件发生时,硬件会使响应的通道标志置位。当CHnF被置位时,读该寄存器可以清CHF。写1到CHF无效。

8)特性模式选择寄存器(FTMx_MODE)

这个寄存器包含用来配置出错中断和出错控制的控制位,捕捉测试模式,PWM同步化,写保护,通道输出初始化,和使FTM加强的特性。这些控制与该模块内的所有通道有联系。

6.3.3 FTM模块概要与编程要点

本小节具体阐述FTM各个模块的特征,由于版面有限,这里只列举了常用的几个模块。

1.计数时钟源与分频

FTM状态和控制寄存器(FTMx_SC)的CLKS[1:0]位用于选择FTM计数器的时钟源,CLKS[1:0]=00表示没有选择任何时钟,相当于关闭FTM计数器,CLKS[1:0]=01表示系统时钟源,CLKS[1:0]=10(固定频率时钟),CLKS[1:0]=11(外部时钟)。MCU复位后,CLKS[1:0]=00,关闭FTM计数器。选择的时钟源的分频因子由FTM状态和控制寄存器(FTMx_SC)的PS[2:0]位决定,PS[2:0]=000 (1分频),PS[2:0]=001 (2分频),PS[2:0]=010 (4分频),PS[2:0]=011 (8分频),PS[2:0]=100 (16分频),PS[2:0]=101 (32分频)。

2.计数器

FTM有一个16位计数器,供通道使用,计数器的操作主要有向上计数与向上向下计数。向上计数:当FTM正交解码控制和状态寄存器(FTMx_QDCTRL)的正交解码模式使能位QUADEN=0且FTM状态和控制寄存器(FTMx_SC)的中央对齐PWM选择位CPWMS=0时向上计数,CNTIN定义了计数起始值,MOD定义了计数的最终值。如图6-2所示,FTM计数器先加载CNTIN 值,然后开始计数,直到达到MOD值,然后计数器重新加载CNTIN值,重复以上步骤。如果CNTIN=0x0000,FTM计数和TPM向上计数一样,即向上无符号计数,如果 CNTIN[15]=1,FTM是向上有符号计数,如果CNTIN (15) =0 且 CNTIN 0x0000, FTM也是向上无符号计数。

向上向下计数:当QUADEN=0且CPWMS=1时,向上向下计数。CNTIN定义了计数起始值,MOD定义了计数的最终值。同向上计数一样,FTM计数器先加载CNTIN值,然后开始计数,直到达到MOD值,但是不同于向上计数,此时计数器执行减数操作,直到它回到CNTIN值,上下计数重新开始。

FTM模块除了以上操作外还可以有以下三个常用的模块。

输入捕捉:输入捕捉功能主要用来监测外部的事件和输入信号。当外部事件发生或信号发生变化时,在指定的输入捕捉引脚发生一个指定的沿跳变(由FTMx_CSC寄存器的ELSnB 和ELSnA域指定是上升沿还是下降沿,具体内容参见本章阅读资料)。定时器捕捉到特定的沿跳变后,会把计数寄存器当前的值锁存到通道寄存器。如果在输入捕捉控制寄存器中设定允许输入捕捉中断,系统会产生一次输入捕捉中断,利用中断处理软件可以得到事件发生的时刻或信号发生变化的时刻。

输出比较:输出比较的功能是用程序的方法在规定的时刻输出需要的电平,实现对外部电路的控制。当定时器的某一通道用做输出比较功能时,通道寄存器的值和计数寄存器的值每隔一定时间比较一次。当两个值相等时,输出比较模块置定时器通道n状态和控制寄存器(FTMx_CnSC)的CHnF位为1,并且在该通道的引脚上输出预先规定的电平。如果输出比

较中断允许,还会产生一个中断。

PWM:脉宽调制器(Pulse Width Modulator,PWM)产生一个在高电平和低电平之间重复交替的输出信号,这个信号被称为PWM信号,也叫脉宽调制波。通过指定所需的时钟周期和占空比来控制高电平和低电平的持续时间。通常定义占空比为信号处于高电平的时间(或时钟周期数) 占整个信号周期的百分比,方波的占空比为50%。脉冲宽度是指脉冲处于高电平的时间;PWM 分为以下三类。

(1)边沿对齐PWM (Edge-Aligned PWM)。所有PWM信号的边沿在周期的开始对齐,如图6-3所示。EPWM周期period由MOD寄存器和CNTIN寄存器的值决定(具体计算公式为MOD - CNTIN + 0x0001 ),脉冲宽度pulse width(占空比)由CnV寄存器和CNTIN寄存器的值决定(具体计算格式为CnV-CNTIN)。

图6-3边沿对齐P W M

(2)中央对齐 PWM (Center-Aligned PWM)。如图6-4所示,CPWM周期由2*(MOD-CNTIN)决定,脉冲宽度(占空比)由2?(CnV-CNTIN)决定,MOD必须在0x0001到0x7FFF内。

图6-4中央对齐P W M

(3)通道合并模式。通道n(一个偶数通道)和通道n+l(相邻的奇数通道)合并到通道n输出一路PWM信号。周期由(MOD-CNTIN+OxOOOl)决定,PWM脉冲宽度(占空比)由(C(n+l)V-C(n)V)的绝对值决定,其中C(n)V为通道n的CV寄存器值。

3.信号描述

FTM模块有六种用户访问信号线,具体描述见表6-1。

表6-1F T M用户访问信号线

信号描述I/O

E X T C L K外部时钟,用于驱动FTM计数器,外部时钟信号不能超过系统时钟频

I 率的1/4

I/O

C H n FTM通道n,n为7?0,每个通道都可被配置为输入或者输出,通道的

方向由模式决定

故障输入j,j为3?0,如果FTMEN=1,FALUTM[1:0]≠0,则使能故障

F A U L T j控制。FTM有4种故障输入,FAULTnEN位使能故障输入n,FFLTRnEN

位使能故障输入n滤波器,FFV AL[3:0]位选抒每个故障输入的滤波器

的值

I

P H A 如果FTMEN=1且QUADEN=1,选择正交解码器模式,正交解码器模

式使用输入信号相A和相B控制FTM计数器的增加和减少。通过PHAFLTREN位使能相A输入过滤器,且这个过滤器的值在FILTER0 寄

存器的CH0FV AL[3:0]位定义

I

P H B 正交解码器B相输入,控制FTM计数器增加或者减少的信号。通过PHBFLTREN位使能相B输入过滤器,且这个过滤器的值在FILTER0

寄存器的CH1FV AL[3:0]位定义

I

6.3.3F T M构件设计及测试实例

省略

6.4 周期中断定时器PIT

6.4.1P I T的基础知识

周期中断时器模块(Periodic Interrupt Timer,PIT)是一组可以用于产生中断和触发DMA 通道的定时器。所有的中断都是可屏蔽的,每个定时器都有独立的溢出周期,此外,周期中断定时器模块没有外部引脚。图6-5为PIT模块的结构框图。

图6-5P I T模块的结构框图

6.4.2 PIT模块寄存器

在介绍可编程中断定时器PIT模块的编程方法之前,先简要介绍用于PIT模块的编程的几个寄存器:PIT模块控制寄存器(PIT_MCR),定时器加载值寄存器(PIT_LDV ALn),当前定时器值寄存器(PIT_CV ALn),定时器控制寄存器(PIT_TCTRLn)和定时器标志寄存

器(PIT_TFLGn)。

1)PIT模块控制寄存器(PIT_MCR)

这个寄存器控制定时器时钟是否使能和定时器是否运行在调试模式。

PIT_MCR域描述

域描述

31-2预留这个只读位域是预留的,并且始终为0。

1 MDIS 模块禁止

0 使能PIT定时器时钟。

1 禁用PIT定时器时钟。

0 FRZ 冻结

0 在调试模式下定时器继续运行。

1 在调试模式下定时器停止。

2) 定时器加载值寄存器(PIT_LDV ALn)

这些寄存器选择定时器中断的溢出周期。

PIT_LDV ALn域描述

域描述

31-0 TSV 定时器初始值字段

这些位设置定时器开始值。定时器将会倒计数直到为0,然后产生一个中断后再加载这个寄存器的值。向这个寄存器写入新值不会重启定时器,相反在定时器到期后才会加载新值。为了取消当前周期,以新值开始一个定时器周期,则必须先禁止定时器再使能定时器。

3) 当前定时器值寄存器(PIT_CV ALn)

这些寄存器指示当前定时器的位置。

PIT_CV ALn域描述域描述

31-0 TVL 当前定时器值

如果使能了定时器,这些位就代表了当前定时器的值。如果定时器被禁止了,不要使用这些位域的值,因为这些值是不可靠的。

4) 定时器控制寄存器(PIT_TCTRLn)

这些寄存器包括了每个定时器的控制位。

PIT_TCTRLn域描述域描述

31-2

预留

这个只读位域是预留的,始终为0。

1 TIE 定时器中断使能位。

0 来自定时器n的中断请求被禁止

1 不论TIF是否被设置,中断都会被请求

0 TEN

定时器使能位

0 定时器n禁止

1 定时器n有效

这些寄存器占有PIT中断标志。

PIT_TFLGn域描述域描述

31-1

预留

这个只读位域是预留的,始终为0。

0 TIF 定时器中断标志

0 超时不产生定时器中断。

1 超时发生定时器中断。

6.4.3P I T模块概要与编程要点

1.定时器

如图6-5所示,每个定时器都先从PIT寄存器中加载初始值,然后递减计数直到为0,接着再次加载初始值,重复以上步骤。每当定时器递减计数到0时,将产生一个脉冲触发并且置中断标志位。

通过设置定时器控制寄存器TCTRL (Timer Control Register)的屮断使能标志位TIE位,可以开启或屏蔽定时器通道中断。只有在旧中断被清除后,新中断才会产生。如果需要,可以通过当前定时器值寄存器CV AL读取定时器的当前计数器的值。重启计数周期时,先关闭定时器,然后置位TCTRL的定时器使能标志位TEN开启定时器,见图6-6。

图6-6 停止和开始定时器

如果要修改正在运行的定时器的计数周期,可以先关闭定时器,设置一个新的加载值,然后开启定时器来修改,见图6-7。

图6-7 修改运行着的定时器周期

此外,也可以不用重启定时器,而直接向定时器加载值寄存器LDV AL写入新值来改变计数周期。这个值将会在下一次触发事件后被加载,见图6-8。

图6-8 动态设置新的加载值

2.调试模式

在调试模式中,通过置位PIT控制寄存器中的FRZ位可以冻结定时器。这是为了在软件开发中,允许开发者停止定时器,查看系统的当前状态,然后继续操作。

3.中断

所有的定时器都支持中断。可以通过设置TIE位来使能定时器中断。在相关的定时器溢出中断发生时将置位定时器中断标志(TIF)。注意,中断处理除了要开定时器中断外还需要开对应的通道中断。

6.4.3P I T构件设计及测试实例

省略

6.5 低功耗定时器LPTMR

省略

6.6 载波调制发射器(CMT)

省略

6.7 实时时钟

6.7.1R T C基础知识

1. RTC简介

实时时钟(Real Time Clock, RTC)模块是一个独立供电的模块,在芯片掉电时由备用电源(VBAT)供电,确保RTC计时器正常运行,保持RTC寄存器状态。RTC模块主要包含一个外部晶体振荡器、一个POR(Power-On Reset)块、RTC计时器以及自身的软件复位控制位。外部晶体振荡器为RTC计时器或其他外设提供32.768 kHz的时钟;POR块在RTC模块上电时产生一个上电复位信号,将所有的RTC寄存器初始化为默认状态;RTC计时器由一个具有报警功能的32位秒寄存器和一个具有补偿功能的16位预分频寄存器组成;RTC自身的软件复位控制位,也会初始化所有的RTC寄存器。注意,在VBAT掉电或POR中断时,不允许访问RTC的任何寄存器(除了控制寄存器),否则将产生总线错误。

2.操作模式

RTC模块拥有两种操作模式,即系统掉电和系统上电。

在系统掉电期间,RTC由备用电源供电,与其他模块电气隔离,此时如果计时器使能,则继续计数,但是在此期间不可访问RTC寄存器。

在系统上电期间,RTC仍然由备用电源供电。在此期间可访问RTC的所有寄存器,并且可以为其他模块提供32.768 kHz的时钟。

3.信号描述

RTC模块共有三根信号线,其中一个作为输入,两个作为输出,具体描述见表6-3。

表6-3R T C信号描述

6.7.2R T C模块寄存器介绍

定时器、计数器操作与应用实验报告

实验三 定时器、计数器操作与应用实验报告 、实验目的 1、 了解和熟悉FX 系列可编程序控制器的结构和外 部接线方法; 2、 了解 和熟 悉 GX Developer Version 7.0 软件的 使用 方法 ; 3、 掌握 可编 程序 控制器 梯形 图程 序的 编制 与调 试。 二、实验要求 仔 细阅 读实 验指 导书 中关 于编 程软 件的 说明 ,复习 教材 中有 关内 容 , 分 析程 序运 行结 果。 三、实验设备 2 、 开关 量输 入 / 输出 实验 箱 3、 计算 机 4、 编程 电缆 注 意: 1) 开关量输入/输出实验 箱内的钮子开关用来产生模拟的 开关量输入 信 号; 2) 开关量输入/输出实验箱内的LED 用来指示开关 量输出信号; 3) 编程电缆在连接PLC 与计算机时请注意方向。 四、实验内容 1 、梯形图 1 、 FX 系列可 编程 序控 制器 一只 一套 5、 GX Developer Version 7.0 软件 一套

2、梯形图程序 0LD xooo 1OUT YOOO X001 2LD 3OR¥001 4AN I X002 5OUT Y001 6OUT TO K50 9MPS 10AHI TO 11OUT Y002 12MPP 13ASD TO 14OUT¥003 15LD X003 16RST CO 18LD X004 19OUT CO K5 22LD CO 23OUT Y004 24END 3、时序图

r 时序10 □ ?Si 正在进荷囲1SL 金冃勖厂手祜r XI广X3厂X5厂K1Q拧应C 40 J2fl MIB -380 .360 '340 -33 MW 脚 M 创Q,220,200,13Q -1?-14D ,1如■!? 如也 40 如厂「 五、实验步骤 1、程序的编辑、检查和修改; 2、程序的变换; 3、程序的离线虚拟设备仿真测试; 4、程序写入PLC; 5、用PLC运行程序; 6、比较程序的分析结果与实际运行结果。 六、实验报告 1、实验梯形图程序的编写; 2、梯形图程序的理论分析与结果; 3、梯形图程序的实际运行结果; 4、结论。 七、实验心得 通过这样一次实验,我对GX Developer Version 7.0 软件的使用方 法更加的熟悉了,也了解到在实验中需要我们集中精力,仔细认真地完成■XDU "Tlr-.Ll-t-1!- D LJ D-IT--1 z?E I4J 一 — Ti ll IL — 」 ill-t-ll-r — 1

单片机实验之定时器计数器应用实验二

一、实验目的 1、掌握定时器/计数器计数功能的使用方法。 2、掌握定时器/计数器的中断、查询使用方法。 3、掌握Proteus软件与Keil软件的使用方法。 4、掌握单片机系统的硬件和软件设计方法。 二、设计要求 1、用Proteus软件画出电路原理图,单片机的定时器/计数器以查询方式工作,设定计数功能,对外部连续周期性脉冲信号进行计数,每计满100个脉冲,则取反P1.0口线状态,在P 1.0口线上接示波器观察波形。 2、用Proteus软件画出电路原理图,单片机的定时器/计数器以中断方式工作,设定计数功能,对外部连续周期性脉冲信号进行计数,每计满200个脉冲,则取反P1.0口线状态,在P 1.0口线上接示波器观察波形。 三、电路原理图 六、实验总结 通过本实验弄清楚了定时/计数器计数功能的初始化设定(TMOD,初值的计算,被计数信号的输入点等等),掌握了查询和中断工作方式的应用。 七、思考题 1、利用定时器0,在P1.0口线上产生周期为200微秒的连续方波,利用定时器1,对 P1.0口线上波形进行计数,满50个,则取反P1.1口线状态,在P 1.1口线上接示波器观察波形。 答:程序见程序清单。

四、实验程序流程框图和程序清单。 1、定时器/计数器以查询方式工作,对外部连续周期性脉冲信号进行计数, 每计满100个脉冲,则取反P1.0口线状态。 汇编程序: START: LJMP MAIN ORG 0100H MAIN: MOV IE, #00H MOV TMOD, #60H MOV TH1, #9CH MOV TL1, #9CH SETB TR1 LOOP: JNB TF1, LOOP CLR TF1 CPL P1.0 AJMP LOOP END C语言程序: #include

器件实验报告八—555集成定时器及其应用

555集成定时器及其应用实验报告 一、实验内容与目的 1.单稳态触发器功能的测试,对于不同的外界元件参数,测定输出信号幅度和暂稳时间。 2.多谐振荡器功能的测试与验证,给定一个外界元件,测量输出波形的频率、占空比,并且计算理论值,算出频率的相对误差。 实验仪器: 自制硬件基础电路实验箱,双踪示波器,数字万用表,集成定时器NE555 2片;电阻100kΩ、10kΩ各2只;51kΩ、5.1kΩ、4.7kΩ各1只;电容30μF、10μF、0.1μF、2200pF各1只;电位器100kΩ1只; 元器件:LM555。 二、实验预习内容: 本实验旨在了解555定时器的内部结构和工作原理:单稳态触发器、多谐振荡器的工作原理。 实验资料: (1)构成单稳态触发器 电路如下图所示,接通电源→电容C充电(至2/3Vcc)→RS触发器置0→Vo =0,T导通,C放电,此时电路处于稳定状态。当2加入VI<1/3Vcc时,RS触发器置1,输出Vo=1,使T 截止。电容C开始充电,按指数规律上升,当电容C 充电到2/3Vcc时,A1翻转,使输出Vo=0。此时T又重新导通,C很快放电,暂稳态结束,恢复稳态,为下一个触发脉冲的到来作好准备。其中输出Vo脉冲的持续时间tw=1.1RC,一般取R=1kΩ--10MΩ,C>1000PF,只要满足VI的重复周期大于tp0 ,电路即可工作,实现较精确的定时。 (2) 多谐振荡器 电路如下图所示,电路无稳态,仅存在两个暂稳态,亦不需外加触发信号,即可产生振荡(振荡过程自行分析)。电容C在1/3Vcc--2/3Vcc之间充电和放电,输出信号的振荡参数为:

周期T=0.7 C(R1+2R2) 频率f=1/T=1.44/(R1+2R2)C, 占空比D=( R1+R2 )/( R1+2R2)。 555电路要求R1与R2 均应大于或等于1kΩ ,使R1+R2 应小于或等于3.3MΩ。 三、实验过程与数据分析 1.单稳态触发器逻辑功能的测试。 连接电路如下:

实验三定时器计数器应用实验一

定时器/计数器应用实验一 设计性试验 2012年11月14日星期三第三四节课 一、实验目的 1、掌握定时器/计数器定时功能的使用方法。 2、掌握定时器/计数器的中断、查询使用方法。 3、掌握Proteus软件与Keil软件的使用方法。 4、掌握单片机系统的硬件和软件设计方法。 二、设计要求 1、用Proteus软件画出电路原理图,单片机的定时器/计数器以查询方式工作,在P1.0口线上产生周期为200μS的连续方波,在P 1.0口线上接示波器观察波形。 2、用Proteus软件画出电路原理图,单片机的定时器/计数器以中断方式工作,在P1.1口线上产生周期为240μS的连续方波,在P 1.1口线上接示波器观察波形。 三、电路原理图

四、实验程序流程框图和程序清单及实验结果 /********* 设计要求:(a)单片机的定时器/计数器以查询方式工作, 在P1.0口线上产生周期为200us的连续方波 编写:吕小洋 说明:用定时器1的方式1以查询方式工作 时间:2012年11月10日 ***************/ ORG 0000H 开始 系统初始化

START: LJMP MAIN ORG 0100H MAIN: MOV SP, #2FH CLR EA ;关总中断 CLR ET1 ;禁止定时器1中断 MOV TMOD, #00010000B ;设置定时器1为工作方式1 MOV TH1, #0FFH ;设置计数初值 MOV TL1, #9CH SETB TR1 ;启动定时器 LOOP: JNB TF1, LOOP ;查询计数是否溢出 MOV TH1, #0FFH ;重置计数初值 MOV TL1, #9CH CLR TF1 ;清除计数溢出标志 CPL P1.0 ;输出取反 LJMP LOOP ;重复取反 END

实验08 555定时器及其应用

实验八 555定时器及其应用 一、实验目的 1.熟悉并掌握555时基电路的工作原理; 2.熟悉并掌握555构成的单稳态触发器、多谐振荡器、占空比可调的多谐振荡器三种典型电路结构及工作原理; 3.学会应用555时基集成电路。 二、实验任务(建议学时:4学时) (一)基本实验任务 1. NE555构成的单稳态触发器逻辑功能测试; 2. NE555构成的多谐振荡器及参数测试; 3. NE555构成的占空比可调的多谐振荡器及参数测试; (二)扩展实验任务() 1. 555构成的脉冲宽度调制(PWM —Pulse Width Modulation )器。 2. 利用555时基电路设计一个驱动电路,能够实现对LED 灯的亮度调节。 3. 利用555时基电路设计一个线性斜坡电压(Linear Ramp )发生器。 三、实验原理 1.555定时器又称为时基电路,由于它的内部使用了三个5K 的电阻,故取名555。 NE555引脚功能说明: GND :电源地;TRIG :触发端;OUT :输出端;RESET :清零端,低电平有效; CONT :控制端;THRES :阈值电压输入端;DISCH :放电端;Vcc :电源正极; 5K 5K 5K R S RE S Vcc CONT RESET THRES TRIG GND DISCH OUT 12 6 5 84 3 7 (a )引脚排列 (b )内部框图 图8-1 NE555引脚排列及内部框图

555定时器集成芯片型号很多,例如LM555、NE555、SA555、CB555、ICM7555、LMC555等等,尽管型号繁多,但它们的引脚功能是完全兼容的,在使用中可以彼此替换,大多数双极型芯片最后3位数码都是555,大多数CMOS型芯片最后4位数码都是7555(还有部分定时器芯片的命名采用C555来表示CMOS型555定时器,例如LMC555)。另外,还有双定时器型芯片双极型的556和CMOS型的7556、四定时器NE558。 555的引脚排列和内部框图见图8-1,556的引脚排列见图8-2。 图8-2 NE556双定时器引脚排列 2.双极型与CMOS型555定时器芯片的区别 1)双极型555定时器工作电压范围5~15V,其驱动能力强,最大负载电流达±200mA,其构成的多谐振荡器工作频率较低,极限大约为300kHz(不同厂商生产的555定时器其最高振荡频率不一定相同,具体值需要通过查阅厂商提供的芯片参数手册); 2)CMOS型555定时器工作电压范围3~16V,其驱动能力弱,最大负载电流仅有±4mA,其构成的多谐振荡器工作频率较高,可达500kHz(不同厂商生产的555定时器其最高振荡频率不一定相同,具体值需要通过查阅厂商提供的芯片参数手册); 由于CMOS型的555定时器驱动能力很弱,因此,使用CMOS型的555定时器时,当负载工作电流最大值超过±4mA时,需要在CMOS型555定时器的Out端和负载之间加一级缓冲电路以提高CMOS型555定时器的驱动能力。 注意,这里的负载电流正负表示的含义为:负载电流为正时,表示电流由Out端流出,负载电流为负时,表示电流流入Out端。

电子技术实验报告8—555定时器及其应用

学生实验报告 系别电子信息学院课程名称电子技术实验 班级10通信A班实验名称实验八 555定时器及其应用 姓名葛楚雄实验时间2012年5月30日 学号20指导教师文毅 报告内容 一、实验目的和任务 1.熟悉555型集成时基电路的电路结构、工作原理及其特点。 2.掌握555型集成时基电路的基本应用。 二、实验原理介绍 555集成时基电路称为集成定时器,是一种数字、模拟混合型的中规模集成电路,其应用十分广泛。该电路使用灵活、方便,只需外接少量的阻容元件就可以构成单稳、多谐和施密特触发器,因而广泛用于信号的产生、变换、控制与检测。它的内部电压标准使用了三个5K的电阻,故取名555电路。其电路类型有双极型和CMOS型两大类,两者的工作原理和结构相似。几乎所有的双极型产品型号最后的三位数码都是555或556;所有的CMOS产品型号最后四位数码都是7555或7556,两者的逻辑功能和引脚排列完全相同,易于互换。555和7555是单定时器,556和7556是双定时器。双极型的电压是+5V~+15V,最大负载电流可达200mA,CMOS型的电源电压是+3V~+18V,最大负载电流在4mA以下。 1、555电路的工作原理 555电路的内部电路方框图如图20-1所示。它含有两个电压比较器,一个基本RS触发器,一个放电开关Td,比较器的参考电压由三只5KΩ的电阻器构成分压,它们分别使低电平比较器Vr1反相输入

端和高电平比较器Vr2的同相输入端的参考电平为2/3VCC和1/3VCC。Vr1和Vr2的输出端控制RS触发器状态和放电管开关状态。当输入信号输入并超过2/3VCC时,触发器复位,555的输出端3脚输出低电平,同时放电,开关管导通;当输入信号自2脚输入并低于1/3VCC时,触发器置位,555的3脚输出高电平,同时充电,开关管截止。 R是异步置零端,当其为0时,555输出低电平。平时该端开路或接VCC。Vro是控制电压端(5脚),D 平时输出2/3VCC作为比较器Vr1的参考电平,当5脚外接一个输入电压,即改变了比较器的参考电平,从而实现对输出的另一种控制,在不接外加电压时,通常接一个的电容器到地,起滤波作用,以消除外来的干扰,以确保参考电平的稳定。Td为放电管,当Td导通时,将给接于脚7的电容器提供低阻放电电路。 2、555定时器的典型应用 (1)构成单稳态触发器 上图20-2为由555定时器和外接定时元件R、C构成的单稳态触发器。D为钳位二极管,稳态时555电路输入端处于电源电平,内部放电开关管T导通,输出端Vo输出低电平,当有一个外部负脉冲触发信号加到Vi端。并使2端电位瞬时低于1/3VCC,单稳态电路即开始一个稳态过程,电容C开始充电,Vc按指数规律增长。当Vc充电到2/3VCC时,输出Vo从高电平返回低电平,放电开关管Td重新导通,电容C上的电荷很快经放电开关管放电,暂态结束,恢复稳定,为下个触发脉冲的来到作好准备。波形图见图20-3。

单片机实验-定时器计数器应用实验二

定时器/计数器应用实验二 一、实验目的和要求 1、掌握定时器/计数器计数功能的使用方法。 2、掌握定时器/计数器的中断、查询使用方法。 3、掌握Proteus软件与Keil软件的使用方法。 4、掌握单片机系统的硬件和软件设计方法。 二、实验内容或原理 1、利用单片机的定时器/计数器以查询方式计数外 部连续周期性矩形波并在单片机口线上产生某一 频率的连续周期性矩形波。 2、利用单片机的定时器/计数器以中断方式计数外 部连续周期性矩形波并在单片机口线上产生某一 频率的连续周期性矩形波。 三、设计要求 1、用Proteus软件画出电路原理图,单片机的定时 器/计数器以查询方式工作,设定计数功能,对 外部连续周期性脉冲信号进行计数,每计满100 个脉冲,则取反P1.0口线状态,在P 1.0口线上 接示波器观察波形。 2、用Proteus软件画出电路原理图,单片机的定时 器/计数器以中断方式工作,设定计数功能,对 外部连续周期性脉冲信号进行计数,每计满200 个脉冲,则取反P1.0口线状态,在P 1.0口线上 接示波器观察波形。 四、实验报告要求 1、实验目的和要求。 2、设计要求。 3、电路原理图。 4、实验程序流程框图和程序清单。 5、实验结果(波形图)。 6、实验总结。 7、思考题。 五、思考题 1、利用定时器0,在P1.0口线上产生周期为200微秒的连续 方波,利用定时器1,对P1.0口线上波形进行计数,满 50个,则取反P1.1口线状态,在P 1.1口线上接示波器 观察波形。 原理图:

程序清单: /*功能:用计数器1以工作方式2实现计数(查询方式)每计满100个脉冲,则取反P1.0口线状态*/ ORG 0000H START:MOV TMOD,#60H MOV TH1,#9CH MOV TL1,#9CH MOV IE,#00H SETB TR1 LOOP:JBC TF1,LOOP1 AJMP LOOP LOOP1:CPL P1.0

单片机原理及应用课后习题答案第六章作业(李传锋)

第6章MCS-51的定时器/计数器 1.如果晶振的频率为3MHz,定时器/计数器工作在方式0、1、2下,其最大的定时时间各 为多少? 2.定时器/计数器用作定时器时,其计数脉冲由谁提供?定时时间与哪些因素有关? 3.定时器/计数器作计数器模式使用时,对外界计数频率有何限制? 4.定时器/计数器的工作方式2有什么特点?适用于什么应用场合? 5.一个定时器的定时时间有限,如何实现两个定时器的串行定时,来实现较长时间的定 时? 6.定时器/计数器测量某正单脉冲的宽度,采用何种方式可得到最大量程?若时钟频率为 6MHz,求允许测量的最大脉冲宽度是多少? 7.判断下列说法是否正确? (1)特殊功能寄存器SCON,与定时器/计数器的控制无关。 (2)特殊功能寄存器TCON,与定时器/计数器的控制无关。 (3)特殊功能寄存器IE,与定时器/计数器的控制无关。 (4)特殊功能寄存器TMOD,与定时器/计数器的控制无关。 8.设定1ms的定时,可以在P1.0引脚上产生周期为2ms的方波输出,设晶体振荡器的频率 为6MHz,分别写出在方式0和方式1时,赋给T0的常数。 9.设MCS-51单片机的晶振频率为12MHz,请编程使P1.O端输出频率为20kHz的方波。 10.要求采用定时中断的方式,实现下图所示流水灯的双向循环(D1—D8—D1)流动功能。 其中流水灯的闪烁速率为每秒1次。 11.设单片机的fosc = 12MHz,使P1.O和P1.1分别输出周期为1ms和lOms的方波,请用定时器TO方式2编程实现。

附录2:作业及答案 1.如果晶振的频率为3MHz,定时器/计数器工作在方式0、1、2下,其最大的定时时间各 为多少?(12/3×8192=32.768ms;12/3*65636=262.144ms; 12/3*256=1.024ms) 2.定时器/计数器用作定时器时,其计数脉冲由谁提供?定时时间与哪些因素有关? (定时的计数脉冲来自于单片机内部,即每个机器周期产生一个计数脉冲,也就是每个机器周期计数器加1。定时时间与定时器的工作模式、定时器的初值选择有关。) 3.定时器/计数器作计数器模式使用时,对外界计数频率有何限制? (计数脉冲的频率不能高于振荡脉冲频率的1/24;由于确认1次负跳变要花2个机器周期,即24个振荡周期,因此外部输入的计数脉冲的最高频率为系统振荡器频率的1/24。)4.定时器/计数器的工作方式2有什么特点?适用于什么应用场合? (自动重装的8位计数器,TLx读数溢出时,溢出标志位置1的同时,自动将THx中的常数送到TLx中,使TLx从初值开始计数。多用于串口通信精确定时,产生波特率用) 5.一个定时器的定时时间有限,如何实现两个定时器的串行定时,来实现较长时间的定 时? (1)2个定时/计数器共同处理; (2)1个定时/计数器配合软件计数方式处理。 6.定时器/计数器测量某正单脉冲的宽度,采用何种方式可得到最大量程?若时钟频率为 6MHz,求允许测量的最大脉冲宽度是多少? (采用方式1定时工作方式,最大脉冲宽度为131.072ms) 7.判断下列说法是否正确? (5)特殊功能寄存器SCON,与定时器/计数器的控制无关。(对) (6)特殊功能寄存器TCON,与定时器/计数器的控制无关。(错) (7)特殊功能寄存器IE,与定时器/计数器的控制无关。(错) (8)特殊功能寄存器TMOD,与定时器/计数器的控制无关。(错) 8.设定1ms的定时,可以在P1.0引脚上产生周期为2ms的方波输出,设晶体振荡器的频 率为6MHz,分别写出在方式0和方式1时,赋给T0的常数。 (方式0:13位计数器(最大计数8192),TH0=1EH,TL0=0CH; 方式1为16位计数器(最大计数65536),TH0=0FEH,TL0=0CH) 7192=213-1000=7192=1111000001100 a=213-5000×12/12=3192= 1100 0111 1000B 9.设MCS-51单片机的晶振频率为12MHz,请编程使P1.O端输出频率为20kHz的方波。 解:fosc = 12MHz,所以机器周期为1us。20kHz的方波周期为1/(20×1000)=50us,方波即高电平和低电平和时间相等,所以只需设一个定时器定时25us将P1.O求反一次即可。由于题目没有规定,所以可以用查询方式,也可以用中断方式进行编程实现。 方法一:采用查询方式实现 #include

555集成定时器的应用试验报告

电工电子实验报告 555 集成定时器的应用 一、实验目的 1. 熟悉555 定时器电路的工作原理。 2. 熟悉555 时基电路逻辑功能的测试方法。掌握用555 定时器电路构成单稳态触 发器,多谐振荡器,施密特触发器的方法和原理。 3. 了解定时器555 的实际应用。(做一个闪烁指示灯门铃) 二、实验仪器与器材 1 、数字逻辑实验箱1 台 2 、万用表1 只 3 、双踪示波器1 台 4 、元器件:NE555、放光二极管、电阻、电容、扬声器、导线若干 三、预习要求 1 .对照功能表熟悉555 定时器各管脚及其功能。 2 阅读本实验的实验原理以及教材中有关单稳态触发器、多谐振荡器、施密特振荡器的容。 3 .根据原理图和给出的电路参数,画好单稳态触发器、多谐振荡器、施密特振荡器的电路图,估算实验结果。 4 .了解55 5 定时器的一般应用电路。 四、实验原理 555 定时器是模拟—数字混合式集成电路,利用它可以方便地构成脉冲产生、整形电路和定时、延时电路。具有功能强,使用灵活、方便等优点,在数字设备、工业控制、家用电器、电子玩具等许多领域都得到了广泛的应用。 集成定时器的产品主要有双极型和CMOS 型两类,按集成电路部定时器的个数又可分为单定时器和双定时器;双极型单定时器电路的型号为555 ,双定时器电路的型号为556 ,其电源电压的围为5~18V ;CMOS 单定时器电路的型号为7555 ,双定时器电路的型号为7556 ,其电源电压的围为2~18V 。CMOS 型定时器的最大负载电流要比双极型的小,它们的功能和外引脚排列完全相同。 (一)、555 定时器的电路结构及其功能 图4- 1为555 定时器的部逻辑电路和外引脚图,从结构上看,555 电路由2 个比较器、1 个基本RS 触发器、1 个反相缓冲器、1 个集电极开路的放电晶体管和3 个5k Ω电阻组成分压器组成。

单片机 第六章 习题参考答案

第六章习题参考答案 一、填空题 1、当定时器T0工作在方式3时,要占用定时器T1 的 TR1 和 TF1 两个控制位。 2、在定时器T0工作方式3下,TH0溢出时, TF1 标志将被硬件置1去请求中断。 3、在定时器T0工作方式3下,欲使TH0停止工作,应执行一 条 CLR TR1 的指令。 4、使用定时器/计数器1设置串行通信的波特率时,应把定时器/计数器1设定作方式 2 ,即自动重新加载方式。 5、当计数器产生计数溢出时,把定时器/计数器的TF0(TF1)位置“1”。对计数溢出的处理,在中断方式时,该位作为中断标志位使用;在查询方式时,该位作状态位使用。 6、在定时器工作方式1下,计数器的宽度为16位,如果系统晶振频率为6MHz,则最大定时时间为 131.072ms ,若系统晶振频率为12MHz,则最大定时时间 为 65.536ms 。 7、8051单片机内部设有两个16位定时器/计数器,

即 T0 和 T1 。 8、T0由两个8位特殊功能寄存 器 TH0 和TL0 组成,T1 由 TH1 和 TL1 组成。 9、定时时间与定时器的工作方式、计数初值及振荡周期有关。 10、MCS-51的定时器/计数器作计数器时计数脉冲由外部信号通过引脚 P3.4 和 P3.5 提供。 11、MCS-51的定时器/计数器T0的门控信号GATE设置为1时,只有 INT0 引脚为高电平且由软件使 TR0 置1时,才能启动定时器/计数器T0工作。 12、当T0为方式 3 ,T1为方式 2 的时候,8051单片机的定时器可提供3个8位定时器/ 计数器。 二、选择题 1、在下列寄存器中,与定时/计数控制无关的是( C ) A、 TCON B、 TMOD C、 SCON D、 IE 2、在工作方式0下,计数器是由TH的全部8位和TL的5位组成,因此其计数范围是( A )

实验八_555集成定时器及其应用

实验八555集成定时器及其应用 一、实验目的 1.熟悉555 集成定时器的组成及工作原理。 2.掌握用定时器构成单稳态电路、多谐振荡电路和施密特触发电路。 3.了解555 定时器的应用:构成变音信号发生器。 4.学习用示波器对波形进行定量分析,测量波形的周期、脉宽和幅值等。二、实验原理及参考电路 1.555定时器的工作原理。 555定时器是一种数字与模拟混合型的中规模集成电路,应用广泛。外加电阻、电容等元件可以构成多谐振荡器,单稳电路,施密特触发器等。 555定时器原理图及引线排列如图8.1、图8.2所示。其功能见表8.1。定时器内部由比较器、分压电路、RS触发器及放电三极管等组成。分压电路由三个5 K的电阻构成,分别给A1和A2提供参考电平2/3Vcc和1/3Vcc。A1和A2的输出端控制RS触发器状态和放电管开关状态。当输入信号自6脚输入大于2/3 Vcc时,触发器复位,3脚输出为低电平,放电管T导通;当输入信号自2脚输入并低于1/3Vcc时,触发器置位,3脚输出高电平,放电管截止。4脚是复位端,当4脚接入低电平时,则Vo=0;正常工作时4接为高电平。5脚为控制端,平时输入2/3Vcc作为比较器的参考电平,当5脚外接一个输入电压,即改变了比较器的参考电平,从而实现对输出的另一种控制。如果不在5脚外加电压通常接0.01μF电容到地,起滤波作用,以消除外来的干扰,确保参考电平的稳定。 图8.1 555定时器内部框图图8.2 555定时器引脚排列 表8.1 555定时器的功能表

2.典型应用 (1)构成单稳态触发器 电路如图8.3所示,接通电源→电容C充电(至2/3Vcc)→RS触发器置0→Vo=0,T导通,C放电,此时电路处于稳定状态。当2加入VI<1/3Vcc时,RS 触发器置1,输出Vo=1,使T 截止。电容C开始充电,按指数规律上升,当电容C充电到2/3Vcc时,A1翻转,使输出Vo=0。此时T又重新导通,C很快放电,暂稳态结束,恢复稳态,为下一个触发脉冲的到来作好准备。其中输出Vo 脉冲的持续时间tw=1.1RC,一般取R=1kΩ--10MΩ,C>1000PF,只要满足VI的重复周期大于tp0 ,电路即可工作,实现较精确的定时。 图8.3 单稳态触发器图8.4 多谐振荡器 (2) 多谐振荡器 电路如图8.4所示,电路无稳态,仅存在两个暂稳态,亦不需外加触发信号,即可产生振荡(振荡过程自行分析)。电容C在1/3Vcc--2/3Vcc之间充电和放电,输出信号的振荡参数为: 周期T=0.7 C(R1+2R2) 频率f=1/T=1.44/(R1+2R2)C, 占空比D=( R1+R2 )/( R1+2R2)。

555定时器及其应用实验报告

555定时器及其应用 【实验目的】 (1) 掌握555的工作原理及其性能特点 (2) 掌握555组成的基本电路及应用。 【实验要求】 (1) 用555组成一个时钟脉冲信号发生器,要求输出:标准秒脉冲, 20Hz~20kHz 范围内任意频率可调、占空比可调的脉冲信号。 (2) 设计一个触摸开关,要求每触发一次其输出端维持10秒钟的高 电平。 (3) 用555设计一个分频器,要求输入时钟脉冲的频率为1KHz ,其 输出为100Hz 。 【实验器材】 面包板,555芯片一片,函数发生器,直流稳压电源,万用表,示波器,电阻、电容、导线若干。 【实验原理】 (1) 时钟脉冲产生器 555组成的多谱振器可以用作各种时钟脉冲发生器,如图1所示,通过D1,D2两个二极管将电路的充电支路与放电支路分开,则由RC 电路的充放电时间公式得,充电时间为:110.7t R C = ,放电时间为230.7t R C =,因此输出脉冲的频率为131.43()f R R C =+ ,占空比为

1 11213 t R t t R R =++ 。通过调节R1和R3的阻值便可实现输出不同频率与占空比的脉冲信号。 图 1 时钟脉冲发生器 (2) 触摸开关 555组成的单稳态触发器可以用作触摸开关,电路如图2所示,其中M 为触摸金属片(或导线)。静态时无触发脉冲输入,555的输出为低电平即U O =0,发光二极管不亮,当用手触摸金属片M 时,相当 于2端输入一负脉冲,555的内部比较器A2翻转,使输出变为高电平即U O =1,发光二极管亮,直到电容C 上的电压充电23 C D D U U = 。发 光二极管亮的时间为 1.1tp RC = 。

定时器计数器应用实验一

一、实验目的和要求 1、掌握定时器/计数器计数功能的使用方法。 2、掌握定时器/计数器的中断、查询使用方法。 3、掌握Proteus软件与Keil软件的使用方法。 4、掌握单片机系统的硬件和软件设计方法。 二、设计要求 1、用Proteus软件画出电路原理图,单片机的定时器/计数器以查询方式工作, 设定计数功能,对外部连续周期性脉冲信号进行计数,每计满100 个脉冲, 则取反P1.0口线状态,在P 1.0口线上接示波器观察波形。 2、用Proteus软件画出电路原理图,单片机的定时器/计数器以中断方式工作, 设定计数功能,对外部连续周期性脉冲信号进行计数,每计满200个脉冲, 则取反P1.0口线状态,在P 1.0口线上接示波器观察波形。 三、电路原理图如下所示:

四:实验程序流程框图和程序清单 查询法流程框图: 中断法流程框图: 开始定时器初始化开定时器 清零TF0结束 TF0=0 P1.0取反N 开始堆栈初始化 定时器 中断初始化 开定时器进行中断 P1.1取反结束 程序清单: 查询法汇编: ORG 0000H MAIN: MOV TMOD, #02H MOV TH0, #9CH MOV TL0, #9CH MOV IE, #00H SETB TR0 LOOP: JBC TF0, LOOP1 LJMP LOOP LOOP1: CPL P1.0 LJMP LOOP END

查询法C语言:#include

数字电路基础D集成定时器及应用

7.2集成555定时器及应用 集成555定时器是一种多用途的单片集成电路,它将模拟电路和数字电路兼容在一起,集成在同一硅片上。只要外接几个元件,就可以构成施密特触发器、单稳态触发器、多谐振荡器等数字电路和模拟电路。 集成定时器使用灵活、方便,在脉冲信号的产生、波形的变换、定时、检测、控制、报警,甚至在家用电器等领域中都得到了广泛的应用。 集成定时器的型号很多,但其内部电路结构和外部引线的排列则完全相同。 7.2.1集成555定时器的工作原理 下面以国产CMOS型CC7555定时器为例,进行简要的分析讨论。CMOS型555定时器是在双极型555基础上采用CMOS工艺制作的,为与双极型555相区分,在555前面冠以“7”,即7555。CC7555定时器等效电路图如图7-2-l所示。 1.电路结构 CC7555集成定时器主要由下列三部分组成。 (1)比较器 电路中有两个比较器Cl和C2,两个比较器的结构完全相同,由差动放大器和恒流源电路构成。Uil是比较器Cl的输入端(称为阀值端,图中用TH标注);Ui2是比较器C2的输入端(称为触发端,图中用TH标注)。比较器Cl的反相输入端和C2同相输入端的参考电压U R1和U R2是由电源电压Ucc经3个等值的电阻R分压提供的,在控制电压输入端(图中用CO标注)悬空时, U Rl=2Ucc/3, U R2=Ucc/3如果控制电压输入端(CO)接固定电压,则 U Rl=Uco, U R2=Uco/2 (2)RS触发器

由或非门G2和G4构成的RS触发器,其输出状态取决于比较器Cl和C2输出是高电平还是低电平。 (3)放电开关管和输出驱动电路 放电开关管VT是一个NMOS管,当栅极为高电平时,VT导通,放电端(图中用D标注)的外接电容便放电;当栅极为低电平时,VT截止。 输出端的反相器G2是一个互补形式的输出驱动门,用来增强电路的带负载能力,并起隔离作用。 2.工作原理 CC7555集成定时器的工作过程如下: ①当R端为有效电平时,RS触发器被复位(Q=0),经Gl门反相后,使放电管VT导 通,外接电容放电,电路的输出为低电平。 ②当阀值输入端TH的输入电压U il>U Rl(=2Ucc/3)时,比较器Cl输出为高电平,使 RS触发器的输出Q=0,放电管VT导通,电路的输出(图中用OTT标注)为低电平。 ③当U il<U Rl(=2Ucc/3),而Ui2>U R2(=Ucc/3)时,比较器Cl和C2的输出均为 “0”,使RS触发器的状态保持不变,放电路的输出状态也保持不变。 ④当Ui1<UR1(=2Ucc/3),而Ui2<UR2(=Ucc/3)时,比较器Cl输出为“0”,比较器 C2输出为“l”,使RS触发器的输出Q=1,放电管VT截止,电路输出为高电平。 综合上述分析,归纳出CC7555集成定时器的功能如表7-2-1所示。 7.2.2 集成定时器的应用 1.单稳态触发器 图7-2-2(a)是用 CC7555 构成的单稳态触发器。

数字逻辑论文 集成定时器5G555的功能及其应用

集成定时器5G555的功能及其应用 计科系计本三班 摘要:集成电路由SSI发展到MSI、LSI和VLSI后,单个芯片的功能不断增强。一般的,在SSI中仅仅是基本器件(如逻辑门或触发器)的集成,在MSI中已是逻辑器件的集成,而在LSI和VSLI中则是一个数字子系统或整个数字系统的集成。数字系统中除了组合电路和时序电路外,还有一种信号发生及完成变换的电路。 关键词:模拟电路功能逻辑电路功能中规模集成电路集成定时器 引言:集成定时器555是一种将模拟电路功能与逻辑电路功能巧妙结合在一起的中规模集成电路。该电路功能灵活、使用范围广,在控制,定时、检测、仿声和报警等方面有着广泛应用。 正文: 1、组成:电阻分压器、电压比较器、基本R-S触发器、放电三极管和输出缓冲器。 (一)、电阻分压器:由3个阻值均为5k欧的电阻串联构成分压器,为电压比较器cl 和c2提供参考电压。当外加控制电压Vco时,比较器的参考电压将发生变化,相应电路的阈值、触发电平也将随之改变,并进而影响电路的定时参数。为了防止干扰,当不外加控制电压时,co端一般通过一个小电容(如0.01uF)接地,以旁路高频干扰。(二)、电压比较器:电压比较器c1和c2是两个结构完全相同的理想运算放大器。当v+> v-,输出高电平1信号;当v+< v-,输出低电平0信号。C1的v+接VR1, v-接阈值输入TH,输出R的状态取决于VTH和VR1的比较结果。当VTH < VR1,R为1;当VTH > VR1,R为0。C2的v+接V/TR,v-接参考电压VR2,输出S的状态取决于V/TR 和VR2的比较结果。当V/TR < VR2 ,S为0;当V/TR > VR2 ,S为1。 (三)、基本R-S触发器:与非门G1、G2构成低电平触发基本R-S触发器,触发器输出Q为电路输出OUT的状态。触发器的/Q端控制放电三极管的导通与截止,当外部复位信号/RD为0时,可使输出VO为0,定时器输出直接复位。 (四)、放电三极管:D连接上拉电阻接至电源构成反相器:当Q为0,T导通,D为0;当Q为1,T截止,D为1;

浙大版电工电子学实验报告15集成定时器及其应用

课程名称:电工电子学实验指导老师:实验名称:集成定时器及其应用 一、实验目的 1.了解集成定时器的功能和外引线排列。 2.掌握用集成定时器构成多谐振荡器、单稳态触发器和施密特触发器的方法和原理。 二、主要仪器设备 1.MDZ-2型模拟电子技术实验箱; 2.HY3003D-3型可调式直流稳压稳流电源; 3.XJ4318型双踪示波器; 4.XJ1631数字函数信号发生器; 5.运放、时基电路实验板。 三、实验内容 1.多谐振荡器 图15-2 按图15-2接好实验线路,U CC采用+5V电源,用双踪示波器观察并记录u C、u0的波形。注意两波形的时间对应关系,并测出u0的幅度和t1、t2及周期T。 2.单稳态触发器 图15-4 按图15-4接好实验电路,U CC采用+5V电源,u i信号用幅度为5V的方波信号,适当调节方波频率(月500Hz)(方波可以由函数信号发生器提供,或由电子技术实验箱直接提供),观察并记录u i、u2、u C、u0的 波形,标出u o的幅度和暂稳时间t W。

3.施密特触发器 图15-6 按图15-6接线,输入u s采用正弦波信号(由函数信号发生器提供),U CC采用+5V电源。接通电源、逐步加大u s信号电压,用示波器观察u i波形,直到u i的有效值等于5V左右。观察并记录u s、u i和u0波形。 四、实验总结 1.用方格纸画好各波形图,并注明幅值、周期(脉宽)等有关参数。注意正确反映各波形在时间上的对

2.整理实验数据,将理论估算结果与实验测试数值相比较,并加以分析讨论。

(注:上表中实验2、3的T理论值都为相应输入波形的T) 结果分析: (1).多谐振荡器 在数值方面,据上表可见,该实验中的各物理量的测量值和理论值相差都不大,最大相对偏差为13.8%,可知实验与理论总体上较为接近。根据其相对偏差的特点,可以看出偏差 并没有一致的规律,因此可推断有较多的随机误差存在,除此之外,可能存在的其他误差有: 1.各元件属性并非完全符合实验设计,存在少许差异,属于系统误差; 2.电路导线不能完全 忽略电阻,再加上导线插头可能接触不良而产生的额外电阻,使得实际电路与设计略有不同, 也属于系统误差,但因为接线有很大的随机性,对于不同的接线方法,可能结果会略有不同; 3.测量仪器(万用表、示波器)有一定的误差; 4.存在人为读数误差,比如在读取示波器上的刻 度值时不可能做到非常精确。 在相位方面,从上文波形图可见,u C和u0的相位相关性较好,形状、大小等方面都与理论相符。 总体来说,实验结果还是比较理想的,较好地实现了多谐振荡器的功能。 (2).单稳态触发器 在数值方面,从表中可看出,除u2的U L(最小幅值)与理论值有很大差距外,其余实验数据都与理论较为相符,其中所有周期T的数据都与输入波形一致,这也与理论是一致的。 由此可以看出,实验误差对周期T的影响极小,而其他数据存在的少量偏差原因大致与(1) 相同,这里不再赘述。而对于u2的U L,实验值与理论值相对偏差高达172%,从图中可以 看出,实验值U L是负值,而理论值为正,经分析,可能是由于输入方波存在负值所致(实验 册中采用的方波无负值),但由于情况复杂,无法进一步分析。同时,通过波形图还可以发 现,图形的个别细微处与理论图像不相符,比如u2在方波有负变正的一瞬间幅值突然变大之 后快速将为原值;而u0在方波由正转负时图像上有一突起;除此之外还有u C在u2彻底恢复 高电位时才停止增长,这与理论也是不相符的。由于此电路情况复杂,难以分析,初步猜测 可能是电路内部构造或由方波有负值所造成的,当然也不排除元件损坏与人为错误的可能。 在相位方面,各波形非常一致,各周期T都与输入波形相同,除了上述的u C增长停止位置与理论有出入外,其余图形对于时间轴几乎没有偏差。 总体来说,此实验的各波形形状基本正确,虽然仍存在一些难以找出原因的问题,但最终还是基本实现了单稳态触发器的功能。 (3).施密特触发器 此实验中仅有t W的实验值与理论值有少许偏差,而其余两个周期T都与输入波形相同。 因此在相位和周期上都几乎没有偏差,而对于t W所存在的8.6%的偏差则很有可能是随机误 差,当然也可能存在(1)中所述的其他可能。 比较u s和u i的波形图可以看出,两波形的时间对应关系良好,很符合理论结果;而比较u i和u0则会发现,u0在u i上所对应的位置并不完全与理论的2/3U CC、1/3U CC相符,尤其是 前者。由于相对偏差并不明显,因此可能是由随机误差所致,但也可能是由于集成块内部电 路并不完全符合2/3、1/3的关系,当然也不能排除其他元件偏差的可能性。 五、心得体会 本次实验通过实际操作,使我们了解了集成定时器的功能,以及由其组成的多谐振荡器、单稳态触发器和施密特触发器的应用,使实践和理论较好地联系在了一起。但在实验过程中,也发现了一些与理论有所出入之处,有些问题甚至难以分析原因,而另一些又可能是由各种误差的干扰所致。由于此次实验理论内容较为繁杂,实际操作中的线路也较为复杂,很难做出准确分析,因此在实验中务必仔细检查元件的完好性,才能保证实验结果的准确性。除此之外,通过实验我们再次练习了示波器和信号发生器的使用,使得此方面的技能更为熟练。

定时器工作原理及应用引脚图

555定时器 摘要:555定时器是一种多用途的数字——模拟混合集成电路,利用它能极方便地构成施密特触发器、单稳态触发器和多谐振荡器。由于使用灵活、方便,所以555定时器在波形的产生与交换、测量与控制、家用电器、电子玩具等许多领域中都得到了广泛应用。本文主要介绍了555定时器的工作原理及其在单稳态触发器、多谐振荡器方面的应用。 关键词:数字——模拟混合集成电路;施密特触发器;波形的产生与交换 555芯片引脚图及引脚描述 555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。 1脚为地。2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。 当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平; 2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。 4脚是复位端,当4脚电位小于0.4V时,不管2、6脚状态如何,输出端3脚都输出低电平。 5脚是控制端。 7脚称放电端,与3脚输出同步,输出电平一致,但7脚并不输出电流,所以3脚称为实高(或低)、7脚称为虚高。