小信号分析法重点笔记

开关电源的反馈环路设计是开关电源设计的一个非常重要的部分,它关系到一个电源性能的好坏。要设计一个好的环路,必须要知道主回路的数学模型,然后根据主回路的数学模型,设计反馈补偿环路。开关电源是一个非线性系统,但可以对其静态工作点附近进行局部线性化,这种方法称为小信号分析法。

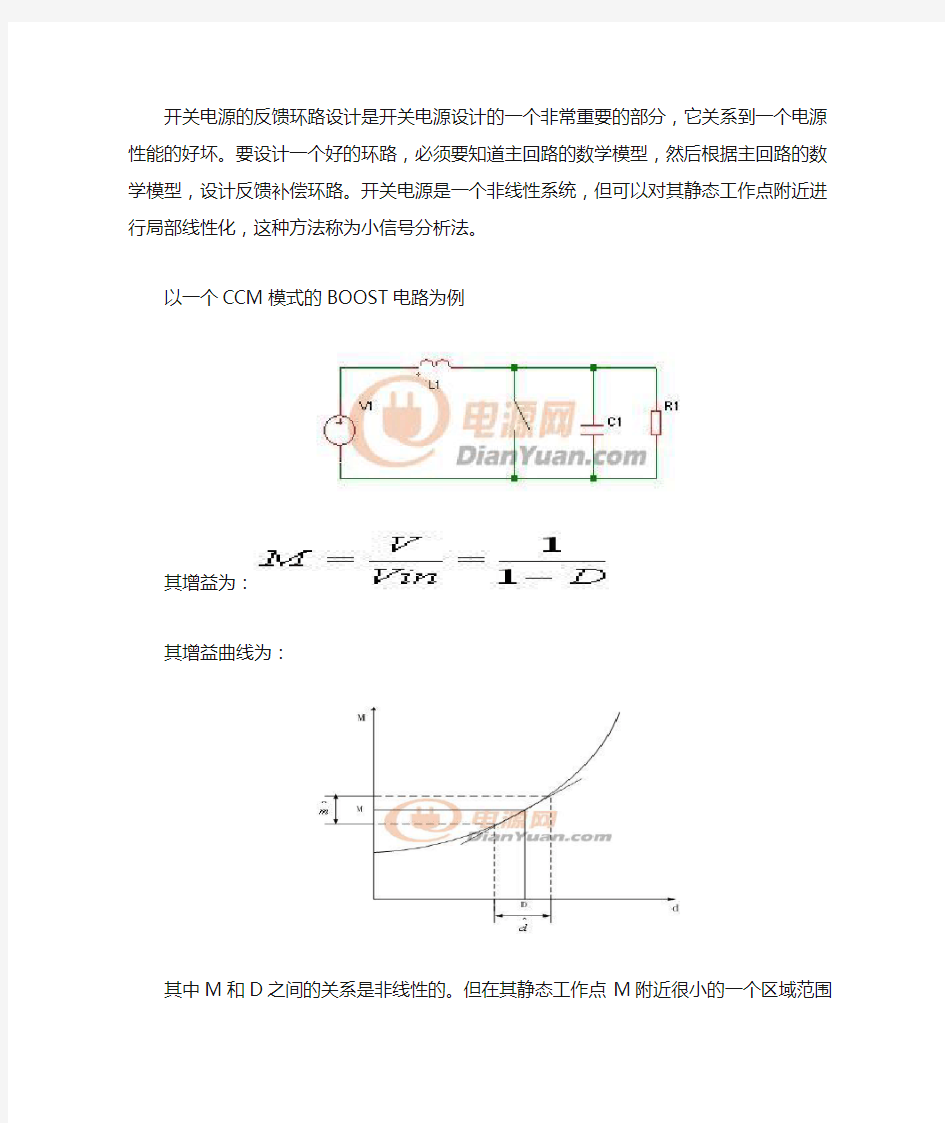

以一个CCM模式的BOOST电路为例

其增益为:

其增益曲线为:

其中M和D之间的关系是非线性的。但在其静态工作点M附近很小的一个

区域范围内,占空比的很小的扰动和增益变化量之间的关系是线性的。因此在这个很小的区域范围内,我们可以用线性分析的方法来对系统进行分析。这就是小信号分析的基本思路。

因此要对一个电源进行小信号建模,其步骤也很简单,第一步就是求出其静态工作点,第二步就是叠加扰动,第三步就是分离扰动,进行线性化,第四步就是拉氏变换,得到其频域特性方程,也就是我们说的传递函数。

要对一个变换器进行小信号建模,必须满足三个条件,首先要保证得到的工作点是“静”态的。因此有两个假设条件:

1,一个开关周期内,不含有低频扰动。因此叠加的交流扰动小信号的频率应该

远远小于开关频率。这个假设称为低频假设

2,电路中的状态变量不含有高频开关纹波分量。也就是系统的转折频率要远远小于开关频率。这个假设称为小纹波假设。

其次为了保证这个扰动是在静态工作点附近,因此有第三个假设条件:3,交流小信号的幅值必须远远小于直流分量的幅值。这个称为小信号假设。

对于PWM模式下的开关电源,通常都能满足以上三个假设条件,因此可以使用小信号分析法进行建模。

对于谐振变换器来说,由于谐振变换器含有一个谐振槽路。在一个开关时区或多个开关时区内,谐振槽路中各电量为正弦量,或者其有效成分是正弦量。正弦量的幅值是在大范围变化的,因此在研究PWM型变换器所使用的“小纹波假设”在谐振槽路的小信号建模中不再适用。

对于谐振变换器,通常采用数据采样法或者扩展描述函数法进行建模。

以一个CCM模式下的BUCK电路为例,应用上面的四个步骤,来建立一个小信号模型。对于一个BUCK电路

当开关管开通时,也就是在(0-DTs)区间。其状态方程为

当开关管S断开时,二极管D导通,忽略二极管D的压降,可得到等效电路

其状态方程为:

将状态变量在一个开关周期内求平均,

简化后得到:

这便是一个开关周期内的状态方程,基于上面的低频和小纹波假设,变换器在一个开关周期内是稳定的,因此这也是其静态工作点的方程。

对上面的稳态方程叠加扰动,可以得到以下方程:

进行分解后为:

将稳态方程代入分解后的扰动方程,便可将扰动方程进行分离:

基于上面的第三个假设,即小信号假设,因此可以忽略掉 ,因此可以得到CCM模式下BUCK的小信号方程:

对于一个开关电源,我们的控制目标是输出电压,控制变量是占空比D。因此,我们可以忽略掉输入电压扰动,得到占空比扰动所对应的输出电压的扰动方程。

对上面的方程进行拉氏变换,得到其频域方程:

将两个方程进行整合,可以得到占空比的扰动与输出电压扰动之间的关系:

化简后就可以得到:

从上面的方程已经很清晰的看到输出电压扰动与占空比扰动之间的关系,将其移项便可以得到CCM BUCK的传递函数:

小信号分析法

主要是状态空间平均法,由美国加里福尼亚理工学院的R.D.Middlebrook于1976年提出,可以说这是电力电子学领域建模分析的第一个真正意义的重大突破。后来出现的如电流注入等效电路法、等效受控源法(该法由我国学者张兴柱于1986年提出)、三端开关器件法等,这些均属于电路平均法的范畴。平均法的缺点是明显的,对信号进行了平均处理而不能有效地进行纹波分析;不能准确地进行稳定性分析;对谐振类变换器可能不大适合;关键的一点是,平均法所得出的模型与开关频率无关,且适用开关电源条件是电路中的电感电容等产生的自然

频率必须要远低于开关频率,准确性才会较高。

大信号分析法

有解析法、相平面法、大信号等效电路模型法、开关信号流法、n次谐波三端口模型法、KBM法及通用平均法。还有一个是我国华南理工大学教授丘水生先生于1994年提出的等效小参量信号分析法,不仅适用于PWM变换器也适用于谐振类变换器,并且能够进行输出的纹波分析。

建模的目的是为了仿真,继而进行稳定性分析。1978年,R.Keller首次运用R.D.Middlebrook的状态空间平均理论进行开关电源的SPICE仿真。近30年来,在开关电源的平均SPICE模型的建模方面,许多学者都建立了开关电源各种各样的模型理论,从而形成了各种SPICE模型。这些模型各有所长,比较有代表性的有:Dr.SamBenYaakov的开关电感模型;Dr.RayRidley的模型;基于Dr.VatcheV orperian的Orcad9.1的开关电源平均Pspice模型;基于Steven Sandler 的ICAP4的开关电源平均Isspice模型;基于Dr. VincentG.Bello的Cadence的开关电源平均模型等等。在使用这些模型的基础上,结合变换器的主要参数进行宏模型的构建,并利用所建模型构成的DC-DC变换器在专业的开关电源仿真软件(如Matlab、Pspice等)平台上进行直流分析、小信号分析以及闭环大信号瞬态分析。

设计一个具有良好动态和静态性能的开关电源时,控制环路的设计是很重要的一个部分。而环路的设计与主电路的拓扑和参数有极大关系。为了进行稳定性分析,有必要建立开关电源完整的小信号数学模型。在频域模型下,波特图提供了一种简单方便的工程分析方法,可用来进行环路增益的计算和稳定性分析。由于开关电源本质上是一个非线性的控制对象,因此,用解析的办法建模只能近似建立其在稳态时的小信号扰动模型,而用该模型来解释大范围的扰动(例如启动过程和负载剧烈变化过程)并不完全准确。好在开关电源一般工作在稳态,实践表明,依据小信号扰动模型设计出的控制电路,配合软启动电路、限流电路、钳位电路和其他辅助部分后,完全能使开关电源的性能满足要求。开关电源一般采用Buck电路,工作在定频PWM控制方式。

Buck电路电感电流连续时的小信号模型

图1为典型的Buck电路,为了简化分析,假定功率开关管S和D1为理想开关,滤波电感L为理想电感(电阻为0),电路工作在连续电流模式(CCM)下。Re为滤波电容C的等效串联电阻,Ro为负载电阻。各状态变量的正方向定义如图1中所示。S导通时,对电感列状态方程有L(dil/dt)=Uin-Uo (1)S断开,D1续流导通时,状态方程变为L(dil/dt)=-Uo (2)

占空比为D时,一个开关周期过程中,式(1)及式(2)分别持续了DTs和(1-D)Ts的时间(Ts为开关周期),因此,一个周期内电感的平均状态方程为L(dil/dt)=D(Uin-Uo)+(1-D)(-Uo)=DUin-Uo (3)稳态时DUin=0,则DUin=Uo。这说明稳态时输出电压是一个常数,其大小与占空比D和输入电压Uin成正比。由于电路各状态变量总是围绕稳态值波动,因此,由式(3)得L[d(il+il')/dt]=(D+d)(Uin+Uin')-(Uo+Uo') (4)

式(4)由式(3)的稳态值加小信号波动值形成。上标为波浪符的量为波动量,d为D的波动量。式(4)减式(3)并略去了两个波动量的乘积项得L(dil'/dt)=DUin'+dUin-Uo' (5)由图1,又有iL=C(duc/dt)+Uo/R0 (6)Uo=Uc+ReC(duc/dt) (7)式(6)及式(7)不论电路工作在哪种状态均成立。由式(6)及式(7)可得iL+ReC(dil/dt)=1/Ro(Uo+CRo(duo/dt)) (8)式(8)的推导中假设Re< 式(9)减式(8)得iL+ReC(dil/dt)=1/Ro(Uo+CRo(dUo/dt)) (10) 将式(10)进行拉氏变换得iL(s)=(Uo(s)/Ro)·[(1+sCRo)/(1+sCRe)] (11) 一般认为在开关频率的频带范围内输入电压是恒定的,即可假设=0并将其代入式(5),将式(5)进行拉氏变换得sLiL'(s)=d(s)Uin-Uo'(s) (12)由式(11),式(12)得Uo'(s)/d(s)=Uin[(1+sCRe)/(s2LC+s(ReC+L/Ro)+1] (13)iL'(s)/d(s)=[(1+sCRo)/s2LC+s(ReC+L/Ro)+1]·Uin/Ro (14)式(13),式(14)便Buck电路在电感电流连续时的控制-输出小信号传递函数。 2 电压模式控制(VMC) 电压模式控制方法仅采用单电压环进行校正,比较简单,容易实现,可以满足大多数情况下的性能要求,如图2所示。图2中,当电压误差放大器(E/A)增益较低、带宽很窄时,Vc波形近似直流电平,并有 D=Vc/Vs (15)d=Vc'/Vs (16) 式(16)为式(15)的小信号波动方程。整个电路的环路结构如图3所示。图3没有考虑输入电压的变化,即假设Uin=0。图3中,(一般为0)及分别为电压给定与电压输出的小信号波动;KFB=UREF/Uo,为反馈系数;误差e为输出采样值偏离稳态点的波动值,经电压误差放大器KEA放大后,得;KMOD为脉冲宽度调制器增益,KMOD=d/=1/Vs;KPWR为主电路增益,KPWR=/d=Uin;KLC为输出滤波器传递函数,KLC=(1+sCRe)/[S2LC+s(ReC+L/Ro)+1]。 在已知环路其他部分的传递函数表达式后,即可设计电压误差放大器了。由于KLC提供了一个零点和两个谐振极点,因此,一般将E/A设计成PI调节器即可,KEA=KP(1+ωz/s)。其中ωz用于消除稳态误差,一般取为KLC零极点的 1/10以下;KP用于使剪切频率处的开环增益以-20dB/十倍频穿越0dB线,相角裕量略小于90°。 VMC方法有以下缺点: 1)没有可预测输入电压影响的电压前馈机制,对瞬变的输入电压响应较慢,需要很高的环路增益; 2)对由L和C产生的二阶极点(产生180°的相移)没有构成补偿,动态响应较慢。 平均电流模式控制含有电压外环和电流内环两个环路,如图4所示。电压环提供电感电流的给定,电流环采用误差放大器对送入的电感电流给定(Vcv)和反馈信号(iLRs)之差进行比较、放大,得到的误差放大器输出Vc再和三角波Vs进行比较,最后即得控制占空比的开关信号。图4中Rs为采样电阻。对于一个设计良好的电流误差放大器,Vc不会是一个直流量,当开关导通时,电感电流上升,会导致Vc下降;开关关断,电感电流下降时,会导致Vc上升。电流环的设计原则是,不能使Vc上升斜率超过三角波的上升斜率,两者斜率相等时就是最优。原因是:如果Vc上升斜率超过三角波的上升斜率,会导致Vc峰值超过Vs的峰值,在下个周波时Vc和Vs就可能不会相交,造成次谐波振荡。 采用斜坡匹配的方法进行最优设计后,PWM控制器的增益会随占空比D的变化而变,如图5所示。当D很大时,较小的Vc会引起D较大的改变,而D 较小时,即使Vc变化很大,D的改变也不大,即增益下降。所以d=DV'/Vs (17)不妨设电压环带宽远低于电流环,则在分析电流环时Vcv为常数。当Vc的上升斜率等于三角波斜率时,在开关频率fs处,电流误差放大器的增益GCA为GCA[d(iLRs)/dt]=GCA(Vo/L)Rs=Vsfs (18) GCA=Vc'/(iL'Rs)=VsfsL/(UoRs) (19) 高频下,将式(14)分子中的“1”和分母中的低阶项忽略,并化简,得 iL'(s)=[d(s)Uin]/sL (20)由式(17)及式(20)有 (iL'Rs)/Vc'=[Rsd(s)Uin/(sL)]/[d(s)Vs/D]=(RsUinD)/(sLVs) (21) 将式(19)与式(21)相乘,得整个电流环的开环传递函数为 (RsUinD/sLVs)·(VsfsL)/(UoRs)=fs/s (22) 将s=2πfc代入上式,并令上式等于1时,可得环路的剪切频率fc=fs/(2π)。因此,可将电流环等效为延时时间常数为一个开关周期的纯惯性环节,如图6 所示。显然,当电流误差放大器的增益GCA小于最优值时,电流响应的延时将会更长。 GCA中一般要在fs处或更高频处形成一个高频极点,以使fs以后的电流环开环增益以-40dB/dec的斜率下降,这样虽然使相角裕量稍变小,但可以消除电流反馈波形上的高频毛刺的影响,提高电流环的抗干扰能力。低频下一般要加一个零点,使电流环开环增益变大,减小稳态误差。 整个环路的结构如图7所示。其中KEA,KFB定义如前。可见相对VMC 而言(参见图3),平均CMC消除了原来由滤波电感引起的极点(新增极点fs 很大,对电压环影响很小),将环路校正成了一阶系统,电压环增益可以保持恒定,不随输入电压Vin而变,外环设计变得更加容易。 平均CMC由于要采样滤波电感的电流,有时显得不太方便,因此,实践中经常采用一种变通的电流模式控制方法,即峰值CMC,如图8所示。电压外环输出控制量(Vc)和由电感电流上升沿形成的斜坡波形(Vs)通过电压比较器进行比较后,直接得到开关管的关断信号(开通信号由时钟自动给出),因此,电压环的输出控制量是电感电流的峰值给定量,由电感电流峰值控制占空比。 峰值CMC控制的是电感电流的峰值,而不是电感电流(经滤波后即负载电流),而峰值电流和平均电流之间存在误差,因此,峰值CMC性能不如平均CMC。一般满载时电感电流在导通期间的电流增量设计为额定电流的10%左右,因此,最好情况下峰值电感电流和平均值之间的误差也有5%,负载越轻误差越大,特别是进入不连续电流(DCM)工作区后误差将超过100%,系统有时可能会出现振荡现象。在剪切频率fc以下,由图6可知平均CMC的电流环开环增益可升到很高(可以>1000),电流可完全得到控制,但峰值CMC的电流环开环增益只能保持在10以内不变(峰值电流和平均值之间的误差引起),因此,峰值CMC更适用于满载场合。 峰值CMC的缺点还包括对噪音敏感,需要进行斜坡补偿解决次谐波振荡等问题。但由于峰值CMC存在逐周波限流等特有的优点,且容易通过脉冲电流互感器等简单办法复现电感电流峰值,因此,它在Buck电路中仍然得到了广泛应用。 转折频率是零点或者极点,有许多个的。系统总增益=LC滤波增益+补偿器增益+采样电路增益。穿越频率是系统总增益=0dB时的频率,是唯一的,一般是开关频率的1/4-1/5. 计算机辅助设计技术的迅速发展和高性能计算机的普及使得开关电源的直接数字仿真 方法得到长足的进步,从采用改进的节点分析法的时域电路仿真发展到采用状态变量方法的分段线性仿真,为了加快模拟速度和提高系统精确性,又出现了分级仿真方法。 数字仿真法是指采用各种各样的算法对开关变换器进行数值计算,从而得到其某些特性数值解的方法。数字仿真法可以对电路进行全面分析,在分析设计和调试中起着重要的作用,但所得结果的物理概念不明确。 数字仿真法又可分为直接数字仿真法和间接数字仿真法,直接数字仿真法是指直接利用现有的通用电路分析软件(如PSPICE等)对开关变换器进行数值计算而得到其解的方法,采用这种方法不必重新建立电路模型,只需对局部电路建立仿真模型或等效子电路即可,其不足之处在于计算速度较慢。直接数字仿真法根据所采用的电路分析软件又可以分为时域电路仿真、分段线性仿真以及分级仿真方法,时域电路仿真主要建立大信号功率半导体的精确模型,分段线性仿真则与之相反,主要用理想开关和线性算法来加速仿真速度,分级仿真方法结合不同工具(如PSPICE和SIMPLIS)及不同技术(如大信号模型和平均模型)来分析不同级的电路。间接数字仿真法是指在数值计算前,需要对开关变换器建立一个专用的适用于数值解的仿真模型如离散模型等,然后采用适当的数值算法求解,其优点是计算速度较快。 解析建模法是指用解析表达式来描述开关变换器特性的建模方法。用解析建模法所得结果的优点是直观明了,物理概念清楚,可以利用线性电路和古典控制理论对开关变换器进行稳态和小信号分析,对设计有一定的指导意义,但其精度较差。解析建模法的主要成果有小信号分析法(代表是状态空间平均法)、Laplace变换法等。 小信号分析主要以状态空间平均法来建立变换器的某一个工作点附近的近似小信号线性模型,该工作点由变换器参数、输入电压和负载决定。 Laplace变换法首先写出网络的频域方程式,得出所求电压或电流的频域表达 式,再将其进行Laplace反变换,从而得出网络解的时域表达式。 直接数字仿真法是指直接利用现有的通用电路分析软件(如PSPICE等)对开关变换器进行数值计算而得到其解的方法,采用这种方法不必重新建立电路模型,只需对局部电路建立仿真模型或等效子电路即可,其不足之处在于计算速度较慢。直接数字仿真法根据所采用的电路分析软件又可以分为时域电路仿真、分段线性仿真以及分级仿真方法,时域电路仿真主要建立大信号功率半导体的精确模型,分段线性仿真则与之相反,主要用理想开关和线性算法来加速仿真速度,分级仿真方法结合不同工具(如PSPICE和SIMPLIS)及不同技术(如大信号模型和平均模型)来分析不同级的电路。间烤数字仿真法是指在数值计算前,需要对开关变换器建立一个专用的适用于数值解的仿真模型如离散模型等,然后采用适当的数值算法求解,其优点是计算速度较快。 小信号分析 为了把握开关变换器的可靠性、稳定性及其动态性能,开关变换器的动态分析是十分重要的。早在20世纪70年代,人们就开始了开关变换器小信号频域模型的研究。小信号分析是要建立某一个工作点附近的近似小信号线性模型,该工作点由变换器参数、输入电压和负载决定。这样,就可以采用线性系统分析方法对开关变换器的调节控制回路进行设计。但是当输入电压或者负载发生变化时,由于工作点将发生变化,这时候分析方法将受到限制。当变换器的自然频率远小于开关频率的一半时,该方法带来的误差是可以接受的。 开关电源的小信号分析是分析电源变换器动态性能的有力工具,也是系统动态设计的依据。其显著优点在于物理概念清楚,可用伯德(Bode)图设计校正环节,因此该方法在电源的分析、仿真与设计中得到普遍重视。 小信号分析主要以状态空间平均法来建立变换器小信号线性模型。状态空间平均法(State-Space Averaging Method)是一种解析分析方法,它是1976年由R.D.Middiebrook提出的一种基于状态平均概念的分析方法,后又经过许多研究者的完善和发展有了不同的形式,它对变换器的分析和设计有很大影响。状态空间平均法是以某种意义的一周期平均值为求解量的连续的状态方程近似代替在一周期中不同时间段成立的分段状态方程"该方法的本质是时间平均。 DDR的基础知识 1.电源 DDR的电源可以分为三类: 主电源VDD和VDDQ, 主电源的要求是VDDQ=VDD,VDDQ是给IO buffer供电的电源,VDD是给但是一般的使用中都是把VDDQ和VDD合成一个电源使用。有的芯片还有VDDL,是给DLL供电的,也和VDD使用同一电源即可。 电源设计时,需要考虑电压,电流是否满足要求,电源的上电顺序和电源的上电时间,单调性等。 电源电压的要求一般在±5%以内。 电流需要根据使用的不同芯片,及芯片个数等进行计算。由于DDR的电流一般都比较大,所以PCB设计时,如果有一个完整的电源平面铺到管脚上,是最理想的状态,并且在电源入口加大电容储能,每个管脚上加一个100nF~10nF的小电容滤波。 参考电源Vref, 参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。由于Vref一般电流较小,在几个mA~几十mA的数量级,所以用电阻分压的方式,即节约成本,又能在布局上比较灵活,放置的离Vref管脚比较近,紧密的跟随VDDQ电压,所以建议使用此种方式。需要注意分压用的电阻在100~10K均可,需要使用1%精度的电阻。 Vref参考电压的每个管脚上需要加10nF的点容滤波,并且每个分压电阻上也并联一个电容较好。 用于匹配的电压VTT(TrackingTermination Voltage) VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。DDR的设计中,根据拓扑结构的不同,有的设计使用不到VTT,如控制器带的DDR器件比较少的情况下。如果使用VTT,则VTT的电流要求是比较大的,所以需要走线使用铜皮铺过去。并且VTT要求电源即可以吸电流,又可以灌电流才可以。一般情况下可以使用专门为DDR设计的产生VTT的电源芯片来满足要求。 而且,每个拉到VTT的电阻旁一般放一个10Nf~100nF的电容,整个VTT电路上需要有uF级大电容进行储能。 一般情况下,DDR的数据线都是一驱一的拓扑结构,且DDR2和DDR3内部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到较好的信号质量。而地址和控制信号线如果是多负载的情况下,会有一驱多,并且内部没有ODT,其拓扑结构为走T点的结构,所以常常需要使用VTT进行信号质量的匹配控制。 2. 时钟 DDR的时钟为差分走线,一般使用终端并联100欧姆的匹配方式,差分走线差分对控制阻抗为100ohm,单端线50ohm。需要注意的是,差分线也可以使用串联匹配,使用串联匹配的好处是可以控制差分信号的上升沿缓度,对EMI可能会有一定的作用。 3. 数据和DQS DQS信号相当于数据信号的参考时钟,它在走线时需要保持和CLK信号保持等长。DQS在DDR2以下为单端信号,DDR2可作为差分信号,也可做单端,做单端时需要将DQS-接地,而DDR3为差分信号,需要走线100ohm差分线。由于内部有ODT,所以DQS不需要终端并联100ohm电阻。每8bit数据信号对应一组DQS信号。 DQS信号在走线时需要与同组的DQS信号保持等长,控制单端50ohm的阻抗。在写数据时,DQ和DQS的中间对齐,在读数据时,DQ和DQS的边沿对齐。DQ信号多为一驱一,并且DDR2和DDR3有内部的ODT匹配,所以一般在进行串联匹配就可以了。 于博士信号完整性分析入门 于争博士 https://www.360docs.net/doc/c76303958.html, 整理:runnphoenix 什么是信号完整性? 如果你发现,以前低速时代积累的设计经验现在似乎都不灵了,同样的设计,以前没问题,可是现在却无法工作,那么恭喜你,你碰到了硬件设计中最核心的问题:信号完整性。早一天遇到,对你来说是好事。 在过去的低速时代,电平跳变时信号上升时间较长,通常几个ns。器件间的互连线不至于影响电路的功能,没必要关心信号完整性问题。但在今天的高速时代,随着IC输出开关速度的提高,很多都在皮秒级,不管信号周期如何,几乎所有设计都遇到了信号完整性问题。另外,对低功耗追求使得内核电压越来越低,1.2v内核电压已经很常见了。因此系统能容忍的噪声余量越来越小,这也使得信号完整性问题更加突出。 广义上讲,信号完整性是指在电路设计中互连线引起的所有问题,它主要研究互连线的电气特性参数与数字信号的电压电流波形相互作用后,如何影响到产品性能的问题。主要表现在对时序的影响、信号振铃、信号反射、近端串扰、远端串扰、开关噪声、非单调性、地弹、电源反弹、衰减、容性负载、电磁辐射、电磁干扰等。 信号完整性问题的根源在于信号上升时间的减小。即使布线拓扑结构没有变化,如果采用了信号上升时间很小的IC芯片,现有设计也将处于临界状态或者停止工作。 下面谈谈几种常见的信号完整性问题。 反射: 图1显示了信号反射引起的波形畸变。看起来就像振铃,拿出你制作的电路板,测一测各种信号,比如时钟输出或是高速数据线输出,看看是不是存在这种波形。如果有,那么你该对信号完整性问题有个感性的认识了,对,这就是一种信号完整性问题。 很多硬件工程师都会在时钟输出信号上串接一个小电阻,至于为什么,他们中很多人都说不清楚,他们会说,很多成熟设计上都有,照着做的。或许你知道,可是确实很多人说不清这个小小电阻的作用,包括很多有了三四年经验的硬件工程师,很惊讶么?可这确实是事实,我碰到过很多。其实这个小电阻的作用就是为了解决信号反射问题。而且随着电阻的加大,振铃会消失,但你会发现信号上升沿不再那么陡峭了。这个解决方法叫阻抗匹配,奥,对了,一定要注意阻抗匹配,阻抗在信号完整性问题中占据着极其重要的 Knowledge 问题 谁在DSP的汇编语言中加入了NOP指令? NOP指令加入的条件是什么? About DSP 1.DSP是实时数字信号处理的核心和标志。 2.DSP分为专用和通用两种类型。专用DSP一般采用定点数据结构(一般不支持小数), 数据结构简单,处理速度快;通用DSP灵活性好,但是处理速度有所降低。 3.DSP采用取指、译码、执行三个阶段的流水线(Pipeline)技术,缩短了执行时间,提高了 运行速率。DSP具有8个Functional unit,如果并行处理的话,以600MHz的时钟计算,如果执行的指令是single cycle指令,则可以4800MIPS(指令每秒)。 4.DSP的8个functional Unit,具有独特的功能,对滤波、矩阵运算、FFT(傅里叶变换) 具有 哈弗结构 把指令空间与数据空间隔离的存储方式。 这样实现是为了实现指令的连续读取,而实现pipeline流水线结构。 传统哈弗结构:两个独立的存储空间,还使用独立总线。让取指与执行存储独立,加快执行速度。 改进型哈弗结构:指令与数据的存储空间还是独立的。但是使用公共的总线(地址总线与数据总线)。这样实现的原因是因为出现了CACHE,数据的存储动作大部分被内部的CACHE 总线承接了,所以总线冲突的情况会大大减少。同时让总线的结构与控制变得简单,CACHE 存储的速度也明显快于外设存储器。 冯诺依曼结构:是指令空间与数据空间共享的存放方式。它不能实现pipeline的执行过程。 Pipeline(流水线)技术 是把指令的取指-译码和指令的执行独立开来的技术。虽然每条指令的过程还是要经过取指-译码-执行三个阶段最少3个CPU Cycle。但是多个指令同时并行先后进行,保证总体的指 信号完整性分析基础系列之一 ——关于眼图测量(上) 汪进进美国力科公司深圳代表处 内容提要:本文将从作者习惯的无厘头漫话风格起篇,从四个方面介绍了眼图测量的相关知识:一、串行数据的背景知识; 二、眼图的基本概念; 三、眼图测量方法; 四、力科示波器在眼图测量方面的特点和优势。全分为上、下两篇。上篇包括一、二部分。下篇包括三、四部分。 您知道吗?眼图的历史可以追溯到大约47年前。在力科于2002年发明基 于连续比特位的方法来测量眼图之前,1962年-2002的40年间,眼图的测量是基 于采样示波器的传统方法。 您相信吗?在长期的培训和技术支持工作中,我们发现很少有工程师能完整地准确地理解眼图的测量原理。很多工程师们往往满足于各种标准权威机构提供的测量向导,Step by Step,满足于用“万能”的Sigtest软件测量出来的眼图给出的Pass or Fail结论。这种对于Sigtest的迷恋甚至使有些工程师忘记了眼图是 可以作为一项重要的调试工具的。 在我2004年来力科面试前,我也从来没有听说过眼图。那天面试时,老板反复强调力科在眼图测量方面的优势,但我不知所云。之后我Google“眼图”, 看到网络上有限的几篇文章,但仍不知所云。刚刚我再次Google“眼图”,仍然 没有找到哪怕一篇文章讲透了眼图测量。 网络上搜到的关于眼图的文字,出现频率最多的如下,表达得似乎非常地专业,但却在拒绝我们的阅读兴趣。 “在实际数字互连系统中,完全消除码间串扰是十分困难的,而码间串扰 对误码率的影响目前尚无法找到数学上便于处理的统计规律,还不能进行准确计算。为了衡量基带传输系统的性能优劣,在实验室中,通常用示波器观察接收信号波形的方法来分析码间串扰和噪声对系统性能的影响,这就是眼图分析法。 如果将输入波形输入示波器的Y轴,并且当示波器的水平扫描周期和码元 定时同步时,适当调整相位,使波形的中心对准取样时刻,在示波器上显示的图形很象人的眼睛,因此被称为眼图(Eye Map)。 二进制信号传输时的眼图只有一只“眼睛”,当传输三元码时,会显示两 只“眼睛”。眼图是由各段码元波形叠加而成的,眼图中央的垂直线表示最佳抽样时刻,位于两峰值中间的水平线是判决门限电平。 在无码间串扰和噪声的理想情况下,波形无失真,每个码元将重叠在一起,最终在示波器上看到的是迹线又细又清晰的“眼睛”,“眼”开启得最大。当有码 数字信号处理报告 数学与信息科学学院 信息与计算科学 学号:41312261 姓名:高萌瑶 数字信号处理 信号处理的问题在各个领域都非常普遍,信号的表现形式也多种多样。若将信号看作自变量时间影响的因变量,则也可细分为如下几种:信号的自变量和函数值均取连续值,称之为模拟信号或时域离散信号;若自变量取离散值,而函数值取连续值,则称此信号为时域离散信号;若自变量和函数值均取离散值,则称为数字信号。 1.模拟信号数字处理方法 在现实生活中及工程技术领域中涉及的信号一般都是模拟信号,即在时域与频域均连续的信号。对模拟信号的处理是通过一些模拟器件,如:晶体管、电阻、电容等,完成对信号的处理。模拟信号处理时改变参数时不具备一些灵活性,而且在计算精度方面也不能得到较高的精度,故处理模拟信号时我们更倾向于将其经过采样和量化编码形成数字信号,再采用数字信号处理技术进行处理。最后,如果需要,则可以将数字信号再转换为模拟信号,进行恢复。 图1 模拟信号数字处理框图 1.1采样间隔与采样信号表示 对模拟信号进行采样可以看作一个模拟信号通过一个电子开关S 。假设电子开关每隔周期T 合上一次,每次合上的时间为T τ<<,在电子开关输出端得到其 采样信号^()a x t 。该电子开关的作用等效成一宽度为τ,周期为T 的矩形脉冲串()P t τ相乘的结果。 如果电子开关合上的时间0τ→,则形成理想采样,此时上面的脉冲串变成单位冲激串,用()P t δ表示。()P t δ中每个单位冲激处在采样点上,强度为1。理想采样则是()a x t 与()P t δ相乘的结果。 用公式表示为: ^()() ()()()()()n a a a n P t t nT x t x t P t x t t nT δδδδ∞=-∞∞ =-∞= -=?=-∑∑ 其中上式中()t δ是单位冲激信号,在上式中只有当t nT =时,才可能有非零值,因此将采样信号表示为下式: ^ ()()()a a n x t x nT t nT δ∞ =-∞=-∑ 1.2采样速率与模拟信号最高频率的关系 为了使采样信号不失真的恢复原模拟信号,需寻找速率s f 与模拟信号最高频率c f 之间的关系。在傅里叶变换中,两个信号在时域相乘的傅里叶变换等于两个信号分别的傅里叶变换的卷积,因此: ()FT[(t)] ()FT[(t)]()FT[P (t)]a a a a X j x X j x P j δδ∧∧ Ω=Ω=Ω= 于博士信号完整性分析入门 于争 博士 https://www.360docs.net/doc/c76303958.html, for more information,please refer to https://www.360docs.net/doc/c76303958.html, 电设计网欢迎您 什么是信号完整性? 如果你发现,以前低速时代积累的设计经验现在似乎都不灵了,同样的设计,以前没问题,可是现在却无法工作,那么恭喜你,你碰到了硬件设计中最核心的问题:信号完整性。早一天遇到,对你来说是好事。 在过去的低速时代,电平跳变时信号上升时间较长,通常几个ns。器件间的互连线不至于影响电路的功能,没必要关心信号完整性问题。但在今天的高速时代,随着IC输出开关速度的提高,很多都在皮秒级,不管信号周期如何,几乎所有设计都遇到了信号完整性问题。另外,对低功耗追求使得内核电压越来越低,1.2v内核电压已经很常见了。因此系统能容忍的噪声余量越来越小,这也使得信号完整性问题更加突出。 广义上讲,信号完整性是指在电路设计中互连线引起的所有问题,它主要研究互连线的电气特性参数与数字信号的电压电流波形相互作用后,如何影响到产品性能的问题。主要表现在对时序的影响、信号振铃、信号反射、近端串扰、远端串扰、开关噪声、非单调性、地弹、电源反弹、衰减、容性负载、电磁辐射、电磁干扰等。 信号完整性问题的根源在于信号上升时间的减小。即使布线拓扑结构没有变化,如果采用了信号上升时间很小的IC芯片,现有设计也将处于临界状态或者停止工作。 下面谈谈几种常见的信号完整性问题。 反射: 图1显示了信号反射引起的波形畸变。看起来就像振铃,拿出你制作的电路板,测一测各种信号,比如时钟输出或是高速数据线输出,看看是不是存在这种波形。如果有,那么你该对信号完整性问题有个感性的认识了,对,这就是一种信号完整性问题。 很多硬件工程师都会在时钟输出信号上串接一个小电阻,至于为什么,他们中很多人都说不清楚,他们会说,很多成熟设计上都有,照着做的。或许你知道,可是确实很多人说不清这个小小电阻的作用,包括很多有了三四年经验的硬件工程师,很惊讶么?可这确实是事实,我碰到过很多。其实这个小电阻的作用就是为了解决信号反射问题。而且随着电阻的加大,振铃会消失,但你会发现信号上升沿不再那么陡峭了。这个解决方法叫阻抗匹配,奥,对了,一定要注意阻抗匹配,阻抗在信号完整性问题中占据着极其重要的 数字信号处理教案 余月华 课程特点: 本课程是为电子、通信专业三年级学生开设的一门课程,它是在学生学完了信号与系统的课程后,进一步为学习专业知识打基础的课程。本课程将通过讲课、练习使学生掌握数字信号处理的基本理论和方法。课程内容包括:离散时间信号与系统;离散变换及其快速算法;数字滤波器结构;数字滤波器设计;数字信号处理系统的实现等。 本课程逻辑性很强, 很细致, 很深刻;先难后易, 前三章有一定的难度, 倘能努力学懂前三章(或前三章的0080), 后面的学习就会容易一些;只要在课堂上专心听讲, 一般是可以听得懂的, 但即便能听懂, 习题还是难以顺利完成。这是因为数字信号分析技巧性很强, 只了解基本的理论和方法, 不辅以相应的技巧, 是很难顺利应用理论和方法的。论证训练是信号分析课基本的,也是重要的内容之一, 也是最难的内容之一。 因此, 理解证明的思维方式, 学习基本的证明方法, 掌握叙述和书写证明的一般语言和格式, 是信号分析教学贯穿始终的一项任务。 鉴于此, 建议的学习方法是: 预习, 课堂上认真听讲, 必须记笔记, 但要注意以听为主, 力争在课堂上能听懂七、八成。 课后不要急于完成作业, 先认真整理笔记, 补充课堂讲授中太简或跳过的推导, 阅读教科书, 学习证明或推导的叙述和书写。基本掌握了课堂教学内容后, 再去做作业。在学习中, 要养成多想问题的习惯。 课堂讲授方法: 1. 关于教材: 《数字信号处理》 作者 丁玉美 高西全 西安电子科技大学出版社 2. 内容多, 课时紧: 大学课堂教学与中学不同的是每次课介绍的内容很多, 因此, 内容重复的次数少, 讲课只注重思想性与基本思路, 具体内容或推导特别是同类型或较简的推理论证及推导计算, 可能讲得很简, 留给课后的学习任务一般很重。. 3. 讲解的重点: 概念的意义与理解, 理论的体系, 定理的意义、条件、结论、定理证明的分析与思路, 具有代表性的证明方法, 解题的方法与技巧,某些精细概念之间的本质差别. 在教学中, 可能会写出某些定理证明, 以后一般不会做特别具体的证明叙述. 4. 要求、辅导及考试: a. 学习方法: 适应大学的学习方法, 尽快进入角色。 课堂上以听为主, 但要做课堂笔记,课后一定要认真复习消化, 补充笔记,一般课堂教学与课外复习的时间比例应为1 : 3 。 b. 作业: 大体上每两周收一次作业, 一次收清。每次重点检查作业总数的三分之一。 作业的收交和完成情况有一个较详细的登记, 缺交作业将直接影响学期总评成绩。 c. 辅导: 大体两周一次。 d. 考试: 只以最基本的内容进行考试, 大体上考课堂教学和所布置作业的内容。 课程的基本内容与要求 第一章. 时域离散信号与时域离散系统 1. 熟悉6种常用序列及序列运算规则; 2. 掌握序列周期性的定义及判断序列周期性的方法; 3. 掌握离散系统的定义及描述方法(时域描述和频域描述); 4. 掌握LSI 系统的线性移不变和时域因果稳定性的判定; 第二章 时域离散信号与系统的傅立叶变换分析方法 DDR3基本知识 一、DDR3简介 DDR3(double-data-rate three synchronous dynamic random access memory)是应用在计算机及电子产品领域的一种高带宽并行数据总线。DDR3在DDR2的基础上继承发展而来,其数据传输速度为DDR2的两倍。同时,DDR3标准可以使单颗内存芯片的容量更为扩大,达到512Mb至8Gb,从而使采用DDR3芯片的内存条容量扩大到最高16GB。此外,DDR3的工作电压降低为1.5V,比采用1.8V的DDR2省电30%左右。说到底,这些指标上的提升在技术上最大的支撑来自于芯片制造工艺的提升,90nm甚至更先进的45nm制造工艺使得同样功能的MOS管可以制造的更小,从而带来更快、更密、更省电的技术提升。 DDR3的发展实在不能说是顺利,虽然在2005年就已经有最初的标准发布并于2007年应用于Intel P35 “Bearlake”芯片组上,但并没有像业界预想的那样很快替代DDR2,这中间还经历了对SDRAM业界影响深远的金融危机,不但使DDR3占领市场的速度更加减慢,还使DDR3在技术上一度走在世界领先地位的内存大厂奇梦达倒闭,实在是让人惋惜。虽然如此,DDR3现今是并行SDRAM家族中速度最快的成熟标准,JEDEC标准规定的DDR3最高速度可达1600MT/s(注,1MT/s即为每秒钟一百万次传输)。不仅如此,内存厂商还可以生产速度高于JEDEC标准的DDR3产品,如速度为2000MT/s的DDR3产品,甚至有报道称其最高速度可高达2500MT/s。 二、DDR存储器特性 1) 时钟的上升和下降沿同时传输数据 DDR存储器的主要优势就是能够同时在时钟循环的上升和下降沿提取 数据,从而把给定时钟频率的数据速率提高1倍。例如,在DDR200器件中,数据传输频率为200 MHz,而总线速度则为100 MHz。 2) 工作电压低 DDR1、DDR2和DDR3存储器的电压分别为2.5、1.8和1.5V,因此与采用3.3V的正常SDRAM芯片组相比,它们在电源管理中产生的热量更少,效率更高。 3) 延时小 延时性是DDR存储器的另一特性。存储器延时性可通过一系列数字体现,如用于DDR1的2-3-2-6-T1、3-4-4-8或2-2-2-5。这些数字表明存储器进行某一操作所需的时钟脉冲数,数字越小,存储越快。 这些数字代表的操作如下:CL- tRCD – tRP – tRAS – CMD。要理解它们,您必须牢记存储器被内部组织为一个矩阵,数据保存在行和列的交叉点。 ?CL:列地址选通脉冲(CAS)延迟,是从处理器发出数据内存请求到存储 信号完整性分析基础系列之二十四——关于抖动(上) 美国力科公司深圳代表处汪进进 写在前面的话 抖动话题是示波器测量的最高境界,也是最风云变换的一个话题,这是因为抖动是示波器测量的诸多功能中最和“数学”相关的。玩数学似乎是需要一定境界的。 “力科示波器是怎么测量抖动的?”,“这台示波器抖动测量准不准?”,“时钟抖动和数据抖动测量方法为什么不一样?”,“总体抖动和峰峰值抖动有什么区别? ”,“余辉方法测量抖动不是最方便吗?”,“抖动和眼图,浴盆曲线之间是什么?”,…… 关于抖动的问题层出不穷。这么多年来,在完成了“关于触发(上)、(下)”和“关于眼图(上)、(下)”,“关于S参数(上)(下)”等三篇拙作后,我一直希望有一篇“关于抖动”的文章问世,但每每下笔又忐忑而止,怕有谬误遗毒。今天,当我鼓起勇气来写关于抖动的时候,我需要特别说明,这是未定稿,恳请斧正。 抖动和波形余辉的关系 有一种比较传统的测量抖动的方法,就是利用余辉来查看信号边沿的变化,然后再用光标测量变化的大小(如图1所示),后来更进了一步,可以利用示波器的“余辉直方图”和相关参数自动测量出余辉的变化范围,这样测量的结果就被称为“抖动”。这个方法是在示波器还没有“测量统计”功能之前的方法,但在90年代初力科发明了测量统计功能之后,这个方法就逐渐被淘汰了。 图1 传统的抖动测量方法 这种传统的方法有下面这些缺点:(1)总会引入触发抖动,因此测量的结果很不准确。(2)只能测量某种参数的抖动,譬如触发上升沿,测量下降沿的余辉变化,反应了宽度的抖动,触发上升沿,测量相邻的上升沿的余辉变化,反应了周期的抖动。显然还有很多类型的抖动特别是最重要的TIE抖动无法测量出来。(3)抖动产生的因果关系的信息也无从得知。 定义抖动的四个维度 和抖动相关的名词非常多:时钟抖动,数据抖动; 周期抖动,TIE抖动,相位抖动,cycle-cycle抖动; 峰峰值抖动(pk-pk jitter),有效值抖动(rms jitter);总体抖动(Tj),随机抖动(Rj),固有抖动(Dj);周期性抖动,DCD抖动,ISI抖动,数据相关性抖动; 定时抖动,基于误码率的抖动; 水平线以上的抖动和水平线以下的抖动…… 这些名词反应了定义抖动的不同维度。 回到“什么是抖动”的定义吧。其实抖动的定义一直没有统一,这可能也是因为需要表达清楚这个概念的维度比较多的原因。目前引用得比较多的定义是: Jitter is defined as the short-term variations of a digital signal’s significant instants from their ideal positions in time. 就是说抖动是信号在电平转换时,其边沿与理想位置之间的偏移量。如图2所示,红色的是表示理想信号,实际信号的边沿和红色信号边沿之间的偏差就是抖动。什么是“理想位置”,“理想位置”是怎么得到的?这是被问到后最不好回答的问题。 DSP设计笔记 CPLD可以控制不同的复位信号。CPLD的寄存器映射到EMIF的CE1数据空间,它的地址是0x90080000。U12是CPLD。 SN74LVTH16245A是三态总线收发器。- OE 输出使能,DIR是直接控制输入端。DIC与- OE 的 状态决定着A、B两总线的传输方向。当他们同为低电位时,数据由B总线传输到A总线; 当- OE 为低DIR为高时,数据由A总线传输到B总线;当- OE 为高时,收发器处于不工作状态。 DSP与PC机的PCI总线高速数据传输 [日期: 2004-12-6] 来源:国外电子元器件作者:肖逾男宋元 胜 [字体:大中 小] 摘要:介绍了TI公司的高性能浮点式数字信号处理芯片TMS320C6713的接口信号及控制寄存器,并在此基础上,指出了该DSP通过PCI总线与PC机进行高速数据传输的实现方法,同时给出了TMS320C6713和PC机通过PCI9052总线接口芯片实现接口的硬件原理图。 关键词:DSP;数据传输;TMS320C6713 PCI9052 TMS320C6713是TI公司在TMS320C6711的基础上推出的C6000系列新一代浮点DSP芯片,它是目前为止C6000系列DSP芯片中性能最高的一种。TMS320C6713可在255MHz的时钟频率下实现1800MIPS/1350MFLOPS的定点和浮点运算,因而可极大地满足通信、雷达、数字电视等高科技领域对信号处理实时性的要求。同时其主机口(HPI)可灵活地和PCI总线控制器相连接。而PC机则可通过PCI总线控制器直接访问TMS320C6713的存储空间和外围设备,从而实现PC机与TMS320C6713之间的高速数据传输。 在上两篇文章中,我们分别介绍了直方图(统计域分析)和抖动追踪(时域分析)在抖动分析中的应用。从抖动的直方图和抖动追踪波形上我们可以得到抖动的主要构成成分以及抖动参数的变化趋势。如需对抖动的构成做进一步的分析,还需要从频域角度去进一步分析抖动的跟踪波形。 抖动的频谱即是对抖动追踪(jitter track)波形做FFT运算。如下图1所示 为一个时钟周期测量参数的追踪、频谱分析步骤及效果,在抖动频谱图上可以清楚的看出某两个频率值点抖动比较大: 图1 抖动频谱 黄色为实际采集到的时钟波形(C1通道) P1测量C1通道时钟信号的时钟周期 F7函数对P1测量参数进行跟踪 F6对F7进行FFT分析 下图2所示为一典型的串行信号抖动追踪频谱图,从图中可看出各种抖动成分;DDj和Pj为窄带频谱(三角形谱或者谱线)但是DDj和Pj的区别是由于DDj是和码型相关的,其频率fDDJ一般会是数据位率的整数倍,如果Pj的频率fPJ正好等于fDDJ,那么从抖动的频谱图里面是很难将DDj和Pj精确的分开的,所以通常在抖动分解的过程中一般通过时域平均的方法来分解DDj;BUj主要由于串扰等因素引起的,一般分为两种,一种是窄带,但幅度较高,很显然这类BUJ也是很难和PJ区分开的,除非我们知道引起BUJ的源头,知道其频率,所以说我们在抖动测试时得到的PJ一般会包含这类BUJ(所以通常情况下对这类BUJ不加区分,直接算做PJ,而将BUJ分类为PJ和OBUJ,在之前的抖动分类文章中有提及);另外一类是宽带的BUJ(很多时候也叫OBUJ,other bounded uncorrelated jitter),幅度很小,基本会埋没到RJ中去,这类抖动很容易被误算作RJ,目前使用在示波器上的抖动分解软件只有Lecroy最近推出的SDAII(基于NQ-SCALE抖动分解理论)能够较好的将这类抖动从Rj中剥离出来;RJ是 宽带频谱,幅度很小。 <数字信号处理的FPGA实现> Verilog写状态机大概有这样几点要求: 1、组合逻辑完成状态转移的条件判断,时序逻辑完成状态机的状态转移。 2、组合逻辑和时序逻辑分别在两个不同的always块中完成,根据状态机状态通过译码逻辑产生的与状态机无关的逻辑部分不要放在专用的状态机always块中。 3、状态编码预先定义为parameter,状态较少的状态机推荐使用one-hot方式编码,以减小译码逻辑的复杂度,提高性能。 4、建议单独使用一个模块来描述状态机。 5、状态机应有一个default状态,在上电复位的时候作为初始状态。 6、注意状态机组合逻辑中的if...else语句,不要出现latch。 7、对于复杂状态机,最好采用状态机嵌套方式完成。 其实上面很多都是按照Synopsys LEDA的coding style的要求的,状态机的写法相对固定,因此很多Design entry的工具可以自动生成状态机代码,Xilinx也有工具支持直接由状态转移图输入完成状态机的编码。所以关键还是画好状态转移图,其他就相对简单了。 visual hdl+ISE+synplify Pro+modelsim! 1.设计输入 1)设计的行为或结构描述。 2)典型文本输入工具有UltraEdit-32和Editplus.exe.。 3)典型图形化输入工具-Mentor的Renoir。 4)我认为UltraEdit-32最佳。 2.代码调试 1)对设计输入的文件做代码调试,语法检查。 2)典型工具为Debussy。 3.前仿真 1)功能仿真 2)验证逻辑模型(没有使用时间延迟)。 3)典型工具有Mentor公司的ModelSim、Synopsys公司的VCS和VSS、Aldec公司的Active、Cadense公司的NC。 4)我认为做功能仿真Synopsys公司的VCS和VSS速度最快,并且调试器最好用,Mentor 公司的ModelSim对于读写文件速度最快,波形窗口比较好用。 4.综合 1)把设计翻译成原始的目标工艺 2)最优化 3)合适的面积要求和性能要求 4)典型工具有Mentor公司的LeonardoSpectrum、Synopsys公司的DC、Synplicity公司的Synplify。 5)推荐初学者使用Mentor公司的LeonardoSpectrum,由于它在只作简单约束综合后的速度和面积最优,如果你对综合工具比较了解,可以使用Synplicity公司的Synplify。 5.布局和布线 1)映射设计到目标工艺里指定位置 2)指定的布线资源应被使用 信号链基础知识之几个关键的基本概念 一直有人说“一年数字,十年模拟。”。大致意思我猜是说:数字技术相对而言比较简单易懂,而模拟技术是非常深奥难以掌握的。我觉得即便这句话并非“空穴来风”,模拟电子技术也不可能离开那些非常基础的东西而成为美丽、高不可攀的“空中楼阁”。所以说,模拟电子技术的“深不可测”并不应该成为我们畏惧它的原因,相反,我们应该尽量把基础知识打扎实,迎难而上,去体会“模拟技术是一种艺术”! (1)输入失调电压(Input offset voltage——Vio): 定义:Vio是使输出电压为零时在运放输入端所加的一个补偿电压。 实际上,由于运放的输入级电路参数不可能绝对对称,所以当输入电压为零时,输出电压并不为零。内部两个差分晶体管的微小差异,通过A倍放大后,即可产生一个不容忽视的输出电压。下图是由输入偏移电压产生的一种极端情况(这个图已把问题说得简单、明了,我就不多说了), 由此可见,输入偏移电压有时可能使得运放输出级的工作状态进入非线性区。So,要想使运放工作在线性区的话,我们就不得不事先对运放进行调零的操作了!——进行人为地输入一个补偿电压。如下图所示: (2)输入失调电流(Input Offset Current——Iio): 碎碎念:对于FET运算放大器来说,由于其输入电阻是“出了名”的极大,以致该类运放的输入失调电流一般是极小的,不至于在运放的输入端产生额外严重的补偿电压。However,反观双极性运算放大器,其输入失调电流在多处情况下是令人无法忍受的,一个有效的处理办法是:尽量使得运放的同相与反相两端保持良好的对称状态,以减小输入失调电流。 (3)负反馈(Negative Feedback): 由于运放一般具有极大的开环电压增益,所以两个输入端即便是只有很小的电压差,运放的输出级也有可能轻易到达饱和区域。由此,运放几乎只能用于比较器应用了。但是,当引入负反馈后,运放就变成一种非常有用的器件了。引入负反馈能够给放大器的性能带来多方面的改善,比如可以稳定放大倍数、改变输入电阻和输出电阻、展宽频带、减小非线性失真等,考虑到博文的篇幅,留待后文再针对这些情况作专门的分析和讨论。 信号完整性背景 信号完整性问题引起人们的注意,最早起源于一次奇怪的设计失败现象。当时,美国硅谷一家著名的影像探测系统制造商早在7 年前就已经成功设计、制造并上市的产品,却在最近从生产线下线的产品中出现了问题,新产品无法正常运行,这是个20MHz 的系统设计,似乎无须考虑高速设计方面的问题,更为让产品设计工程师们困惑的是新产品没有任何设计上的修改,甚至采用的元器件型号也与原始设计的要求一致,唯一的区别是 IC 制造技术的进步,新采购的电子元器件实现了小型化、快速化。新的器件工艺技术使得新生产的每一个芯片都成为高速器件,也正是这些高速器件应用中的信号完整性问题导致了系统的失败。随着集成电路(IC)开关速度的提高,信号的上升和下降时间迅速缩减,不管信号频率如何,系统都将成为高速系统并且会出现各种各样的信号完整性问题。在高速PCB 系统设计方面信号完整性问题主要体现为:工作频率的提高和信号上升/下降时间的缩短,会使系统的时序余量减小甚至出现时序方面的问题;传输线效应导致信号在传输过程中的噪声容限、单调性甚至逻辑错误;信号间的串扰随着信号沿的时间减少而加剧;以及当信号沿的时间接近0.5ns 及以下时,电源系统的稳定性下降和出现电磁干扰问题。 信号完整性含义 信号完整性(Signal Integrity)简称SI,指信号从驱动端沿传输线到达接收端后波形的完整程度。即信号在电路中以正确的时序和电压作出响应的能力。如果电路中信号能够以要求的时序、持续时间和电压幅度到达IC,则该电路具有较好的信号完整性。反之,当信号不能正常响应时,就出现了信号完整性问题。从广义上讲,信号完整性问题指的是在高速产品中由互连线引起的所有问题,主要表现为五个方面: 信号完整性分析基础系列之一_——关于眼图测量(全) 您知道吗?眼图的历史可以追溯到大约47年前。在力科于2002年发明基于连续比特位的方法来测量眼图之前,1962年-2002的40年间,眼图的测量是基于采样示波器的传统方法。 您相信吗?在长期的培训和技术支持工作中,我们发现很少有工程师能完整地准确地理解眼图的测量原理。很多工程师们往往满足于各种标准权威机构提供的测量向导,Step by Step,满足于用“万能”的Sigtest软件测量出来的眼图给出的Pass or Fail结论。这种对于Sigtest 的迷恋甚至使有些工程师忘记了眼图是可以作为一项重要的调试工具的。 在我2004年来力科面试前,我也从来没有听说过眼图。那天面试时,老板反复强调力科在眼图测量方面的优势,但我不知所云。之后我Google“眼图”,看到网络上有限的几篇文章,但仍不知所云。刚刚我再次Google“眼图”,仍然没有找到哪怕一篇文章讲透了眼图测量。 网络上搜到的关于眼图的文字,出现频率最多的如下,表达得似乎非常地专业,但却在拒绝我们的阅读兴趣。 “在实际数字互连系统中,完全消除码间串扰是十分困难的,而码间串扰对误码率的影响目前尚无法找到数学上便于处理的统计规律,还不能进行准确计算。为了衡量基带传输系统的性能优劣,在实验室中,通常用示波器观察接收信号波形的方法来分析码间串扰和噪声对系统性能的影响,这就是眼图分析法。 如果将输入波形输入示波器的Y轴,并且当示波器的水平扫描周期和码元定时同步时,适当调整相位,使波形的中心对准取样时刻,在示波器上显示的图形很象人的眼睛,因此被称为眼图(Eye Map)。 二进制信号传输时的眼图只有一只“眼睛”,当传输三元码时,会显示两只“眼睛”。眼图是由各段码元波形叠加而成的,眼图中央的垂直线表示最佳抽样时刻,位于两峰值中间的水平线是判决门限电平。 在无码间串扰和噪声的理想情况下,波形无失真,每个码元将重叠在一起,最终在示波器上看到的是迹线又细又清晰的“眼睛”,“眼”开启得最大。当有码间串扰时,波形失真,码元不完全重合,眼图的迹线就会不清晰,引起“眼”部分闭合。若再加上噪声的影响,则使眼图的线条变得模糊,“眼”开启得小了,因此,“眼”张开的大小表示了失真的程度,反映了码间串扰的强弱。由此可知,眼图能直观地表明码间串扰和噪声的影响,可评价一个基带传输系统性能的优劣。另外也可以用此图形对接收滤波器的特性加以调整,以减小码间串扰和改善系统的传输性能。通常眼图可以用下图所示的图形来描述,由此图可以看出:(1)眼图张开的宽度决定了接收波形可以不受串扰影响而抽样再生的时间间隔。显然,最佳抽样时刻应选在眼睛张开最大的时刻。 (2)眼图斜边的斜率,表示系统对定时抖动(或误差)的灵敏度,斜率越大,系统对定时抖动越敏感。 浅谈数字信号处理 20091111 崔琦中文摘要: 数字信号处理的目的是对真实世界的连续模拟信号进行测量或滤波。因此在进行数字信号处理之前需要将信号从模拟域转换到数字域,这通常通过模数转换器实现。而数字信号处理的输出经常也要变换到模拟域,这是通过数模转换器实现的。 关键词:数字信号处理;芯片发展;应用 ABSTRACT: The purpose of digital signal processing is the real world of continuous analog signals measured or filter. Therefore in digital signal processing is needed before will signal from analog to digital domain, the field that usually through the adc. And digital signal processing output often will transform into analog domain, it is realized by digital-to-analog converters. Keywords:Digital signal processing;Chip development;application 正文: 数字信号处理作为信号和信息处理的一个分支学科,已渗透到科学研究、技术开发、工业生产、国防和国民经济的各个领域,取得了丰硕的成果。对信号在时域及变换域的特性进行分析、处理,能使我们对信号的特性和本质有更清楚的认识和理解,得到我们需要的信号形式,提高信息的利用程度,进而在更广和更深层次上获取信息。DSP芯片,也称数字信号处理器,是一种特别适合进行数字信号处理运算的微处理器。DSP芯片的出现和发展,促进数字信号处理技术的提高,许多新系统、新算法应运而生,其应用领域不断拓展。目 信号完整性分析与测试 信号完整性问题涉及的知识面比较广,我通过这个短期的学习,对信号完整性有了一个初步的认识,本文只是简单介绍和总结了几种常见现象,并对一些常用的测试手段做了相应总结。本文还有很多不足,欢迎各位帮助补充,谢谢! 梁全贵 2011年9月16日 目录 第1章什么是信号完整性------------------------------------------------------------------------------ 3第2章轨道塌陷 ----------------------------------------------------------------------------------------- 5第3章信号上升时间与带宽 --------------------------------------------------------------------------- 6第4章地弹----------------------------------------------------------------------------------------------- 8第5章阻抗与特性阻抗--------------------------------------------------------------------------------- 9 5.1 阻抗 ------------------------------------------------------------------------------------------ 9 5.2 特性阻抗------------------------------------------------------------------------------------- 9第6章反射----------------------------------------------------------------------------------------------11 6.1 反射的定义 ---------------------------------------------------------------------------------11 6.2 反射的测试方法--------------------------------------------------------------------------- 12 6.3 TDR曲线映射着传输线的各点 --------------------------------------------------------- 12 6.4 TDR探头选择 ----------------------------------------------------------------------------- 13 第7章振铃--------------------------------------------------------------------------------------------- 14 第8章串扰--------------------------------------------------------------------------------------------- 16 8.1 串扰的定义 -------------------------------------------------------------------------------- 16 8.2 观测串扰 ----------------------------------------------------------------------------------- 16 第9章信号质量 --------------------------------------------------------------------------------------- 18 9.1 常见的信号质量问题 --------------------------------------------------------------------- 18 第10章信号完整性测试 ----------------------------------------------------------------------------- 21 10.1 波形测试---------------------------------------------------------------------------------- 21 10.2 眼图测试---------------------------------------------------------------------------------- 21 10.3 抖动测试---------------------------------------------------------------------------------- 23 10.3.1 抖动的定义 ------------------------------------------------------------------------ 23 10.3.2 抖动的成因 ------------------------------------------------------------------------ 23 10.3.3 抖动测试 --------------------------------------------------------------------------- 23 10.3.4 典型的抖动测试工具: ---------------------------------------------------------- 24 10.4 TDR测试 --------------------------------------------------------------------------------- 24 10.5 频谱测试---------------------------------------------------------------------------------- 25 10.6 频域阻抗测试 ---------------------------------------------------------------------------- 25 10.7 误码测试---------------------------------------------------------------------------------- 25 10.8 示波器选择与使用要求: -------------------------------------------------------------- 26 10.9 探头选择与使用要求-------------------------------------------------------------------- 26 10.10 测试点的选择--------------------------------------------------------------------------- 27 10.11 数据、地址信号质量测试 ------------------------------------------------------------- 27 10.11.1 简述 ------------------------------------------------------------------------------- 27 10.11.2 测试方法-------------------------------------------------------------------------- 27DDR的基础知识

于博士信号完整性分析入门-初稿

DSP汇编指令学习笔记

信号完整性分析基础系列之一——眼图测量

数字信号处理学习心得

于博士信号完整性分析入门(修改)

数字信号处理教案

DDR3基本知识

信号完整性分析基础系列之二十四

DSP设计笔记

信号完整性分析基础之八——抖动的频域分析

《数字信号处理的FPGA实现》读书笔记

信号链基础知识之几个关键的基本概念

信号完整性分析

信号完整性分析基础系列之一__关于眼图测量(全)

谈谈对数字信号处理(DSP)的认识

信号完整性分析与测试