四位数字的电子锁电路数电课程设计word精品

四位数字的电子锁电路设计

1四位数字的电子锁设计

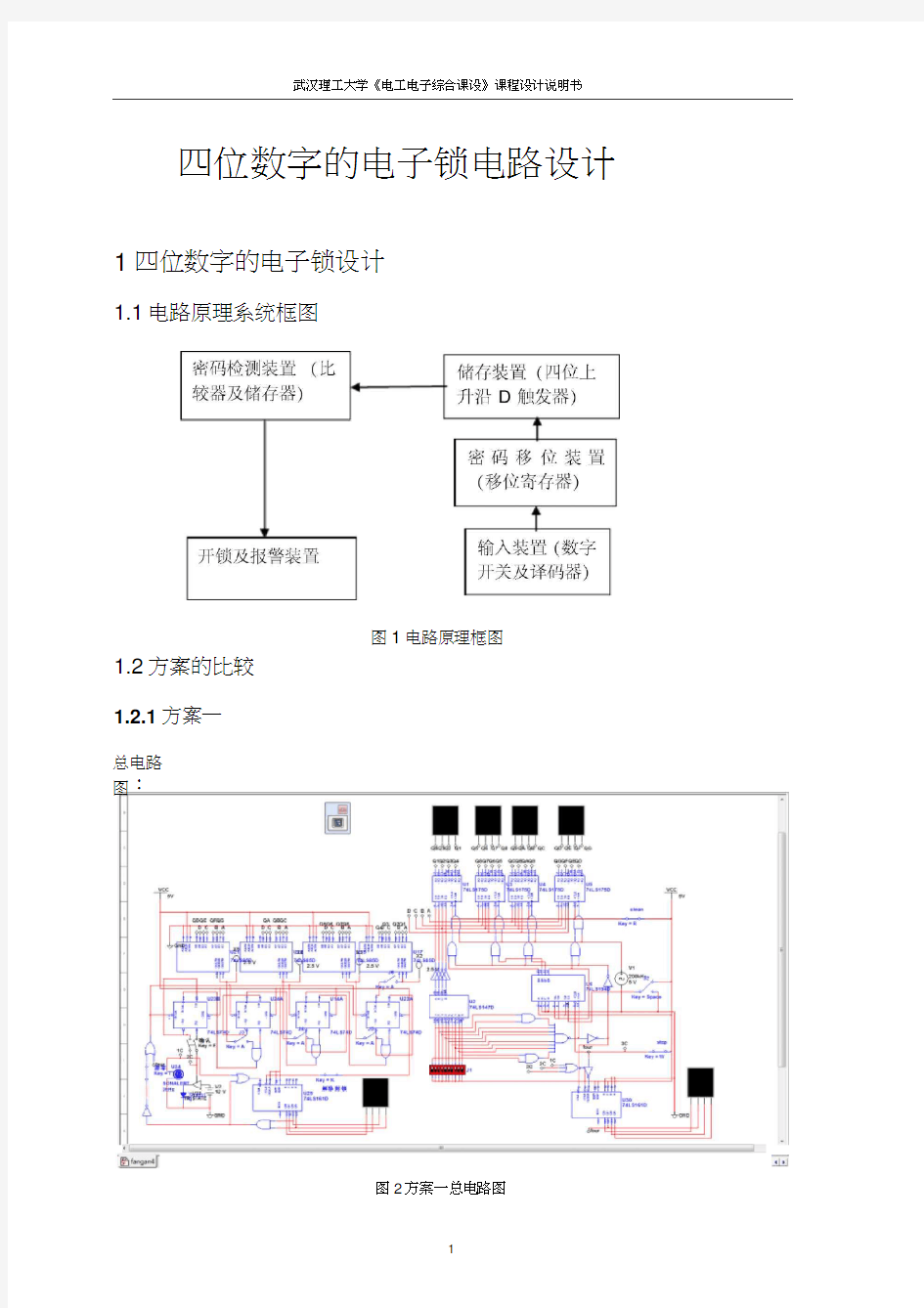

1.1电路原理系统框图

1.2方案的比较

1.2.1方案一

总电路

图:

图2方案一总电路图

图1电路原理框图

原理说明:由数字开关与译码器输入密码,按键输入触发接成环形计数器的移位寄 存器,计数器记录密码输入个数来和控制各锁存器时钟端来使显示稳定,四位锁存 器时钟开关按下,

74LS175存储密码,之后4个锁存器依次检测四个等于信号的输出, 若依次为一,则正确,

否则错误。计数器控制一次输入密码个数最多为四,超过则 错误。密码比较使用74LS85四位数值比较器级联,只能依次输入正确密码触发74IS74 给信号输出正确密匙,输出结果驱动由传输门控制密码子正确是的开锁显示,正确 密码则led 灯亮解锁,反之蜂鸣器发出警报.

1.1.2方案二

总原理图:

原理说明:如上电路图所示,由数字开关与译码器输入密码,分配器和锁存器分配 数据显示在数码管上,计数器记录密码输入个数来控制数据分配和控制各锁存器时 钟端来使显示稳定,四位锁存器时钟开关按下,

74LS175存储当前,密码比较使用

图3方案二的总电路图

74LS85四位数值比较器级联,输出结果驱动由传输门控制密码子正确是的开锁显示, 以及密码错误的蜂鸣器报警。

1.3方案的选择

两个方案相同之处:使用了编码器及反相器作为密码输入部分,用与非门进行电路

输入错误信号是的封锁,密码检测部分都用了74IS85比较器用来对二次密码的检测

和比较。两方案制作都需要一定量芯片,制作成本较高;

不同之处:方案一具备完备功能,满足实验全部要求,线路中用了网络标号做线路连接,使电路图简单美观,输入部分用了移位寄存器对输入信号移位已输入四位密码;方案二初步功能虽具备,但电路封锁后仍可改变末尾密码,有弊端,且整个电路图接线复杂,难制作出实物,用的是数据分配器对输入密码进行分配,74IS175对信号进行多次储存,计算复杂。综合比较两方案,选择方案一为佳。

2整体设计方案的分析

2.1输入单元电路

电路图示:

图4输入单元电路图

原理说明:信号输入数J1开关,经74IS147编码器及反相器向储存器传输转化为二进制数,同时有方向加载个八位与非门及74IS194移位寄存器进行封锁及移位,

74IS161计数器计数对数字输入信号进行计数,开关space对寄存器预置数,初始值

为1000,开关w打开切断寄存器清除端低电平,输出低电平,不进行数字移位而由检测装置移位检测。

74LS147引脚图及功能表:

Vec 丫3 亍3 】殳1j Tg Yo

16 15 14 13 12 H 10 9

74147

74LS147

12 3 4 5 6 7 8

Q 6 Q 6 a d 6 o

L T5U I T T s% Yj 地

图5 74IS147引脚图

管脚图:引出端符号:1-9 编码输入端(低电平有效)ABCD 编码输出端(低电平有效)表1 4IS147 功能表

输入输出

) 2 3 4 5 6789 D C B A

HHHHHHHHH H H H H

XXXXXXXXL L H H L

XXXXXXXHH L H H H

XXXXXXHHH H L L L

XXXXXHHHH H L L H

XXXXHHHHH H L H L

XXXHHHHHH H H H H

XXHHHHHHH H r H L L

XLHHHHHHH H H L H

LHHHHHHHH H H H L

功能说明:74LS147优先编码器有9个输入端和4个输出端。某个输入端为0,代表输入某一个十进制数。当9个输入端全为1时,代表输入的是十进制数0。4个输出端反映输入十进制数的BCD码编码输出。

74LS147优先编码器的输入端和输出端都是低电平有效,即当某一个输入端低电平0

时,4个输出端就以低电平0的输出其对应的8421 BCD 编码。当9个输入全为1时,

4个输入出也全为1,代表输入十进制数0的8421 BCD 编码输出。

74IS194引脚图及功能表:

图6 74IS194引脚图 CP

CR Si Sa

功畤 Q> Q J QiQo

X

X

MM

存=0£时,Q^Q^QiQ)=0G00

正常工作时?CAS 1

1 1 1

I

Q B Q J Q J Q O ~1? 此时串厅融据< St ■诡篆止

t J

I □ J I

QjQlQ 「也 Q 事 Q= Q L t 1 I 0

QsQaQiQo^QaQiCiPsL t

1 0 0

QiQiQ iQo=Qf k Q/k Q^Qd h

4

1

X

X

保持 Q? QaQ x Q Q ?QTQ 尹Q 尸 QcT

功能说明:当清除端(CLEAR 为低电平时,输出端(QA- QD 均为低电平。当工作 方式控制端(S0 S1)均为高电平时,在时钟(CLOCK 上升沿作用下,并行数据(A —D )被送入相应的输出端 QA- QD 此时串行数据(DSR DSI )被禁止。当S0为高 电平、S1为低电平时,在

CLOC 上升沿作用下进行右移操作,数据由 DSR 送入。当 S0为低电平、S1为高电平时,在CLOC 上升沿作用下进行操作,数据由 DSR 送入。

当S0和S1均为低电平时CLOC 被禁止。74LS194只有当CLOCI 为高电平时S0和S1 才可改变。

s S] %

Do

Di

6

6

S L

CP CR

16

VccQaQj Q 3 Q 咅 CP 沁

74LS194

CR S R D 。D I D 】D 扌 S L V SS

Y

图7储存单元电路图

原理说明:此部分由四个 74IS175上升沿触发的四位D 触发器作为储存器,开关 R 接175清零端低电平有效,打开 R 即清零储存器,图上显示器置于密码锁内部只做 测试点录用,网络标号分别对应节点。

74IS175引脚图及真值表:

2.2储存单元

电路图示:

750

:

二"二"

2■自亡亡二.二, 亍

F 好T 谆T 审号

4LS175D ] I ...?g 琴

U4:: 7JLS1 5D ............

U5 :::

:

08070605: : QCQBQAQ9

Q1Q2Q3O :

A - A .

. A ...................-

- ■

:'QGQFQEQD

-? ------------ TTi

----------

P

—*

—

—

74ALS175h 为一四路的锁存器,当CLK 引脚输入上涨沿时,1D-4D 被锁存到输出端(1Q-4Q 。在CLK 其他状态时,输出与输入无关。

2.3检测单元

电路图示:

vcc

原理说明:此部分用了四个 74IS85D 数值比较器及四个D 触发器作为储存器,当二 次输入密码,通过储存部分 ABCD 端 口,当输出正确顺序的密码,比较器输出 A=B 端 高电位依次触发D 触发器翻转,最后输出比较结果。

QDQE QFQG

QA QBOC

1 ■1 ■ i

忡卄Btt

''

DC

■ i

DC B A

7 阳 tttt

卜

mum

表3 74IS175功能表

5V

0 c e A

* s - s L 图9检测单元电路图 s 数字电路课程设计 数字时钟 《数字时钟》技术报告 概要 数字钟是一个将“时”,“分”,“秒”显示于人的视觉器官的计时装置。它的计时周期为24小时,显示满刻度为23时59分59秒。一个基本的数字钟电路主要由秒信号发生器、“时、分、秒、”计数器、译码器及显示器组成。由于采用纯数字硬件设计制作,与传统的机械表相比,它具有走时准,显示直观,无机械传动装置等特点。 本设计中的数字时钟采用数字电路实现对“时”、“分”、“秒”的显示和调整。经过采用各种集成数字芯片搭建电路来实现相应的功能。具体用到了555震荡器,74LS90及与非,异或等门集成芯片等。该电路具有计时和校时的功能。 在对整个模块进行分析和画出总体电路图后,对各模块进行仿真并记录仿真所观察到的结果。 实验证明该设计电路基本上能够符合设计要求! 一、系统结构。 (1)功能。 此数字钟能显示“时、分、秒”的功能,它的计时周期是24 小时,最大能显示23时59分59秒,并能对时间进行调整和校对,相对于机械式的手表其更为准确。 (2)系统框图。 系统方框图1 (3)系统组成。 1.秒发生器:由555芯片和RC组成的多谐振荡器,其555上3的输出频率由接入的电阻与电容决定。 2.校时模块:由74LS03中的4个与非门和相应的开关和电阻构成。 3.计数器:由74LS90中的与非门、JK触发器、或门构成相应芯片串接得到二十四、六十进制的计数器,再由74LS90与74LS08相 连接而得到秒、分、时的进分别进位。 4.译码器:选用BCD锁存译码器4511,接受74LS90来的信号,转换为7段的二进制数。 5.显示模块:由7段数码管来起到显示作用,经过接受CD4511的信号。本次选用的是共阴型的CD4511。 二、各部分电路原理。 三、秒发生器:555电路内部(图2-1)由运放和RS触发器共同组成,其工作原理由8处接VCC,C1处当Uco=2/3Vcc>u11时运放输出为1,同理C2也一样。最终如图3接口就输出矩形波,而形成的秒脉冲。 图2-1 内部结构图 一、选择正确答案填入空内,只需填入A 、B 、C 、D 1.已知图示电路中晶体管的100≈β,Ω≈k 1be r ,在输入电压为有效值等于10mV 的1kHz 正弦信号时,估计输出电压有效值为____。( A .0.5V , B .1V , C .2V , D .5V )。 2k Ω L 2. 放大电路如图所示,已知硅三极管的50=β,则该电路中三极管的工作状态为( )。 3. 放大电路如图所示,已知三极管的05=β,则该电路中三极管的工作状态为( )。 4. 放大电路A 、B 的放大倍数相同,但输入电阻、输出电阻不同,用它们对同一个具有内阻 的信号源电压进行放大,在负载开路条件下测得A 的输出电压小,这说明A 的( )。 A. 输入电阻大 B. 输入电阻小 C. 输出电阻大 D.输出电阻小 5. 关于三极管反向击穿电压的关系,下列正确的是( )。 A. EBO BR CBO BR CEO BR U U U )()()(>> B. EBO BR CEO BR CBO BR U U U )()()(>> A. 截止 B. 饱和 C. 放大 D. 无法确定 A. 截止 B. 饱和 C. 放大 D. 无法确定 C. CEO BR EBO BR CBO BR U U U )()()(>> D. CBO BR CEO BR EBO BR U U U )()()(>> 6. 在三极管放大电路中,下列等式不正确的是( )。 A.C B E I I I += B. ?B C I βI C. CEO CBO I I )1(β+= D. βααβ=+ 7. 图示电路中,欲增大U CEQ ,可以( )。 A. 增大Rc B. 增大R L C. 增大R B1 D. 增大β 8、射极输出电路如图所示,分析在下列情况中L R 对输出电压幅度的影响,选择:2 (1).保持i U 不变,将L R 减小一半,这时o U 将____; (2).保持s U 不变,将L R 减小一半,这时o U 将____。 (A .明显增大, B .明显.减小, C .变化不大) 9、在共射、共集、共基三种组态的放大电路中____的电压放大倍数u A 一定小于1,____的电流放大倍数i A 一定小于1,____的输出电压与输入电压反相。(A .共射组态, B .共集组态, C .共基组态) 10、已知图示电路中晶体管的50≈β,Ω≈k 2be r ,在输入电压为有效值等于10mV 的1kHz 正弦信号时,估计输出电压有效值为________。( A .0.2V , B .0.5V , C .1V , D .2V ) 数字电路课程设计题目选编 1、基于DC4011水箱水位自动控制器的设计与实现 简介及要求:水箱水位自动控制器,电路采用CD4011 四与非门作为处理芯片。要求能够实现如下功能:水 箱中的水位低于预定的水位时,自动启动水泵抽水; 而当水箱中的水位达到预定的高水位时,使水泵停止 抽水,始终保持水箱中有一定的水,既不会干,也不 会溢,非常的实用而且方便。 2、基于CD4011声控、光控延时开关的设计与实现 简介及要求:要求电路以CD4011作为中心元件,结合外围 电路,实现以下功能:在白天或光线较亮时,节电开关呈关闭 状态,灯不亮;夜间或光线较暗时,节电开关呈预备工作状态, 当有人经过该开关附近时,脚步声、说话声、拍手声等都能开 启节电开关。灯亮后经过40秒左右的延时节电开关自动关闭, 灯灭。 3、基于CD4011红外感应开关的设计与实现 在一些公共场所里,诸如自动干手机、自动取票机等,只要人手在机器前面一晃,机器便被启动,延时一段时间后自动关闭,使用起来非常方便。要求用CD4011设计有此功能的红外线感应开关。 4、基于CD4011红外线对射报警器的设计与实现 设计一款利用红 外线进行布防的防盗 报警系统,利用多谐振 荡器作为红外线发射 器的驱动电路,驱动红 外发射管,向布防区内 发射红外线,接收端利用专用的红外线接收器件对发射的 红外线信号进行接收,经放大电路进行信号放大及整形, 以CD4011作为逻辑处理器,控制报警电路及复位电路,电 路中设有报警信号锁定功能,即使现场的入侵人员走开,报警电路也将一直报警,直到人为解除后方能取消报警。 5、基于CD4069无线音乐门铃的设计与实现 音乐门铃已为人们所熟知,在一些住宅楼中都 装有音乐门铃,当有客人来访时,只要按下门铃按 钮,就会发出“叮咚”的声音或是播放一首乐曲, 然而在一些已装修好的室内,若是装上有线门铃, 由于必须布线,从而破坏装修,让人感到非常麻烦。 采用CD4069设计一款无线音乐门铃,发射按键与接 收机间采用了无线方式传输信息。 6、基于时基电路555“叮咚”门铃的设计与实现 用NE555集成电路设计、制作一个“叮咚”门铃,使该装置能够 发出音色比较动听的“叮咚”声。 7、基于CD4511数显八路抢答器的设计与实现 CD4511是一块含BCD-7段锁存、译码、驱动电路于一体的集成 电路。设计一款基于CD4511八路抢答器,该电路包括抢答,编 码,优先,锁存,数显和复位。 8、基于NE555+CD4017流水彩灯的设计与实现 以NE555和CD4017为核心,设计制作一个流水彩灯,使之通 过调节电位器旋钮,可调整彩灯的流动速度。 9、基于用CD4067、CD4013、 NE555跑马灯的设计与实 现 天津职业技术师范大学电子工程学院电子技术之---万用表课程设计报告 同组学生姓名(学号):寡人猪八戒 任务分工::查阅资料设计电路并进行电脑仿真, 焊接电路并参与电路的安装与调试 负责撰写课程设计及实验总结的工作 设计时间:2012年04月28日——2012 年05月04日 指导教师: 一、课程设计的目的与要求(含设计指标) 1、设计目的 (1)了解ICL7107芯片工作原理及应用。 (2)能够使用电路仿真软件进行电路调试。 (3)掌握电子系统的一般设计方法。 (4)培养综合应用所学知识来指导实践的能力。 (5)掌握常用元器件的识别和测试。 (6)熟悉常用仪表,了解电路调试的基本方法。 2、设计要求 (1)提出具体方案 (2)给出所设计电路的原理图。 (3)进行电路仿真设计 (4)设计电路所需的直流电源。 (5)用分立元件和运放设计的万用表电路要求先用multisim进行电路仿真分析,仿真结果正确后,在进行安装调试。 3、设计指标 直流电压表:满量程+6V; 直流电流表:满量程10mA; 交流电压表:满量程6V,50HZ~1KHZ; 交流电流表:满量程10mA; 欧姆表:满量程分别为1KΩ,10KΩ,100KΩ 三、方案论证及选择 设计万用电表,总体来说有两种设计方案,来源于万用电表的指针式和数字式的两种类型。指针式万用电表,需有表头,同时主要用HA17741,LM324N等芯片,借助集成运放实现万用电表。但是考虑到表头的应用,还有本课题其他组同学采用这个方案,我们则采用了另一种方案,设计数字式万用电表。主要运用ICL7107来实现,ICL7107是高性能、低功耗的三位半A/D转换器电路。它包含七段译码器、显示驱动器、参考源和时钟系统,ICL7107可直接驱动发光二极管。所以,用此芯片可以直接把模拟信号转换成数字信号,然后通过数码管显示出来。在数据采集时,采用分开设计,直流电压测量电路,直流电流测量电路,欧姆表测量电路,交流电流、电流测量电路。 三、原理设计(或基本原理) (1)基本原理:ICL7107是高性能、低功耗的三位半A/D转换器电路。它包含七段译码器、显示驱动器、参考源和时钟系统,ICL7107可直接驱动发光二极管。ICL7107 是双积型的A/D 转换器,还集成了A/D 转换器的模拟部分电路,如缓冲器、积分器、电压比较器、正负电压参考源和模拟开关,以及数字电路部分如振荡源、计数器、锁存器、译码器、驱动器和控制逻辑电路等,使用时只需外接少量的电阻、电容元件和显示器件,就可以完成模拟到数字量的转换,从而满足设计要求。 — 四川工业科技学院 电子信息工程学院课程设计 专业名称: 电子信息工程 课程名称:数字电路课程设计 \ 课题名称:自动节能灯设计 设计人员:蔡志荷 指导教师:廖俊东 2018年1月10日' 《模拟电子技术课程设计》任务书 一、课题名称:数字钟的设计 二、技术指标: (1)掌握数字钟的设计、组装和调试方法。 (2)熟练使用proteus仿真软件。 (3)熟悉各元件的作用以及注意事项。 三、要求: (1)设画出总体设计框图,以说明数字钟由哪些相对独立的功能模块组成,标出各个模块之间互相联系。 (2)设计各个功能模块的电路图,加上原理说明。 (3)选择合适的元器件,设计、选择合适的输入信号和输出方式,确保电路正确性。 指导教师:廖俊东 学生:蔡志荷 电子信息工程学院 2018 年 1 月 10 日 课程设计报告书评阅页 课题名称:数字钟的设计 班级:15级电子信息工程4班 姓名:蔡志荷 2018 年 1 月 10 日指导教师评语: 考核成绩:指导教师签名: 20 年月 目录 摘要 .......................................................错误!未定义书签。第1章设计任务与要求........................................错误!未定义书签。 设计指标数字钟简介......................................错误!未定义书签。 具体要求................................................错误!未定义书签。 设计要求................................................错误!未定义书签。第2章元件清单及主要器件介绍................................错误!未定义书签。 元件清单................................................错误!未定义书签。 主要器件介绍............................................错误!未定义书签。 74LS90计数.........................................错误!未定义书签。 74LS47 ..............................................错误!未定义书签。 七段数码显示器......................................错误!未定义书签。第3章设计原理与电路........................................错误!未定义书签。 计时电路................................................错误!未定义书签。 计秒、计分电路......................................错误!未定义书签。 计时电路...........................................错误!未定义书签。 校时电路................................................错误!未定义书签。 报时锁存信号........................................错误!未定义书签。 报时................................................错误!未定义书签。第4章仿真结果及误差分析....................................错误!未定义书签。 实验结果................................................错误!未定义书签。 实时分析................................................错误!未定义书签。第5章设计总结..............................................错误!未定义书签。参考文献......................................................错误!未定义书签。 课程设计报告 学生姓名:张浩学学号:201130903013 7 学 院:电气工程学院 班 级: 电自1116(实验111) 题 目: 模电音频功率放大电路设计 指导教师:张光烈职称: 2013 年 7月 4 日 1、设计题目:音频功率放大电路 2、设计任务目的与要求: 要求:设计并制作用晶体管和集成运算放大器组成的音频功率放大电路,负载为扬声器,阻抗8。 指标:频带宽50HZ~20kHZ,输出波形基本不失真;电路输出功率大于8W;输入灵敏度为100mV,输入阻抗不低于47KΩ。 模电这门课程主要讲了二极管,三极管,几种放大电路,信号运算与处理电路,正弦信号产生电路,直流稳压电源。功率放大器的作用是给音响放大器的负载RL(扬声器)提供一定的输出频率。当负载一定时,希望输出的功率尽可能大,输出的信号的非线性失真尽可能小,效率尽可能高。功率放大器的常见电路形式有OTL电路和OCL电路。有用继承运算放大器和晶体管组成的功率放大器,也有专集成电路功率放大器。本实验设计的是一个OTL功率放大器,该放大器采用复合管无输出耦合电容,并采用单电源供电。主要涉及了放大器的偏置电路克服交越失真,复合管的基本组合提高电路功率,交直流反馈电路,对称电路,并用multism软件对OTL 功率放大器进行仿真实现。根据电路图和给定的原件参数,使用multism 软件模拟电路,并对其进行静态分析,动态分析,显示波形图,计算数据等操作。 3、整体电路设计: ⑴方案比较: ①利用运放芯片 LM1875和各元器件组成音频功率放大电路,有保护电路,电源分别接+30v和-30v并且电源功率至少要50w,输出功率30w。 ②利用运放芯片TDA2030和各元器件组成音频功率放大电路,有保护电路,电源只需接+19v,另一端接地,负载是阻抗为8Ω的扬声器,输出功率大于8w。 通过比较,方案①的输出功率有30w,但其输入要求比较苛刻,添加了实验难度。而方案②的要求不高,并能满足设计要求,所以选取方案②来进行设计。 ⑵整体电路框图: 实验三旋转灯光电路与追逐闪光灯电路 一、实验目的 1.熟悉集成电路CD4029、CD4017、74LS138的逻辑功能。 2.学会用74LS04、CD4029、74LS138组装旋转灯光电路。 3. 学会用CD4069、CD4017组装追逐闪光灯电路。 二、实验电路与原理 1.旋转灯光电路: 图3-1 旋转灯光电路 将16只发光二极管排成一个圆形图案,按照顺序每次点亮一只发光二极管,形成旋转灯光。实现旋转灯光的电路如图3-1所示,图中IC1、R1、C1组成时钟脉冲发生器。IC2为16进制计数器,输出为4位二进制数,在每一个时钟脉冲作用下输出的二进制数加“1”。计数器计满后自动回“0”,重新开始计数,如此不断重复。 输入数据的低三位同时接到两个译码器的数据输入端,但是否能有译码器输出取决于使能端的状态。输入数据的第四位“D”接到IC3的低有效使能端G2和IC4的高有效使能端G1,当4位二进制数的高位D为“0”时,IC4的G1为“0”,IC4的使能端无效,IC4无译码输出,而IC3的G2为“0”,IC3使能端全部有效,低3位的CBA数据由IC3译码,输出D=0时的8个输出,即低8位输出(Y0~Y7)。当D为“1”时IC3的使能端处于无效状态,IC3无译码输出;IC4的使能端有效,低3位CBA数据由IC4译码,输出D=1时的8个输出,即高8位输出(Y8~Y15)。 由于输入二进制数不断加“1”,被点亮的发光二极管也不断地改变位置,形成灯光地“移动”。改变振荡器的振荡频率,就能改变灯光的“移动速度”。 注意:74LS138驱动灌电流的能力为8mA,只能直接驱动工作电流为5mA的超高亮发光二极管。若需驱动其他发光二极管或其他显示器件则需要增加驱动电路。 2. 追逐闪光灯电路 图 3-2 追 逐 闪 光 灯 电 路 ( 1) . CD 401 7 的 管 脚功能 CD4017集成电路是十进制计数/时序译码器,又称十进制计数/脉冲分频器。它是4000系列CMOS数字集成电路中应用最广泛的电路之一,其结构简单,造价低廉,性能稳定可靠,工艺成熟,使用方便。它与时基集成电路555一样,深受广大电子科技工作者和电子爱好者的喜爱。目前世界各大通用数字集成电路厂家都生产40171C,在国外的产品典型型号为CD4017,在我国,早期产品的型号为C217、C187、CC4017等。 (2)CD4017C管脚功能 CMOSCD40171C采用标准的双列直插式16脚塑封,它的引脚排列如图3-3(a)所示。 CC4017是国标型号,它与国外同类产品CD4017在逻辑功能、引出端和电参数等方面完全相同,可以直接互换。本书均以CD40171C为例进行介绍,其引脚功能如下: ①脚(Y5),第5输出端;②脚(Y1),第1输出端,⑧脚(Yo),第0输出端,电路清零 时,该端为高电平,④脚(Y2),第2输出端;⑤脚(Y6),第6输出端;⑥脚(Y7),第7输出端;⑦脚(Y3),第3输出端;⑧脚(Vss),电源负端;⑨脚(Y8),第8输出端,⑩脚(Y4),第4输出端;11脚(Y9),第9输出端,12脚(Qco),级联进位输出端,每输入10个时钟脉冲,就可得一个进位输出脉冲,因此进位输出信号可作为下一级计数器的时钟信号。13脚(EN),时钟输入端,脉冲下降沿有效;14脚(CP),时钟输入 数字电子技术基础课程设计DT-830B数字万用表报告 三亚学院 2011~2012学年第2学期 数字电子技术基础课程设计报告 学院: 理工学院 专业: 测控技术与仪器 班级: 学号: 学生姓名: 指导教师: 2012年9月7日 目录 一、设计任务与要求……………………………………… 二、电路原理……………………………………………… 三、总原理图及元器件清单……………………………… 四、装配过程……………………………………………… 五、电路功能测试………………………………………… 六、结论与心得…………………………………………… DT-830B数字万用表的组装与调试 一、设计任务与要求 1、设计要求: 学习了解DT830B数字万用表,熟悉它的工作原理。然后安装并调试数字万用表。通过对DT830B数字万用表的安装与调试实训,了 解数字万用表的特点,熟悉装配数字万用表的基本工艺过程、掌握基本 的装配技艺、学习整机的装配工艺、培养自身的动手能力以及培养严谨 的学习工作作风。 DT830B由机壳熟料件(包括上下盖和旋钮)、印制板部件(包括插口)、液晶屏及表笔等组成,组装成功关键是装配印制板部件。因为 一旦被划伤或有污迹,将对整机的性能产生很大的影响。整机安装的流 程图如下所示: 3)认识DT830B数字万用表的液晶显示器件、印制板部件等。 4)安装制作一台DT830B数字万用表。 5)根据技术指标测试DT830B数字万用表的主要参数 6)校验数字式万用表,减小其误差。 二、电路原理 DT830B电路原理它是3位半数字万用表。 数字万用表的核心是以ICL7106A/D转化器为核心的数字万用表。A/D转化器将0~2V范围的模拟电压变成三位半的BCD码数字显示出来。将被测直流电压、交流电压、直流电流及电阻的物理量变成0~2V的直流电压,送到ICL7106的输入端,即可在数字表上进行检测。 为检测大于2V的直流电压,在输入端引入衰减器,将信号变为0~2V,检测显示时再放大同样的倍数。 检测直流电流,首先必须将被测电流变成0~2V的直流电压即实现衰减与I/V 变换。衰减是有精密电阻构成的具有不同分流系数的分流器完成。 电阻的检测是利用电流源在电阻上产生压降。因为被测电阻上通过的电流是恒定的,所以在被测电阻上产生的压降与其阻值成正比,然后将得到的电压信号送到A/D转换器进行检测。 三、总原理图及元器件清单 数字电路电子时钟课程设计 整个数字钟由时间计数电路、晶体振荡电路、校正电路、整点报时电路组成。 其中以校正电路代替时间计数电路中的时、分、秒之间的进位,当校时电路处于正常输入信号时,时间计数电路正常计时,但当分校正时,其不会产生向时 进位,而分与时的校位是分开的,而校正电路也是一个独立的电路。电路的信 号输入由晶振电路产生,并输入各电路 方案论证:方案一数字电子钟由信号发生器、“时、分、秒”计数器、译码 器及显示器、校时电路、整点报时电路等组成。秒信号产生器是整个系统的时 基信号,它直接决定计时系统的精度,一般用555构成的振荡器加分频器来实现。 优点:数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械 式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用。 方案二秒、分计数器为60进制计数器,小时计数器为24进制计数器。 实现这两种模数的计数器采用中规模集成计数器74LS90构成。 优点:简单易懂,比较好调试。 1 设计原理数字电子钟由信号发生器、“时、分、秒”计数器、译码器及显示器、校时电路、整点报时电路等组成。秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用555构成的振荡器加分频器来实现。将标 准秒脉冲信号送入“秒计数器”,该计数器采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用60进制计数器,每累计60分,发出一个“时脉冲”信号,该信号将被 送到“时计数器”。“时计数器”采用24进制计数器,可以实现一天24h的累计。译码显示电路将“时、分、秒”计数器的输出状态经七段显示译码器译码,通 过六位LED显示器显示出来。整点报时电路是根据计时系统的输出状态产生一 数电课程设计报告数字钟的设计 数电课程设计报告 第一章设计背景与要求 设计要求 第二章系统概述 2.1设计思想与方案选择 2.2各功能块的组成 2.3工作原理 第三章单元电路设计与分析 3.1各单元电路的选择 3.2设计及工作原理分析 第四章电路的组构与调试 4.1遇到的主要问题 4.2现象记录及原因分析 4.3解决措施及效果 4.4功能的测试方法,步骤,记录的数据 第五章结束语 5.1对设计题目的结论性意见及进一步改进的意向说明5.2总结设计的收获与体会 附图(电路总图及各个模块详图) 参考文献 第一章设计背景与要求 一.设计背景与要求 在公共场所,例如车站、码头,准确的时间显得特别重要,否则很有可能给外出办事即旅行袋来麻烦。数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确度和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用。数字钟是一种典型的数字电路,包括了组合逻辑电路和时序电路。 设计一个简易数字钟,具有整点报时和校时功能。 (1)以四位LED数码管显示时、分,时为二十四进制。 (2)时、分显示数字之间以小数点间隔,小数点以1Hz频率、50%占空比的亮、灭规律表示秒计时。 (3)整点报时采用蜂鸣器实现。每当整点前控制蜂鸣器以低频鸣响4次,响1s、停1s,直到整点前一秒以高频响1s,整点时结束。 (4)才用两个按键分别控制“校时”或“校分”。按下校时键时,是显示值以0~23循环变化;按下“校分”键时,分显示值以0~59循环变化,但时显示值不能变化。 二.设计要求 电子技术是一门实践性很强的课程,加强工程训练,特别是技能的培养,对于培养学生的素质和能力具有十分重要的作用。在电子信息类本科教学中,课程设计是一个重要的实践环节,它包括选 数字电路课程设计 一、概述 任务:通过解决一两个实际问题,巩固和加深在课程教学中所学到的知识和实验技能,基本掌握常用电子电路的一般设计方法,提高电子电路的设计和实验能力,为今后从事生产和科研工作打下一定的基础。为毕业设计和今后从事电子技术方面的工作打下基础。 设计环节:根据题目拟定性能指标,电路的预设计,实验,修改设计。 衡量设计的标准:工作稳定可靠,能达到所要求的性能指标,并留有适当的裕量;电路简单、成本低;功耗低;所采用的元器件的品种少、体积小并且货源充足;便于生产、测试和维修。 二、常用的电子电路的一般设计方法 常用的电子电路的一般设计方法是:选择总体方案,设计单元电路,选择元器件,计算参数,审图,实验(包括修改测试性能),画出总体电路图。 1.总体方案的选择 设计电路的第一步就是选择总体方案。所谓总体方案是根据所提出的任务、要求和性能指标,用具有一定功能的若干单元电路组成一个整体,来实现各项功能,满足设计题目提出的要求和技术指标。 由于符合要求的总体方案往往不止一个,应当针对任务、要求和条件,查阅有关资料,以广开思路,提出若干不同的方案,然后仔细分析每个方案的可行性和优缺点,加以比较,从中取优。在选择过程中,常用框图表示各种方案的基本原理。框图一般不必画得太详细,只要说明基本原理就可以了,但有些关键部分一定要画清楚,必要时尚需画出具体电路来加以分析。 2.单元电路的设计 在确定了总体方案、画出详细框图之后,便可进行单元电路设计。 (1)根据设计要求和已选定的总体方案的原理框图,确定对各单元电路的设计要求,必要时应详细拟定主要单元电路的性能指标,应注意各单元电路的相互配合,要尽量少用或不用电平转换之类的接口电路,以简化电路结构、降低成本。 课程设计任务书 学生姓名:吴培力专业班级:信息SY1201 指导教师:刘可文工作单位:信息工程学院 题目: 数字式电子锁的设计与实现 初始条件: 本设计既可以使用集成电路和必要的元器件等,也可以使用单 片机系统构建数字密码电子锁。自行设计所需工作电源。电路组成 原理框图如图1,数字密码锁的实际锁体一般由电磁线圈、锁栓、 弹簧和锁柜构成。当线圈有电流时,产生磁力,吸动锁栓,即可开 锁。反之则不开锁。 图1 数字式电子锁原理框图要求完成的主要任务:(包括课程设计工作量及技术要求,以及说明书撰写等具体要求) 1、课程设计工作量:1周。 2、技术要求: 1)课程设计中,锁体用LED代替(如“绿灯亮”表示开锁,“红灯亮”表示闭锁)。 2)其密码为4位二进制代码,密码可以通过密码设定电路自行设定。 3)开锁指令为串行输入码,当开锁密码与存储密码一致时,锁被打开。当开锁密码与存储密码不一致时,可重复进行,若连续三次未将锁打开,电路则报警并实现自锁。(报警动作为响1分钟,停10秒) 4)选择电路方案,完成对确定方案电路的设计。计算电路元件参数与元件选择、并画出总体电路原理图,阐述基本原理。安装调试设计电路。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 1、年月日,布置作课设具体实施计划与课程设计报告格式的要求说明。 2、年月日至年月日,方案选择和电路设计。 3、年月日至年月日,电路调试和设计说明书撰写。 4、年月日,上交课程设计成果及报告,同时进行答辩。 指导教师签名:年月日 系主任(或责任教师)签名:年月日 数字电子技术课程设计 数字电子钟 指导老师: 小组成员: 目录 摘要 (3) 第一节系统概述 (4) 第二节单元电路设计与分析 (6) 第三节电路的总体设计与调试 (11) 第四节设计总结 (13) 附录部分芯片功能参数表 (14) 参考文献 (17) 摘要 数字钟是一个将“时”,“分”,“秒”显示于人的视觉器官的计时装置。它的计时周期为24小时,显示满刻度为23时59分59秒。一个基本的数字钟电路主要由秒信号发生器、“时、分、秒、”计数器、译码器及显示器组成。由于采用纯数字硬件设计制作,与传统的机械表相比,它具有走时准,显示直观,无机械传动装置等特点。 本设计中的数字时钟采用数字电路实现对“时”、“分”、“秒”的显示和调整。通过采用各种集成数字芯片搭建电路来实现相应的功能。具体用到了555震荡器,74LS90及与非,异或等门集成芯片等。该电路具有计时的功能。 在对整个模块进行分析和画出总体电路图后,对各模块进行仿真并记录仿真所观察到的结果。 实验证明该设计电路基本上能够符合设计要求! 关键词振荡器、计数器、译码显示器、Multisim 第一节系统概述 数字电子钟是由多块数字集成电路构成的,其中有振荡器,分频器,校时电路,计数器,译码器和显示器六部分组成。振荡器和分频器组成标准秒信号发生器,不同进制的计数器产生计数,译码器和显示器进行显示,通过校时电路实现对时,分的校准。 1.1实验目的 1).掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的设计、安装、测试方法; 2).进一步巩固所学的理论知识,提高运用所学知识分析和解决实际问题的能力; 3).提高电路布局﹑布线及检查和排除故障的能力; 4).培养书写综合实验报告的能力。 1.2 主要内容 熟悉Multisim10.0仿真软件的应用;设计一个具有显示、校时、整点报时和定时功能的数字时钟,.能独立完成整个系统的设计;用Multisim10.0仿真实现数字时钟的功能。 1.3 系统设计思路与总体方案 数字时钟基本原理的逻辑框图如下所示: , 课程设计 课程名称_模拟电子技术课程设计 题目名称音频功率放大电路 $ 学生学院 专业班级 学号 学生姓名__ 指导教师 : 2010 年 6 月 20 日 — 音频功率放大电路课程设计报告 一、设计题目 题目:音频功率放大电路 二、设计任务和要求 ` 1)设计任务 设计并制作一个音频功率放大电路(电路形式不限),负载为扬声器,阻抗8Ω。 2)设计要求 频带宽50H Z ~20kH Z ,输出波形基本不失真;电路输出功率大于8W; 输入灵敏度为100mV,输入阻抗不低于47KΩ。 三、原理电路设计 功率放大电路: % 功率放大电路通常作为多级放大电路的输出级。功率放大器的常见电路形式有OTL电路和OCL电路。在很多电子设备中,要求放大电路的输出级能够带动某种负载,例如驱动仪表,使指针偏转;驱动扬声器,使之发声;或驱动自动控制系统中的执行机构等。也就是把输入的模拟信号经被放大后,去推动一个实际的负载工作,所以要求放大电路有足够大的输出功率,这样的放大电路统称为功率放大电路。而音频功率放大器的作用就是给音响放大器的负载RL(扬声器)提供一定的输出功率。当负载一定时,希望输出的功率尽可能大,输出的信号的非线形失真尽可能地小,效率尽可能的高。随着半导体工艺,技术的不断发展,输出功率几十瓦以上的集成放大器已经得到了广泛的应用。功率VMOS管的出现,也给功率放大器的发展带来了新的生机。总之,功率放大器的主要任务是向负载提供较大的信号功率,故功率放大器应具有以下几个主要特点: 1. 输出功率要足够大 工作在大信号状态下,输出电压和输出电流都很大.要求在允许的失真条件下, 目录 一.设计目的 (1) 二.实现功能 (1) 三.制作过程 (1) 四.原理框图 (3) 4.1 数字钟构成 (3) 4 .2设计脉冲源 (4) 4.3 设计整形电路 (5) 4.4 设计分频器 (5) 4.5 实际计数器 (6) 4.6 译码/驱动器电路的设计 (7) 4.7 校时电路 (8) 4.8 整点报时电路 (9) 4.9 绘制总体电路图 (10) 五.具体实现 (10) 5.1电路的选择 (10) 5.2集成电路的基本功能 (10) 5.3 电路原理 (11) 六.感想与收获 (12) 七.附录 (14) 数字电子技术课程设计报告 一、设计目的 数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。 数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。 钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、定时启闭电路、定时开关烘箱、通断动力设备,甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。因此,研究数字钟及扩大其应用,有着非常现实的意义。 石英数字钟,具有电路简洁,代表性好,实用性强等优点,在数字钟的制作中,我们采用了传统的PCMS大规模集成电路为核心,配上LED发光显示屏,用石英晶体做稳频元件,准确又方便。 二、实现功能 ①时间以12小时为一个周期; ②显示时、分、秒; ③具有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间; ④计时过程具有报时功能,当时间到达整点前10秒进行蜂鸣报时; 数字电路课程设计报告 导语:真正的知识来自内心,而不是得自别人的传授。同时,唯有出自内心的知识,才能使人拥有真正的智慧。以下小编为大家介绍数字电路课程设计报告文章,欢迎大家阅读参考! 数字电路课程设计报告设计题目:数字电子钟逻辑电路专业班级:自动化112班学生姓名: xx 学号:xx指导教师: xx 设计时间: xx 教师评语:成绩评阅教师日期 所谓数字钟,是指利用电子电路构成的计时器。相对机械钟而言,数字钟能实现准确计时,并显示时、分、秒,而且可以方便准确的对时间进行调节。在此基础上,还可以实现整点报时的功能。因此,数字钟的应用十分广泛。我们要通过这次的课程设计掌握数字钟的原理,学会设计简单的数字钟。 用中小规模集成电路设计一台能显示时、分、秒24时制地的数字电子钟,具体要求如下: 时为00-23二十四进制计数器;秒、分为00-59六十进制计数器; 整点报时,整点报时电路要求在每个整点前鸣叫五次低音,整点时再鸣叫一次高音。 数字电子钟所采用的是十六进制计数器74LS161和十进制计数器74SL160,根据时分秒各个部分的的不同功能,设计成不同进制。秒的个位,需要10进制计数器,十位需6进制计数器。秒部分设计与分钟的设计完全相同;时部分的设计为当时钟计数到24时,使计数器的小时部分清零,从而实现整体循环计时的功能。 (1)数字电子技术实验系统箱, (2)直流稳压电源, (3)集成芯片:74LS161 2个、74LS160 4个、 74LS00 2个、 74LS20 1个。 (4)喇叭,1/4W、8Ω。 计数部分:利用74LS161芯片,74LS160芯片和74LS00芯片组成的计数器,它们采用异步连接,利用外接标准1Hz 脉冲信号进行计数。 1. 显示部分:将两片74LS161芯片和四片74LS60的Q0Q1Q2Q3脚分别接到实验箱上的数码显示管上,根据脉冲的个数显示时间。 (一)设计步骤及方法 所有74LS161芯片和74LS160的16脚接5V电源(置为1),3脚、4脚、5脚、6脚和8脚接地。74LS00芯片的14脚接5V电源,7接地。 1. 秒设计 秒的个位部分为逢十进一,十位部分为逢六进一,从而共同完成60进制计数器。当计数到59时清零并重新开始计数。秒的个位部分的设计:利用十进制计数器74LS160和与非门74LS00在面包板上设计10进制计数器显示秒的个位。 数字逻辑课程设计说明书 题目: 多功能数字钟 专业: 计算机科学与技术 班级: 姓名: 学号: 完成日期: -9 一、设计题目与要求 设计题目: 多功能数字钟 设计要求: 1.准确计时, 以数字形式显示时、分、秒的时间。 2.小时的计时能够为”12翻1”或”23翻0”的形式。 3.能够进行时、分、秒时间的校正。 二、设计原理及其框图 1.数字钟的构成 数字钟实际上是一个对标准频率?( 1HZ) 进行计数的计数电路。由于计数的起始时间不可能与标准时间( 如北京时间) 一致, 故需要在电路上加一个校时电路。图 1 所示为数字钟的一般构成框图。 图1 数字电子时钟方案框图 ⑴多谐振荡器电路 多谐振荡器电路给数字钟提供一个频率1Hz 的信号, 可保证数字钟的走时准确及稳定。 ⑵时间计数器电路 时间计数电路由秒个位和秒十位计数器、分个位和分十位计数器及时个位和时十位计数器电路构成。其中秒个位和秒十位计数器、分个位和分十位计数器为60 进制计数器。而根据设计要求, 时个位和时十位计数器为24 进制计数器。 ⑶译码驱动电路 译码驱动电路将计数器输出的8421BCD 码转换为数码管需要的逻辑状态, 而且为保证数码管正常工作提供足够的工作电流。 ⑷数码管 数码管一般有发光二极管( LED) 数码管和液晶( LCD) 数码管。本设计提供的为LED数码管。 2.数字钟的工作原理 ⑴多谐振荡器电路 555 定时器与电阻R1、 R2, 电容C1、 C2 构成一个多谐振荡器, 利用电容的充放电来调节输出V0, 产生矩形脉冲波作为时钟信号, 因为是数字钟, 因此应选择的电阻电容值使频率为1HZ。 ⑵时间计数单元 六片74LS90 芯片构成计数电路, 按时间进制从右到左构成从低位向高位的进位电路, 并经过译码显示。在六位LED 七段显示起 辽宁工业大学电子技术基础课程设计(论文) 题目:语音放大电路 课程设计(论文)任务及评语 1 第 1 章语音放大电路设计方案论证 (1) 1.1 语音放大电路的应用意 义 (1) 1.2 语音放大电路设计的要求及技术指标................................... 1 1.3 设计方案论 证 (1) 1.4 总体设计方案框图及分析............................................. 2 第 2 章语音放大电路各单元电路设计.. (3) 2.1 前置放大电路的设 计 (3) 2.2 滤波电路的设 计 (4) 2.3 功率放大电路的设计.................................................5 第3 章语音放大电路整体电路设计. (7) 3.1 整体电路图及工作原 理 (7) 3.2 电路参数计算及整机电路性能分析.....................................9 第 4 章设计总结...........................................................9 参考文献.. (9) 附录:器件清单 (10) 2 第1 章语音放大电路设计方案论证 1.1语音放大电路的应用意义 在电子电路中,输入信号常常受各种因素的影响。即含有一些不必要的成分(即干扰),或者输入信号是不同频率信号混合在一起的信号,对前者应设法将不必要的成份衰减到足够小,而后者应设法将需要的信号提取出来。这时我们就需要一种技能放大语音信号又能降低外来噪声的仪器。 1.2语音放大电路设计的要求及技术指标 设计要求: 1. 分析设计要求,明确性能指标。必须仔细分析课题要求、性能、指标及应用环境 等,广开思路,构思出各种总体方案,绘制结构框图。 2. 确定合理的总体方案。对各种方案进行比较,以电路的先进性、结构的繁简、成 本的高低及制作的难易等方面作综合比较,并考虑器件的来源,敲定可行方案。 3. 设计各单元电路。总体方案化整为零,分解成若干子系统或单元电路,逐个设计。 4. 组成系统。在一定幅面的图纸上合理布局,通常是按信号的流向,采用左进右出 的规律摆放各电路,并标出必要的说明。 技术指标:采用全部或部分分立元件设计一种语音 放大电路额定输出功率P o≥5W 负载阻抗R L=4Ω频率响 应:300HZ~3KHZ 1.3设计方案论证 语音放大电路主要有信号输入、前置放大电路、有源带通滤波电路、功率放大电路和输出组成。 1.3.1 前置放大电路 前置放大电路以为测量用小信号放大电路。在测量用的放大电路中,一般传感器送 1 数字电路课程设计 姓名:李志波 专业:电子信息工程 年级:2012级 数字闹钟计时器 一.实验目的 1.通过这个实验进一步了解掌握各种功能芯片的功能,并能够在电路系统中正确应用。 2.强化巩固专业课课程内容,学会对电路的系统分析。 3.初步了解基础的电路设计思路和方法,锻炼自己的动手能力,巩固电子焊接技术。 二.实验原理 1.显示译码器 74LS248(74LS48)是BCD码到七段码的显示译码器,它可以直接驱动共阴极数码管。它的引脚图及功能如下: (a)要求输入数字0~15时“灭灯输入端”BI必须开路或保持高电平,如果不要灭十进制的0,则“动态灭灯 输入”RBI必须开路或者为高电平。 (b)当灭灯输入端BI接低电平时,不管其他输入端为何种电平,所有各端输出均为低电平。 (c)BI/RBO是线与关系,既是“灭灯输入端”BI又是“动态灭灯输出端”RBO。 2.数码显示器 LC5011-11就是一种共阴极数码显示器,它的管脚图如图1,X为共阴极,DP为小数点。其内部是八段发光二极管的负极连在一起的电路。当在a.b.c.d.e.f.g.DP加上正向电压时,各段 二极管就会被点亮,例如,利用74LS48和数码管组合成的显 示译码电路。 ABCD 四个引脚接上一级输出 LT,RBO/BI ,RBI 接高电平,或悬空。 3,十进制集成计数电路74LS90 74LS90时异步二-五-十进制计数器。其管脚图如图 U1 74LS90D Q A 12Q B 9Q D 11 Q C 8I N B 1 R 916 R 927R 012I N A 14R 02 3 G N D 10 V C C 5它的内部由两个计数电路组成,一个为二 进制,计数电路,计数脉冲输入端为CP1,输出端为QA QB QC QD.这两个计数器可独立使用,当QA 连到CP2时,可构成十进制计数器。 它具有复零输入端ROA,ROB 和复9输入端R9A R9B 。如果复零输入端ROA,ROB 皆为高电平时,计数器复零;如果复9输入端R9A,R9B 皆为高电平时,计数器复9。计数时ROA,ROB 其中之一接高电平或者二者都接高电平,并要求复9输入端R9A,R9B 其一接低电平或者同时接低电平。用74LS90接成的24 进 制 计 数 器 电 路 如 图数字电路课程设计数字时钟

课程设计:任务四放大电路及其应用习题

数字电路课程设计题目选编

数字电路课程设计报告(好)

数字电路课程设计——数字钟

模电音频功率放大器课程设计

《数字电路课程设计》

数字电子技术基础课程设计DT-830B数字万用表报告

数字电路电子时钟课程设计

数电课程设计报告数字钟的设计

数字电路课程设计

数字电路课程设计报告

数电课程设计 数字电子钟

音频功率放大电路课程设计报告

数字电子技术课程设计报告(数字钟)

数字电路课程设计报告

数电课程设计数字电子时钟样本

语音放大电路课程设计

数字电路课程设计