DES加密算法Verilog实现源代码

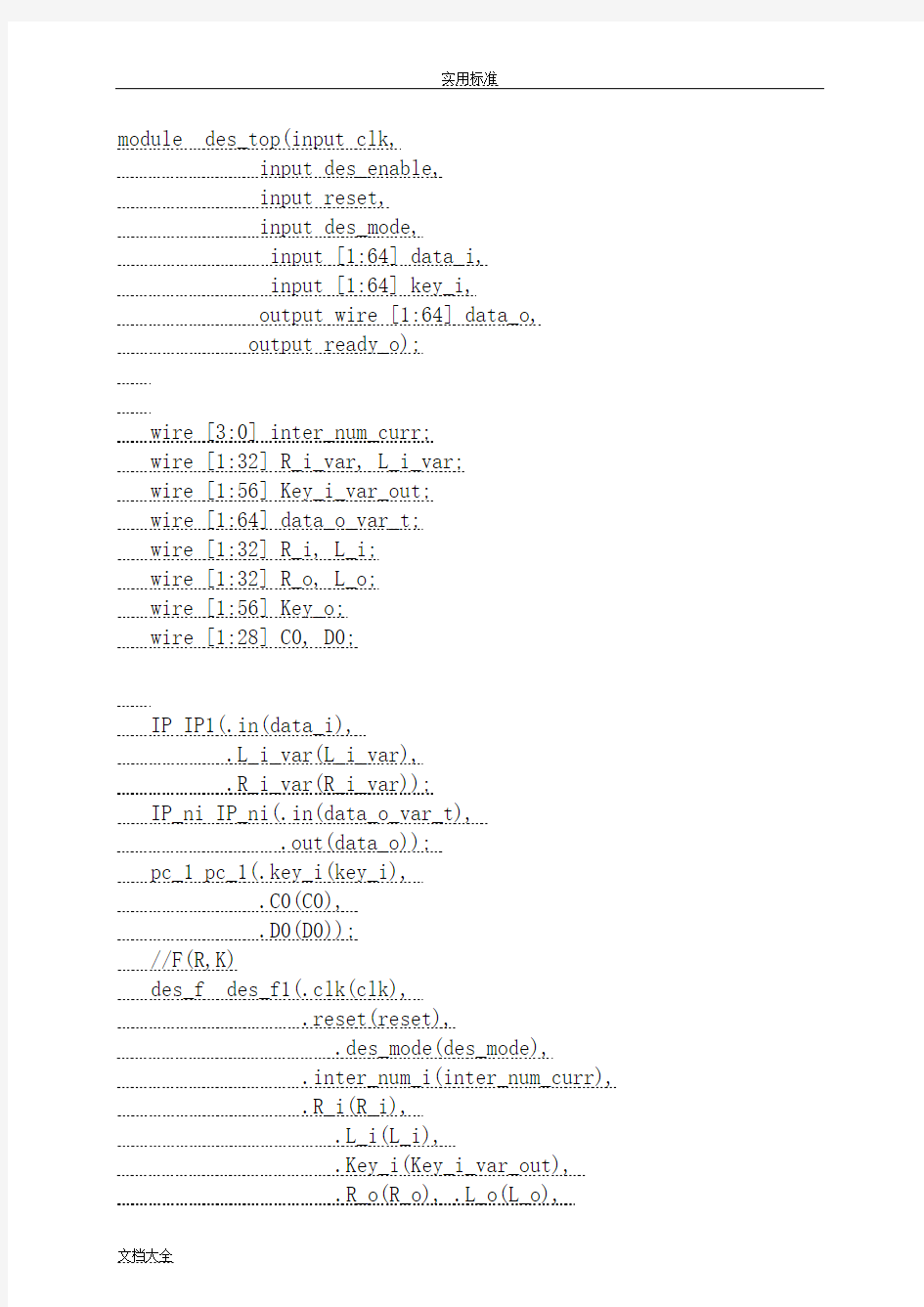

module des_top(input clk,

input des_enable,

input reset,

input des_mode,

input [1:64] data_i,

input [1:64] key_i,

output wire [1:64] data_o,

output ready_o);

wire [3:0] inter_num_curr;

wire [1:32] R_i_var, L_i_var;

wire [1:56] Key_i_var_out;

wire [1:64] data_o_var_t;

wire [1:32] R_i, L_i;

wire [1:32] R_o, L_o;

wire [1:56] Key_o;

wire [1:28] C0, D0;

IP IP1(.in(data_i),

.L_i_var(L_i_var),

.R_i_var(R_i_var));

IP_ni IP_ni(.in(data_o_var_t),

.out(data_o));

pc_1 pc_1(.key_i(key_i),

.C0(C0),

.D0(D0));

//F(R,K)

des_f des_f1(.clk(clk),

.reset(reset),

.des_mode(des_mode), .inter_num_i(inter_num_curr), .R_i(R_i),

.L_i(L_i),

.Key_i(Key_i_var_out),

.R_o(R_o), .L_o(L_o),

.Key_o(Key_o));

//contral 16 F(R,K)

contrl contrl1(.data_o_var_t(data_o_var_t),

.inter_num_curr(inter_num_curr),

.Key_i_var_out(Key_i_var_out),

.R_i(R_i),

.L_i(L_i),

.ready_o(ready_o),

.L_o(L_o),

.R_o(R_o),

.R_i_var(R_i_var),

.L_i_var(L_i_var),

.Key_o(Key_o),

.C0(C0),

.D0(D0),

.clk(clk),

.reset(reset),

.des_enable(des_enable));

endmodule

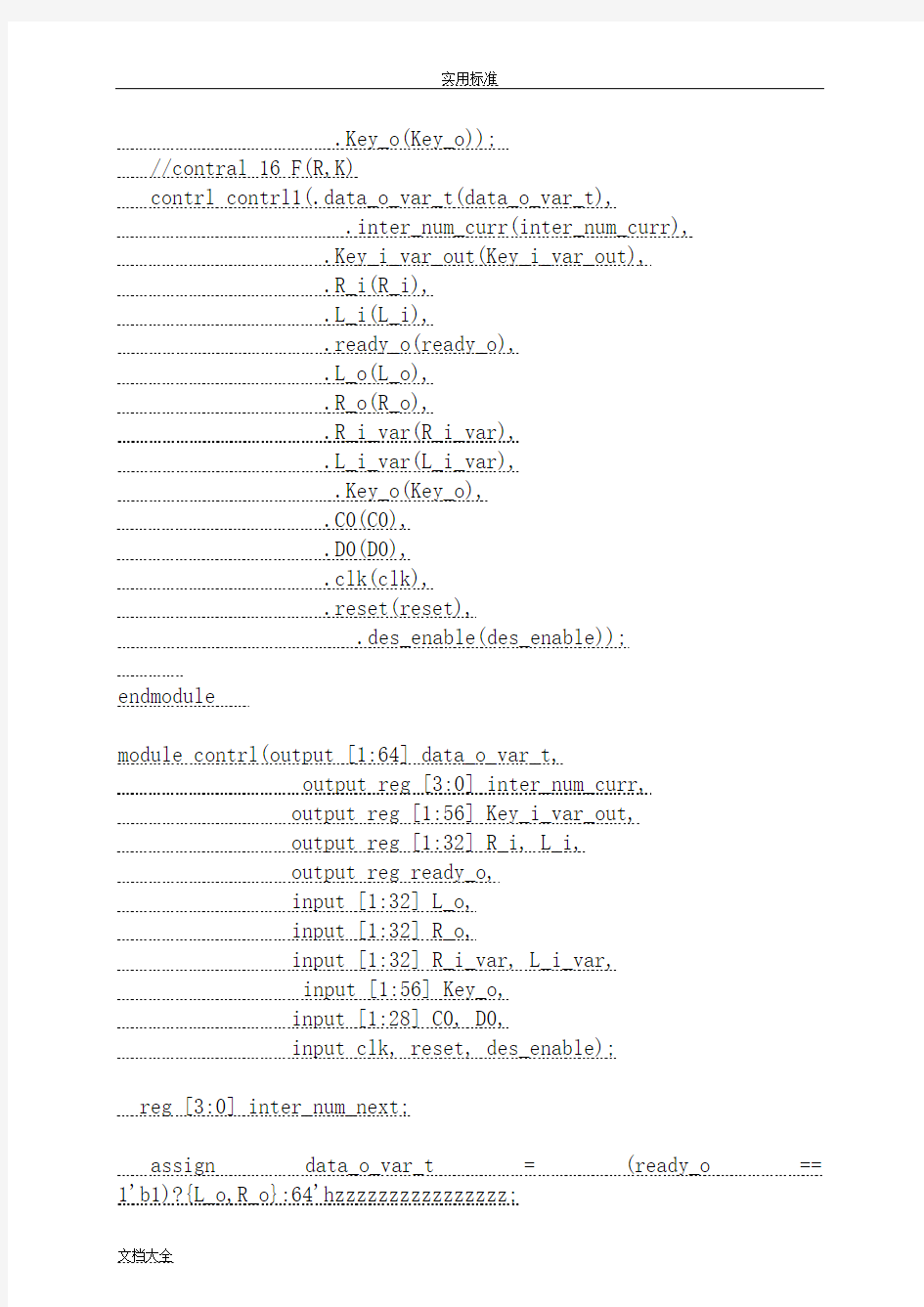

module contrl(output [1:64] data_o_var_t,

output reg [3:0] inter_num_curr,

output reg [1:56] Key_i_var_out,

output reg [1:32] R_i, L_i,

output reg ready_o,

input [1:32] L_o,

input [1:32] R_o,

input [1:32] R_i_var, L_i_var,

input [1:56] Key_o,

input [1:28] C0, D0,

input clk, reset, des_enable);

reg [3:0] inter_num_next;

assign data_o_var_t = (ready_o == 1'b1)?{L_o,R_o}:64'hzzzzzzzzzzzzzzzz;

always (posedge clk or negedge reset)

if(reset == 1'b0)

begin

inter_num_next <= 4'd0;

inter_num_curr <= 4'd0;

ready_o <= 1'b0;

end

else if(des_enable)

begin

if(ready_o == 1'b0)

inter_num_curr <= inter_num_next;

end

always (posedge clk or negedge reset)

begin

if(reset == 1'b0) ready_o <= 1'b0;

else if(inter_num_curr == 4'd15) ready_o <= 1'b1;

else ready_o <= 1'b0;

end

always (*)

begin

case(inter_num_curr)

4'd0:begin

//ready_o = 1'b0;

R_i = R_i_var;

L_i = L_i_var;

Key_i_var_out = {C0, D0};

inter_num_next = 4'd1;

end

4'd1: begin

//ready_o = 1'b0;

R_i = R_o;

L_i = L_o;

Key_i_var_out = Key_o;

inter_num_next = 4'd2;

end

4'd2: begin

//ready_o = 1'b0;

R_i = R_o;

L_i = L_o;

Key_i_var_out = Key_o;

inter_num_next = 4'd3;

end

4'd3: begin

//ready_o = 1'b0;

R_i = R_o;

L_i = L_o;

Key_i_var_out = Key_o;

inter_num_next = 4'd4;

end

4'd4: begin

//ready_o = 1'b0;

R_i = R_o;

L_i = L_o;

Key_i_var_out = Key_o;

inter_num_next = 4'd5;

end

4'd5: begin

//ready_o = 1'b0;

R_i = R_o;

L_i = L_o;

Key_i_var_out = Key_o;

inter_num_next = 4'd6;

end

4'd6: begin

//ready_o = 1'b0;

R_i = R_o;

L_i = L_o;

Key_i_var_out = Key_o;

inter_num_next = 4'd7;

end

4'd7: begin

VerilogHDL经典程序非常适合新手

一、2线-4线译码器 module counter4(q1,q0,ncr,cp); input cp,ncr; output q1,q0; reg q1,q0; always@(posedge cp or negedge ncr) begin if(~ncr){q1,q0}<=2'b00; else{q1,q0}<={q1,q0}+1'b1; end endmodule 二、4选1数据选择器 module selector4_1(i0,i1,i2,i3,a1,a0,y); input i0,i1,i2,i3,a1,a0; output y; reg y; always@(a1or a0) begin case({a1,a0}) 2'b00:y=i0; 2'b01:y=i1; 2'b10:y=i2; 2'b11:y=i3; default:y=0; 一、2线-4线译码器 module counter4(q1,q0,ncr,cp); input cp,ncr; output q1,q0; reg q1,q0; always@(posedge cp or negedge ncr) begin if(~ncr){q1,q0}<=2'b00; else{q1,q0}<={q1,q0}+1'b1; end endmodule 二、4选1数据选择器 module selector4_1(i0,i1,i2,i3,a1,a0,y); input i0,i1,i2,i3,a1,a0; output y; reg y; always@(a1or a0) begin case({a1,a0}) 2'b00:y=i0;

智造工坊verilog代码规范

Verilog 代码规范 陈永/Jon chen 2015.12.16

FPGA项目规范体系 智造工坊FPGA项目的执行需要严格按照完整的规范体系完成,代码规范只是一个组成部分。 智造工坊FPGA项目规范 流程规范工 程 规 范 文 档 规 范 代 码 规 范 实 现 规 范 仿 真 规 范 测 试 规 范 验 收 规 范 维 护 规 范

代码规范声明 本课程所述的Verilog代码规范是根据本公司近20年来数百个FPGA项目经验总结出的规范,旨在提高内部工程师工作效率和工作质量。 不同公司根据自身的业务类型和管理理念,具有不同的代码风格和代码规范。本课程仅阐述本公司的代码规范,供初学者参考学习。本课程如有不合理之处或对课程中的规范有更好的建议,请及时提出,一经确认采纳,定有重谢! 联系方式: 邮箱:Jonchen@https://www.360docs.net/doc/f32268664.html, QQ : 517343565

Verilog 代码规范作用 增加代码可读性,复用性,统一性,维护性 提升编码效率,降低语法出错率和逻辑出错率 提高代码实现效率,优化FPGA 逻辑资源,提高设计可靠性和稳定性 初级规范 中级规范 高级规范 (外在形式,基本规范,风格统一即可) (基本保障,建议统一执行) (经验总结,建议在项目中体会)

初级规范 文件名与模块名定义文件头 注释 模块内部结构 端口定义 参数定义 信号定义对齐方式缩进方式模块例化顶层要求

初级(文件名,模块名) 文件名,模块名 1)文件名和模块名保持一致 2)文件以小写.v为后缀名 3)文件名和模块名由小写字母a-z,数字0-9,下划线组成 4)文件名和模块名长度不超过16个字符 5)文件名和模块名中的几个词组以下划线隔开 6)文件名和模块名要有一定含义,和模块功能保持一致 7) Altera公司的Ipcore以ALT开头,Xilinx芯片的Ipcore以XIL开头(一个项目多家芯片) 8)时钟复位控制模块统一用clk_rst,寄存器模块统一用reg_ctrl 9)单芯片项目FPGA顶层模块名统一用fpga_top 10)多板卡多芯片项目FPGA顶层模块名用xx_fpgan_top命名(xx:板卡名,n:FPGA编号)

DES加密算法的实现

常州工学院 计算机信息工程学院 《数据结构》课程设计报告 题目 DES加密算法的实现 班级 14软一 学号姓名王磊(组长) 学号姓名王凯旋 学号姓名陶伟 2016年01月06日

一,实验名称: DES加密算法的实现 二,实验内容: a)熟悉DES算法的基本原理; b)依据所算则的算法,编程实现该该算法; c)执行程序并分析结果; 三,实验原理 1,概述 DES是一种分组加密算法,他以64位为分组对数据加密。64位一组的明文从算法的一端输入,64位的密文从另一端输出。DES是一个对称算法:加密和解密用的是同一个算法(除密钥编排不同以外)。密钥的长度为56位(密钥通常表示为64位的数,但每个第8位都用作奇偶检验,可以忽略)。密钥可以是任意的56位数,且可以在任意的时候改变。 DES算法的入口参数有3个:Key,Data,Mode。其中Key为8个字节共64位,是DES算法的工作密钥;Data也为8个字节64位,是要被加密或解密的数据:Mode为DES的工作方式,有两种:加密或解密。 DES算法的工作过程:若Mode为加密,则用Key对数据Data进行加密,生成Data的密码形式(64位)作为DES的输出结果;若Mode 为解密,则用Key对密码形式的数据Data解密,还原为Data的明码形式(64位)作为DES的输出结果。

2,DES算法详述 DES算法把64位的明文输入块变为64位的密文输出块,他所使用的密钥也是64位,DES对64 位的明文分组进行操作。通过一个初始置换,将明文分组分成左半部分和右半部分,各32位长。然后进行16轮相同的运算,这些相同的运算被称为函数f,在运算过程中数据和密钥相结合。经过16轮运算后左、右部分在一起经过一个置换(初始置换的逆置换),这样算法就完成了。 (1)初始置换 其功能是把输入的64位数据块按位重新组合,并把输出分为L0,R0两部分,每部分各长32位, 即将输入的第58位换到第1位,第50位换到第2位,…,依次类推,最后一位是原来的第7位,L0,R0则是换位输出后的两部分,L0是输出的左32位,R0是右32位。。 (2)逆置换 经过16次迭代运算后,得到L16,R16,将此作为输入进行逆置换,即得到密文输出。逆置换正好是初始置换的逆运算。例如,第1位经过初始置换后,处于第40位,而通过逆置换,又将第40位换回到第1位。 (3)函数f(Ri,Ki)的计算 “扩展置换”是将32位放大成48位,“P盒置换”是32位到32位换位, 在(Ri,Ki)算法描述图中,选择函数功能是把6 b数据变为4 b数

Verilog编码风格

Verilog编码风格 嵌入式开发2010-05-03 15:28:13 阅读14 评论0 字号:大中小订阅 这是以前公司的对fpga代码编写的要求 良好代码编写风格的通则概括如下: (1)对所有的信号名、变量名和端口名都用小写,这样做是为了和业界的习惯保持一致;对常量名和用户定义的类型用大写; (2)使用有意义的信号名、端口名、函数名和参数名; (3)信号名长度不要太长; (4)对于时钟信号使用clk 作为信号名,如果设计中存在多个时钟,使用clk 作为时钟信号的前缀; (5)对来自同一驱动源的信号在不同的子模块中采用相同的名字,这要求在芯片总体设计时就定义好顶层子模块间连线的名字,端口和连接端口的信号尽可能采用相同的名字; (6)对于低电平有效的信号,应该以一个下划线跟一个小写字母b 或n 表示。注意在同一个设计中要使用同一个小写字母表示低电平有效; (7)对于复位信号使用rst 作为信号名,如果复位信号是低电平有效,建议使用rst_n; (8)当描述多比特总线时,使用一致的定义顺序,对于verilog 建议采用bus_signal[x:0]的表示; (9)尽量遵循业界已经习惯的一些约定。如*_r 表示寄存器输出,*_a 表示异步信号,*_pn 表示多周期路径第n 个周期使用的信号,*_nxt 表示锁存前的信号,*_z 表示三态信号等; (10)在源文件、批处理文件的开始应该包含一个文件头、文件头一般包含的内容如下例所示:文件名,作者,模块的实现功能概述和关键特性描述,文件创建和修改的记录,包括修改时间,修改的内容等; (11)使用适当的注释来解释所有的always 进程、函数、端口定义、信号含义、变量含义或信号组、变量组的意义等。注释应该放在它所注释的代码附近,要求简明扼要,只要足够说明设计意图即可,避免过于复杂; (12)每一行语句独立成行。尽管VHDL 和Verilog 都允许一行可以写多个语句,当时每个语句独立成行可以增加可读性和可维护性。同时保持每行小于或等于72 个字符,这样做都是为了提高代码得可读性; (13)建议采用缩进提高续行和嵌套语句得可读性。缩进一般采用两个空格,如西安交通大学SOC 设计中心 2 如果空格太多则在深层嵌套时限制行长。同时缩进避免使用TAB 键,这样可以避免不同机器TAB 键得设置不同限制代码得可移植能力; (14)在RTL 源码的设计中任何元素包括端口、信号、变量、函数、任务、模块等的命名都不能取Verilog 和VHDL 语言的关键字; (15)在进行模块的端口申明时,每行只申明一个端口,并建议采用以下顺序:

(免费)[VHDL+Verilog]良好的代码编写风格(二十五条)

[VHDL+Verilog]良好的代码编写风格(二十五条) 良好代码编写风格可以满足信、达、雅的要求。在满足功能和性能目标的前提下,增强代码的可读性、可移植性,首要的工作是在项目开发之前为整个设计团队建立一个命名约定和缩略语清单,以文档的形式记录下来,并要求每位设计人员在代码编写过程中都要严格遵守。良好代码编写风格的通则概括如下: (1)对所有的信号名、变量名和端口名都用小写,这样做是为了和业界的习惯保持一致;对常量名和用户定义的类型用大写; (2)使用有意义的信号名、端口名、函数名和参数名; (3)信号名长度不要太长; (4)对于时钟信号使用clk 作为信号名,如果设计中存在多个时钟,使用clk 作为时钟信号的前缀; (5)对来自同一驱动源的信号在不同的子模块中采用相同的名字,这要求在芯片总体设计时就定义好顶层子模块间连线的名字,端口和连接端口的信号尽可能采用相同的名字; (6)对于低电平有效的信号,应该以一个下划线跟一个小写字母b 或n 表示。注意在同一个设计中要使用同一个小写字母表示低电平有效; (7)对于复位信号使用rst 作为信号名,如果复位信号是低电平有效,建议使用rst_n; (8)当描述多比特总线时,使用一致的定义顺序,对于verilog 建议采用bus_signal[x:0]的表示; (9)尽量遵循业界已经习惯的一些约定。如*_r 表示寄存器输出,*_a 表示异步信号,*_pn 表示多周期路径第n 个周期使用的信号,*_nxt 表示锁存前的信号,*_z 表示三态信号等; (10)在源文件、批处理文件的开始应该包含一个文件头、文件头一般包含的内容如下例所示:文件名,作者,模块的实现功能概述和关键特性描述,文件创建和修改的记录,包括修改时间,修改的内容等; (11)使用适当的注释来解释所有的always 进程、函数、端口定义、信号含义、变量含义或信号组、变量组的意义等。注释应该放在它所注释的代码附近,要求简明扼要,只要足够说明设计意图即可,避免过于复杂; (12)每一行语句独立成行。尽管VHDL 和V erilog 都允许一行可以写多个语句,当时每个语句独立成行可以增加可读性和可维护性。同时保持每行小于或等于72 个字符,这样做都是为了提高代码得可读性;

DES加密算法的JAVA实现

目录 摘要 (3) 一、目的与意义 (4) 二、DES概述 (5) 三、DES加解密算法原理 (7) 1.加密 (6) 2.子密钥生成 (11) 3.解密 (13) 四、加解密算法的实现 (14) 1.软件版本 (14) 2.平台 (14) 3.源代码 (14) 4.运行结果 (24) 五、总结 (25)

【摘要】1973年5月15 日,美国国家标准局(现在的美国国家标准就是研究所,即NIST)在联邦记录中公开征集密码体制,这一举措最终导致了数据加密标准(DES)的出现,它曾经成为世界上最广泛使用的密码体制。DES由IBM开发,它是早期被称为Lucifer体制的改进。DES在1975年3月17日首次在联邦记录中公布,在经过大量的公开讨论后,1977年2月15日DES被采纳为“非密级”应用的一个标准。最初预期DES作为标准只能使用10~15年;然而,事实证明DES要长寿得多。被采纳后,大约每隔5年就被评审一次。DES的最后一次评审是在1999年1月。 本文阐述了DES发展现状及对网络安全的重要意义,并在此基础上对DES算法原理进行详细的介绍和分析。通过应用DES算法加解密的具体实现,进一步加深对DES算法的理解,论证了DES算法具有加密快速且强壮的优点,适合对含有大量信息的文件进行加密,同时分析了DES算法密钥过短(56位)所带来的安全隐患。 【关键词】DES 加密解密明文密文

一、目的与意义 随着计算机和通信网络的广泛应用,信息的安全性已经受到人们的普遍重视。信息安全已不仅仅局限于政治,军事以及外交领域,而且现在也与人们的日常生活息息相关。现在,密码学理论和技术已得到了迅速的发展,它是信息科学和技术中的一个重要研究领域。在近代密码学上值得一提的大事有两件:一是1977年美国国家标准局正式公布实施了美国的数据加密标准(DES),公开它的加密算法,并批准用于非机密单位及商业上的保密通信。密码学的神秘面纱从此被揭开。二是Diffie和Hellman联合写的一篇文章“密码学的新方向”,提出了适应网络上保密通信的公钥密码思想,拉开了公钥密码研究的序幕。 DES(Data Encryption Standard)是IBM公司于上世纪1977年提出的一种数据加密算法。在过去近三十年的应用中,还无法将这种加密算法完全、彻底地破解掉。而且这种算法的加解密过程非常快,至今仍被广泛应用,被公认为安全的。虽然近年来由于硬件技术的飞速发展,破解DES已经不是一件难事,但学者们似乎不甘心让这样一个优秀的加密算法从此废弃不用,于是在DES的基础上有开发了双重DES(DoubleDES,DDES)和三重DES(Triple DES,TDES)。 在国内,随着三金工程尤其是金卡工程的启动,DES 算法在POS、ATM、磁卡及智能卡(IC 卡)、加油站、高速公路收费站等领域被广泛应用,以此来实现关键数据的保密,如信用卡持卡人的PIN 码加密传输,IC 卡与POS 间的双向认证、金融交易数据包的MAC 校验等,均用到DES 算法。DES加密体制是ISO颁布的数据加密标准。 因此研究DES还是有非常重要的意义。

74LS138Verilog源码

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 2020/02/28 13:40:03 // Design Name: // Module Name: _74ls138 // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module _74ls138(nE1,nE2,E3,B,nY); input nE1,nE2,E3; input [2:0]B; output[7:0]nY; reg[7:0]nY; always@(nE1,nE2,E3,B) if(!nE1 && !nE2 && E3) begin case(B) 3'b000: nY = 8'b1111_1110; 3'b001: nY = 8'b1111_1101; 3'b010: nY = 8'b1111_1011; 3'b011: nY = 8'b1111_0111; 3'b100: nY = 8'b1110_1111; 3'b101: nY = 8'b1101_1111; 3'b110: nY = 8'b1011_1111; 3'b111: nY = 8'b0111_1111; default:nY = 8'b1111_1111; endcase end

Verilog试题 A答案

北京航空航天大学 2011 ~2012 学年第二学期 数字EDA 期末考试试卷 ( 2012 年 5 月 23 日) 班级:__________;学号:______________;姓名:__________________;成绩:___________ 注意事项:1、填空题与选择题直接在试题上作答 2、设计题在答题纸上作答 正题: 一、填空题(共30分,每道题3分) 1. 写出表达式以实现对应电路的逻辑功能。 F 2. 根据图中输入输出关系将Verilog 模块定义补充完整,其中信号A 为5比特宽度,其余信号为1比特宽度。 A 宽 3. IEEE 标准的硬件描述语言是 verilog HDL 和 VHDL 。 4. 你所知道的可编程逻辑器件有(至少两种): FPGA, CPLD, GAL, PAL (任写其二) 。 5. 假定某4比特位宽的变量a 的值为4’b1011,计算下列运算表达式的结果 6. Verilog 语言规定了逻辑电路中信号的4种状态,分别是0,1,X 和Z 。其中0表示低电平状态,1表示高电平状态,X 表示 不定态(或未知状态) ,Z 表示 高阻态 。 assign F= E ^ ( (A&B) | (!(C&D))) module tblock( A,B,C ) ; output [4:0] A; input B; inout C; …… //省略了功能描述 endmodule //模块结束 &a = 1’b0 ~a = 4’b0100 {3{a}} = 12’b101110111011 {a[2:0],a[3]} = 4’b0111 (a<4’d3) || (a>=a) = 1’b1 !a = 1’b0

DES加密算法设计(含程序)

DES加密算法分析 [摘要]DES数据加密算法是使用最广的分组加密算法,它作为最著名的保密密钥或对称密钥加密算法,在计算机密码学及计算机数据通信的发展过程中起了重要作用。本次学年论文是主要是学习介绍DES对 称密钥数据加密算法,并用c++实现。DES算法具有较高的安全性,为我们进行一般的计算机数据传输活 动提供了安全保障。 [关键词] 加密与解密,DES算法,S-盒 引言 密码学是伴随着战争发展起来的一门科学,其历史可以追溯到古代,并且还有过辉煌的经历。但成为一门学科则是近20年来受计算机科学蓬勃发展的刺激结果。今天在计算机被广泛应用的信息时代,信息本身就是时间,就是财富。如何保护信息的安全(即密码学的应用)已不再局限于军事、政治和外交,而是扩大到商务、金融和社会的各个领域。特别是在网络化的今天,大量敏感信息(如考试成绩、个人简历、体检结果、实验数据等)常常要通过互联网进行交换。(现代电子商务也是以互联网为基础的。)由于互联网的开放性,任何人都可以自由地接入互联网,使得有些不诚实者就有可能采用各种非法手段进行破坏。因此人们十分关心在网络上交换信息的安全性。普遍认为密码学方法是解决信息安全保护的一个最有效和可行的方法。有效是指密码能做到使信息不被非法窃取,不被篡改或破坏,可行是说它需要付出的代价是可以接受的。 密码是形成一门新的学科是在20世纪70年代。它的理论基础之一应该首推1949年Shannon的一篇文章“保密系统的通信理论”,该文章用信息论的观点对信息保密问题作了全面的阐述。这篇文章过了30年后才显示出它的价值。1976年,Diffie和Hellman发表了论文《密码学的新方向》,提出了公钥密码体制的新思想,这一思想引发了科技界对研究密码学的极大兴趣,大量密码学论文开始公开发表,改变了过去只是少数人关起门来研究密码学的状况。同时为了适应计算机通信和电子商务迅速发展的需要,密码学的研究领域逐渐从消息加密扩大到数字签名、消息认证、身份识别、抗欺骗协议等新课题[1]。 美国国家标准局(NBS)1973年开始研究除国防部外的其它部门的计算机系统的数据加密标准,并批准用于非机密单位及商业上的保密通信。于1973年5月15日和1974年8月27日先后两次向公众发出了征求加密算法的公告。1977年1月,美国政府颁布:采用IBM公司1971年设计出的一个加密算法作为非机密数据的正式数据加密标准(DES : Data Encryption Standard)。DES广泛应用于商用数据加密,算法完全公开,这在密码学史上是一个创举[2]。 在密码学的发展过程中,DES算法起了非常重要的作用。本次学年论文介绍的就是分组加密技术中最典型的加密算法——DES算法。 1概述 1.1加密与解密 加密技术是基于密码学原理来实现计算机、网络乃至一切信息系统安全的理论与技术基础。简单的说,加密的基本意思是改变信息的排列形式,使得只有合法的接受才能读懂,任何他人即使截取了该加密信息也无法使用现有的手段来解读。解密是我们将密文转换成能够直接阅读的文字(即明文)的过程称为解密,它是加密的反向处理,但解密者必须利用相同类型的加密设备和密钥对密

全数字锁相环的verilog源代码讲解

支持论坛发展帖出全数字锁相环的verilog源代码,仿真已通过 module dpll(reset,clk,signal_in,signal_out,syn; parameter para_K=4; parameter para_N=16; input reset; input clk; input signal_in; output signal_out; output syn; reg signal_out; reg dpout; reg delclk; reg addclk; reg add_del_clkout; reg [7:0]up_down_cnt; reg [2:0]cnt8; reg [8:0]cnt_N; reg syn; reg dpout_delay; reg [8:0]cnt_dpout_high; reg [8:0]cnt_dpout_low; /******phase detector*****/ always@(signal_in or signal_out begin dpout<=signal_in^signal_out; end /******synchronization establish detector*****/ always@(posedge clk or negedge reset begin if(!reset dpout_delay<='b0; else dpout_delay<=dpout; end always@(posedge clk or negedge reset begin if(!reset begin cnt_dpout_high<='b0; cnt_dpout_low<='b0; end else if(dpout if(dpout_delay==0 cnt_dpout_high<='b0; else if(cnt_dpout_high==8'b11111111 cnt_dpout_high<='b0; else cnt_dpout_high<=cnt_dpout_high+1; else if(!dpout if(dpout_delay==1 cnt_dpout_low<='b0; else if(cnt_dpout_low==8'b11111111 cnt_dpout_low<='b0; else cnt_dpout_low<=cnt_dpout_low+1; end always@(posedge clk or negedge reset begin if(!reset syn<='b0; else if((dpout&&!dpout_delay||(!dpout&&dpout_delay if(cnt_dpout_high[8:0]-cnt_dpout_low[8:0]<=4||cnt_dpout_low[8:0]- cnt_dpout_high[8:0]<=4 syn<='b1; else syn<='b0; end /****up down couter with mod=K****/ always@(posedge clk or negedge reset begin if(!reset begin delclk<='b0; addclk<='b0; up_down_cnt<='b00000000; end else begin if(!dpout begin delclk<='b0; if(up_down_cnt==para_K-1 begin up_down_cnt<='b00000000; addclk<='b0; end else begin up_down_cnt<=up_down_cnt+1; addclk<='b0; end end else begin addclk<='b0; if(up_down_cnt=='b0 begin up_down_cnt<=para_K-1; delclk<='b0; end else if(up_down_cnt==1 begin delclk<='b1; up_down_cnt<=up_down_cnt-1; end else up_down_cnt<=up_down_cnt-1; end end end /******add and delete clk*****/ always@(posedge clk or negedge reset begin if(!reset begin cnt8<='b000; end else begin if(cnt8=='b111 begin cnt8<='b000; end else if(addclk&&!syn begin cnt8<=cnt8+2; end else if(delclk&&!syn

des加密算法的实现及应用

DES加密算法的实现及应用 学生姓名:梁帅指导老师:熊兵 摘要随着信息与通信技术的迅猛发展和广泛应用,人们通过互联网进行信息交流,难免涉及到密码保护问题,这就需要使用DES加密技术来对数据进行加密保护。本课程设计介绍了DES加密的基本原理以及简单的实现方法。本课程设计基于C语言,采用DES算法技术,设计了DES加密程序,实现了DES加密解密功能。经测试,程序能正常运行,实现了设计目标。 关键词DES加密,C语言,信息交流

1 引言 1.1本文主要内容 DES是一个分组密码算法,使用64位密钥(除去8位奇偶校验,实际密钥长度为56位)对64比特的数据分组(二进制数据)加密,产生64位密文数据。DES是一个对称密码体制,加密和解密使用同意密钥,解密和加密使用同一算法(这样,在硬件与软件设计时有利于加密单元的重用)。DES的所有的保密性均依赖于密钥。 DES算法的入口参数有三个:Key、Data、Mode。其中Key为8个字节共64位,是DES算法的工作密钥;Data也为8个字节64位,是要被加密或被解密的数据;Mode为DES的工作方式,有两种:加密或解密。 DES算法是这样工作的:如Mode为加密,则用Key 去把数据Data进行加密,生成Data的密码形式(64位)作为DES的输出结果;如Mode为解密,则用Key去把密码形式的数据Data解密,还原为Data的明码形式(64位)作为DES的输出结果。在通信网络的两端,双方约定一致的Key,在通信的源点用Key对核心数据进行DES加密,然后以密码形式在公共通信网(如电话网)中传输到通信网络的终点,数据到达目的地后,用同样的Key对密码数据进行解密,便再现了明码形式的核心数据。这样,便保证了核心数据(如PIN、MAC等)在公共通信网中传输的安全性和可靠性 DES的加密过程: 第一阶段:初始置换IP。在第一轮迭代之前,需要加密的64位明文首先通过初始置换IP 的作用,对输入分组实施置换。最后,按照置换顺序,DES将64位的置换结果分为左右两部分,第1位到第32位记为L0,第33位到第64位记为R0。 第二阶段:16次迭代变换。DES采用了典型的Feistel结构,是一个乘积结构的迭代密码算法。其算法的核心是算法所规定的16次迭代变换。DES算法的16才迭代变换具有相同的结构,每一次迭代变换都以前一次迭代变换的结果和用户密钥扩展得到的子密钥Ki作为输入;每一次迭代变换只变换了一半数据,它们将输入数据的右半部分经过函数f后将其输出,与输入数据的左半部分进行

verilog有限状态机实验报告(附源代码)

有限状态机实验报告 一、实验目的 ●进一步学习时序逻辑电路 ●了解有限状态机的工作原理 ●学会使用“三段式”有限状态机设计电路 ●掌握按键去抖动、信号取边沿等处理技巧 二、实验内容 用三段式有限状态机实现序列检测功能电路 a)按从高位到低位逐位串行输入一个序列,输入用拨动开关实现。 b)每当检测到序列“1101”(不重叠)时,LED指示灯亮,否则灭,例如 i.输入:1 1 0 1 1 0 1 1 0 1 ii.输出:0 0 0 1 0 0 0 0 0 1 c)用八段数码管显示最后输入的四个数,每输入一个数,数码管变化一次 d)按键按下的瞬间将拨动开关状态锁存 i.注意防抖动(按键按下瞬间可能会有多次的电平跳变) 三、实验结果 1.Rst_n为0时数码管显示0000,led灯不亮,rst_n拨为1,可以开始输入,将输 入的开关拨到1,按下按钮,数码管示数变为0001,之后一次类推分别输入1, 0,1,按下按钮后,数码管为1101,LED灯亮,再输入1,LED灯灭,之后再输 入0,1(即共输入1101101使1101重叠,第二次LED灯不亮),之后单独输入

1101,LED灯亮 2.仿真图像 刚启动时使用rst_n 一段时间后 其中Y代表输出,即控制led灯的信号,sel表示数码管的选择信号,seg表示数码管信号 四、实验分析 1、实验基本结构

其中状态机部分使用三段式结构: 2、整体结构为:

建立一下模块: Anti_dither.v 输入按键信号和时钟信号,输出去除抖动的按键信号生成的脉冲信号op 这一模块实现思路是利用按钮按下时会持续10ms以上而上下抖动时接触时间不超过10ms来给向下接触的时间计时,达到上限时间才产生输出。 Num.v 输入op和序列输入信号A,时钟信号clk和复位信号,复位信号将num置零,否则若收到脉冲信号则将num左移一位并将输入存进最后一位。输出的num即为即将在数码管上显示的值 Scan.v 输入时钟信号,对其降频以产生1ms一次的扫描信号。 Trigger.v 这一模块即为状态机模块,按三段式书写。 整个模块的输入为时钟信号,脉冲信号,序列输入变量,复位信号,输出LED灯控制信号Y。 第一段是状态转换模块,为时序逻辑电路,功能是描述次态寄存器迁移到现态寄存器。即如果收到复位信号将现态置零,否则将上次得到的next_state赋给current_state。

Verilog的135个经典设计实例

【例3.1】4位全加器 module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule 【例3.2】4位计数器 module count4(out,reset,clk); output[3:0] out; input reset,clk; reg[3:0] out; always @(posedge clk) begin if (reset) out<=0; //同步复位 else out<=out+1; //计数 end endmodule 【例3.3】4位全加器的仿真程序 `timescale 1ns/1ns `include "adder4.v" module adder_tp; //测试模块的名字 reg[3:0] a,b; //测试输入信号定义为reg型 reg cin; wire[3:0] sum; //测试输出信号定义为wire型 wire cout; integer i,j; adder4 adder(sum,cout,a,b,cin); //调用测试对象 always #5 cin=~cin; //设定cin的取值 initial begin a=0;b=0;cin=0; for(i=1;i<16;i=i+1) #10 a=i; //设定a的取值 end - 1 -

initial begin for(j=1;j<16;j=j+1) #10 b=j; //设定b的取值 end initial//定义结果显示格式 begin $monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum); #160 $finish; end endmodule 【例3.4】4位计数器的仿真程序 `timescale 1ns/1ns `include "count4.v" module coun4_tp; reg clk,reset; //测试输入信号定义为reg型 wire[3:0] out; //测试输出信号定义为wire型 parameter DELY=100; count4 mycount(out,reset,clk); //调用测试对象 always #(DELY/2) clk = ~clk; //产生时钟波形 initial begin//激励信号定义 clk =0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*20) $finish; end //定义结果显示格式 initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out); endmodule 【例3.5】“与-或-非”门电路 module AOI(A,B,C,D,F); //模块名为AOI(端口列表A,B,C,D,F) input A,B,C,D; //模块的输入端口为A,B,C,D output F; //模块的输出端口为F - 2 -

第10章例题verilog源代码(夏宇闻版)

第十章例题 module add_4( X, Y, sum, C); input [3 : 0] X, Y; output [3: 0] sum; output C; assign {C, Sum } = X + Y; endmodule //而16位加法器只需要扩大位数即可,见下例: module add_16( X, Y, sum, C); input [15 : 0] X, Y; output [15 : 0] sum; output C; assign {C, Sum } = X + Y; endmodule 快速乘法器常采用网格形式的迭带阵列结构,图10.3示出两个四位二进制数相乘的结构图,//用Verilog HDL来描述乘法器是相当容易的,只需要把运算表达式写出就可以了,见下例。module mult_4( X, Y, Product); input [3 : 0] X, Y; output [7 : 0] Product; assign Product = X * Y; endmodule // 而8位乘法器只需要扩大位数即可,见下例: module mult_8( X, Y, Product); input [7 : 0] X, Y; output [15 : 0] Product; assign Product = X * Y; endmodule

// 下面就是一个位数可以由用户定义的比较电路模块: module compare_n ( X, Y, XGY, XSY, XEY); input [width-1:0] X, Y; output XGY, XSY, XEY; reg XGY, XSY, XEY; parameter width = 8; always @ ( X or Y ) // 每当X 或Y 变化时 begin if ( X = = Y ) XEY = 1; // 设置X 等于Y的信号为1 else XEY = 0; if (X > Y) XGY = 1; // 设置X 大于Y的信号为1 else XGY = 0; if (X < Y) XSY = 1; // 设置X 小于Y的信号为1 else XSY = 0; end endmodule //下面就是带使能控制信号(nCS)的数据位宽可以由用户定义的(8位)八路数据通道选择器模块: module Mux_8( addr,in1, in2, in3, in4, in5, in6, in7, in8, Mout, nCS); input [2:0] addr; input [width-1:0] in1, in2, in3, in4, in5, in6, in7, in8; input nCS; output [width-1:0] Mout; parameter width = 8; always @ (addr or in1 or in2 or in3 or in4 or in5 or in6 or in7 or in8 or nCS) begin if (!nCS) //nCS 低电平使多路选择器工作 case(addr) 3’b000: Mout = in1; 3’b001: Mout = in2; 3’b010: Mout = in3; 3’b011: Mout = in4;

基于FPGA的SDRAM实验Verilog源代码

// megafunction wizard: %ALTPLL% // GENERATION: STANDARD // VERSION: WM1.0 // MODULE: altpll // ============================================================ // File Name: clk_ctrl.v // Megafunction Name(s): // altpll // // Simulation Library Files(s): // altera_mf // ============================================================ // ************************************************************ // THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE! // // 11.0 Build 208 07/03/2011 SP 1 SJ Full Version // ************************************************************ //Copyright (C) 1991-2011 Altera Corporation //Your use of Altera Corporation's design tools, logic functions //and other software and tools, and its AMPP partner logic //functions, and any output files from any of the foregoing //(including device programming or simulation files), and any //associated documentation or information are expressly subject //to the terms and conditions of the Altera Program License //Subscription Agreement, Altera MegaCore Function License //Agreement, or other applicable license agreement, including, //without limitation, that your use is for the sole purpose of //programming logic devices manufactured by Altera and sold by //Altera or its authorized distributors. Please refer to the //applicable agreement for further details. // synopsystranslate_off `timescale 1 ps / 1 ps // synopsystranslate_on moduleclk_ctrl ( areset, inclk0, c0, c1, c2,

ADDA等一些芯片的verilog程序

/* AD0809 module v1.0 work up to 5M sample = 25us 40khz for normal clk = 2.5M sample = 30us 33khz */ module ad0809( clkin, adclk, eoc, st, ale, datain, oe, dataout ); input clkin; input eoc; input [7:0]datain; output st; output ale; output oe; output adclk; output [7:0]dataout; reg adclk; reg [7:0]dataout; reg st; reg oe; reg ale; //frequence divider for AD parameter Div_adclk = 8'd9;//(9+1)*2=20 adclk=2.5M parameter Div_clk_state = 4'd4;//(4+1)*2=10 clk_state=5M

reg [8:0]div_cnt_ad;//frequence div cnt reg [3:0]div_cnt_state; reg clk_state; always@(negedge clkin)begin if(div_cnt_ad != Div_adclk) div_cnt_ad <= div_cnt_ad + 1'b1; else begin div_cnt_ad <= 0; adclk <= ~adclk; end if(div_cnt_state != Div_clk_state) div_cnt_state <= div_cnt_state + 1'b1; else begin div_cnt_state <= 0; clk_state <= ~clk_state; end end /*AD convert*/ reg [3:0]state; reg [7:0]delay; initial begin state <= 4'd0; end always@(negedge clk_state)begin case(state) 4'd0:begin //clear all st <= 1'b0; oe <= 1'b0; ale <= 1'b0;