关于(单片机)msp430的时钟资料全

msp430f5419/38学习笔记之时钟系统

(2011-11-30 10:41:30)

分类: msp430

标签:

msp430f541x

msp430f543x

ucs

时钟系统注:msp5419/38中,如果你使用SMCLK做TIMER_A的时钟,那么进入低功耗3或低功耗4是不会把SMCLK关掉的,这点5系列和其他系列的不一样。

UCS模块是一个低成本超低功耗系统,通过选择使用3个部时钟信号,用户可以得到性能和功耗的

最佳平衡点。UCS可以由软件配置其工作模式,如配置成:不需要任何外部器件、使用 1或 2个外部晶振等。

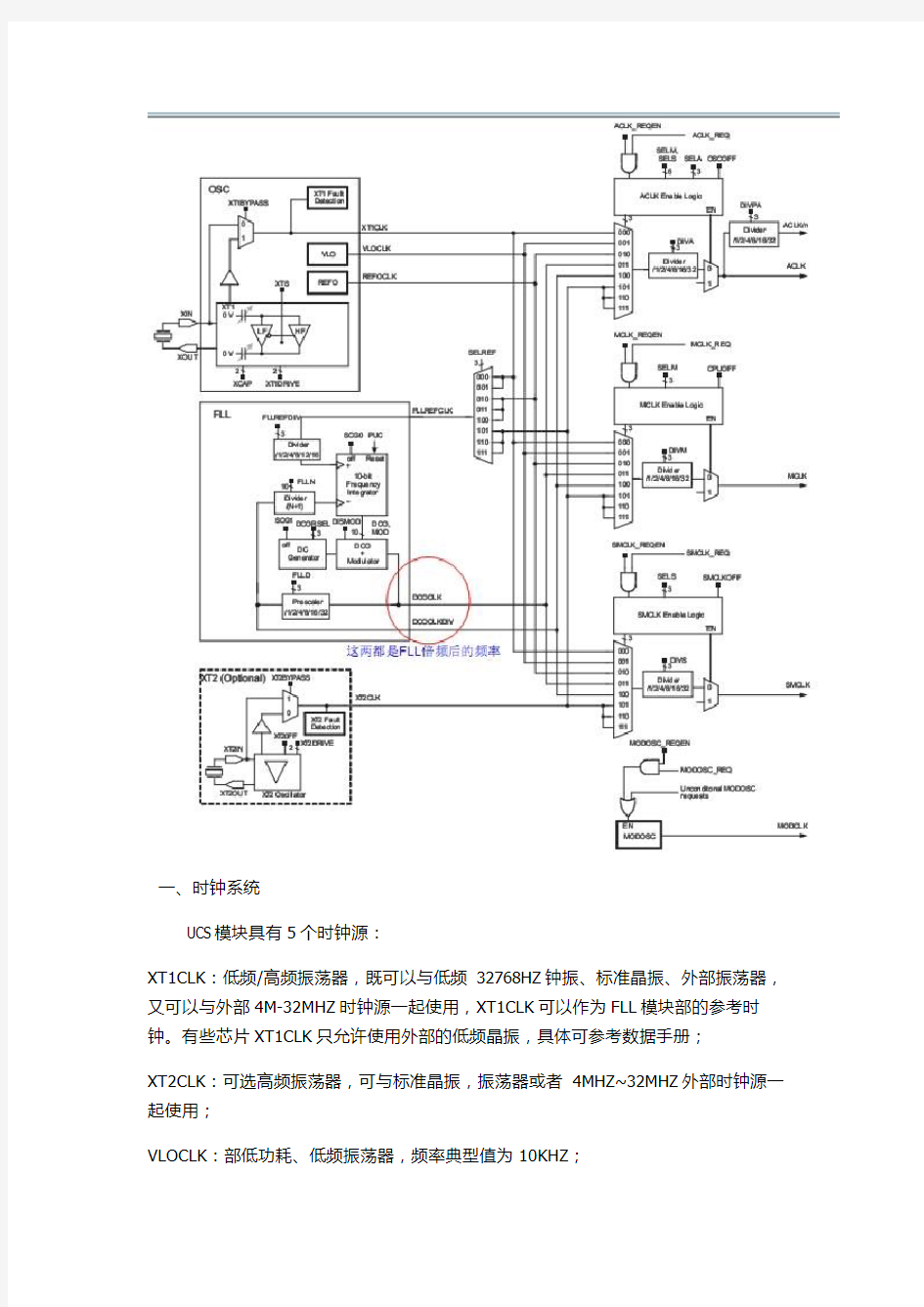

一、时钟系统

UCS模块具有5个时钟源:

XT1CLK:低频/高频振荡器,既可以与低频 32768HZ钟振、标准晶振、外部振荡器,又可以与外部4M-32MHZ时钟源一起使用,XT1CLK可以作为FLL模块部的参考时钟。有些芯片XT1CLK只允许使用外部的低频晶振,具体可参考数据手册;

XT2CLK:可选高频振荡器,可与标准晶振,振荡器或者 4MHZ~32MHZ外部时钟源一起使用;

VLOCLK:部低功耗、低频振荡器,频率典型值为10KHZ;

REFOCLK:部低频振荡器,典型值为 32768HZ,可作为 FLL基准时钟源;

DCOCLK:可以通过 FLL来稳定的部数字控制振荡器(DCO);DCOCLK经过 FLL分频后可得DCOCLKDIV。

UCS模块可以提供3种时钟信号:

ACLK:辅时钟;

MCLK:系统主时钟;

SMCLK:子系统主时钟。

二、UCS操作

PUC之后,UCS的默认配置模式如下:

XT1CLK 选择LF模式下的XT1作为时钟源,ACLK 选择 XT1CLK 作为时钟源;MCLK 选择DCOCLKDIV作为时钟源;

SMCLK 选择DCOCLKDIV作为时钟源;

FLL操作使能,FLL基准时钟(FLLREFCLK)选择XT1CLK;

XIN 和 XOUT作普通IO 口使用,禁止了 XT1 功能,直到 I/O 口重新配置为 XT1 模式;

如果有 XT2IN 和XT2OUT,则一并配置为普通 IO 口,禁止 XT2 功能。

如上所述:

默认状态下:XIN/XOUT(P7.0/1)、XT2IN/XT2OUT(P5.2/3) 为普通 IO口,振荡功能禁止;FLL基准源、ACLK时钟源是 XT1CLK,晶振失效逻辑控制位作用下均切换

到 REFOCLK,ACLK = 32768Hz;默认下FLL倍频为:31(FLLN值),DCOCLKDIV=(32+1)*32768 =1.047856MHz;默认下分频值 D=2(FLLD值),DCOCLK = 2*DCOCLKDIV = 2.097152MHz。

默认选择了使用 XT1的 FLL操作,为了启用 XT1功能,必须将与 XT1引脚对应的PSEL置位。当 XT1CLK 使用 32768Hz 晶振时,由于XT1不会立即稳定,失效逻辑控制位会立即选择 REFOCLK 作为 ACLK 时钟源。一旦晶体振荡稳定后,由于 FLL的作用,MCLK 和SMCLK 都将稳定在 1.047586MHz,Fdco稳定在 2.097152MHz。

状态寄存器(SCG0,SCG1,OSCOFF和CPUOFF)用于配置 MSP430的工作模式,使能和禁止 UCS模块中的部分功能(参考系统复位、中断和操作模式)。UCS 模块可以在程序运行中的任何时候进行配置和修改配置,配置使用寄存器

UCSCTL0~UCSCTL8。

2.1 UCS模块在超低功耗方面的特性

为了保持长时间工作或降低功耗而采用低时钟频率;

快速响应时间和快速数据处理能力需要高时钟频率;

适应各种工作温度和供电电压的稳定时钟;

低成本应用中使用准确度要求较少器件的时钟。

2.2 VLO 部低功耗低频振荡器

部 VLO能够在不需要任何外接晶振的情况下,提供 10KHz的时钟,在对时钟精度不敏感而对成本又非常敏感的场合,使用 VLO是一个非常好的选择。当 VLO 作为ACLK、MCLK、SMCLK(SELA=1、SELM=1、SELS=1)中的任何一个时钟源时,开始启动振荡。

2.3 REFO 部低频参考时钟

在对成本非常敏感时,通常不需要使用外部晶振,此时可以使用部低频参考时钟。该时钟的典型频率值为32768Hz,并可以作为用于稳定时钟模块 FLL所需要的参考时钟源 FLLREFCLK。REFO 和 FLL在不需要外接晶振的情况下,给了系统时钟设置一定的灵活性。REFO不使用时,不存在电流消耗。

REFO 在下面任何一种情况下,是处于工作允许状态的:

在活动模式到 LPM3模式下,REFO 作为ACLK 的时钟源(SELA=2 OSCOFF=0);

在活动模式下,REFO 作为 MCLK的时钟源(SELM=2 CPUOFF=0);

在活动模式到 LPM1模式下时,REFO作为 SMCLK 的时钟源(SELS=2 SMCLKOFF=0);

活动模式到LPM3模式下,REFO作为FLLREFCLK(SELREF=2)时钟源,DCO作为ACLK的时钟源(SE LA=3,4 OSCOFF=0)

在活动模式下,REFO作为FLLREFCLK(SELREF=2)时钟源,DCO 作为 MCLK的时钟源(SELA=3,4 CPUOFF=0);

活动模式到LPM1模式,REFO作为FLLREFCLK(SELREF=2)时钟源,DCO作为SMCLK时钟源(SELA=3,4 SMCLKOFF=0)

对于ACLK、MCLK、SMCLK的时钟源的选择由 UCSCTL4 控制寄存器决定:

SELA Bits10-8 选择ACLK 的时钟源

000 XT1CLK

001 VLOCLK

010 REFOCLK

011 DCOCLK

100 DCOCLKDIV

101 XT2CLK(可用),否则是DCOCLKDIV

110 保留,XT2CLK(可用),否则是DCOCLKDIV

111 保留,XT2CLK(可用),否则是DCOCLKDIV

SELS Bits6-4 选择SMCLK 的时钟源

000 XT1CLK

001 VLOCLK

010 REFOCLK

011 DCOCLK

100 DCOCLKDIV

101 XT2CLK(可用),否则是DCOCLKDIV

110 保留。XT2CLK(可用),否则是DCOCLKDIV

111 保留。XT2CLK(可用),否则是DCOCLKDIV

SELM Bits2-0 选择MCLK 的时钟源

000 XT1CLK

001 VLOCLK

010 REFOCLK

011 DCOCLK

100 DCOCLKDIV

101 XT2CLK(可用),否则是DCOCLKDIV

110 保留,XT2CLK(可用),否则是DCOCLKDIV

111 保留,XT2CLK(可用),否则是DCOCLKDIV

ACLK、MCLK、SMCLK 时钟的输出(对应 P11.0/1/2)UCSCTL5 控制寄存器决定:

DIVPA Bits14-12 外部引脚上可用的 ACLK 时钟源分频。对 ACLK 进行分频,外部引脚(P11.0)上输出。

000 fACLK/1

001 fACLK/2

010 fACLK/4

011 fACLK/8

100 fACLK/16

101 fACLK/32

110 保留。默认是 fACLK/32

111 保留。默认是 fACLK/32

DIVA Bits 10-8 ACLK 时钟源分频。对 ACLK 时钟源进行分频。

000 fACLK/1

001 fACLK/2

010 fACLK/4

011 fACLK/8

100 fACLK/16

101 fACLK/32

110 保留。默认是 fACLK/32

111 保留。默认是 fACLK/32

DIVS Bits 6-4 SMCLK 时钟源分频

000 fSMCLK/1

001 fSMCLK/2