EDA电子设计自动化实验报告山东大学信息学院

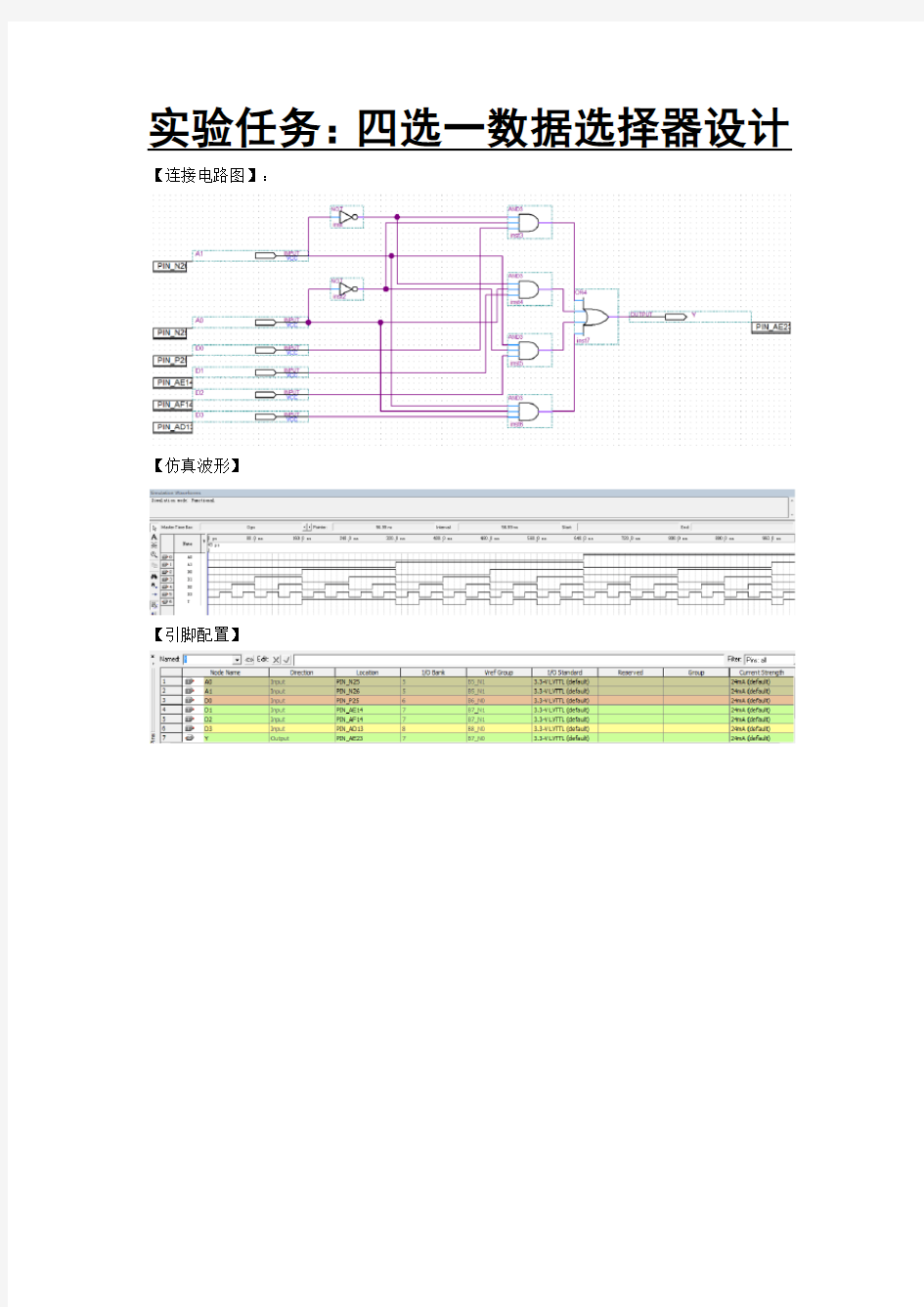

实验任务:四选一数据选择器设计【连接电路图】:

【仿真波形】

【引脚配置】

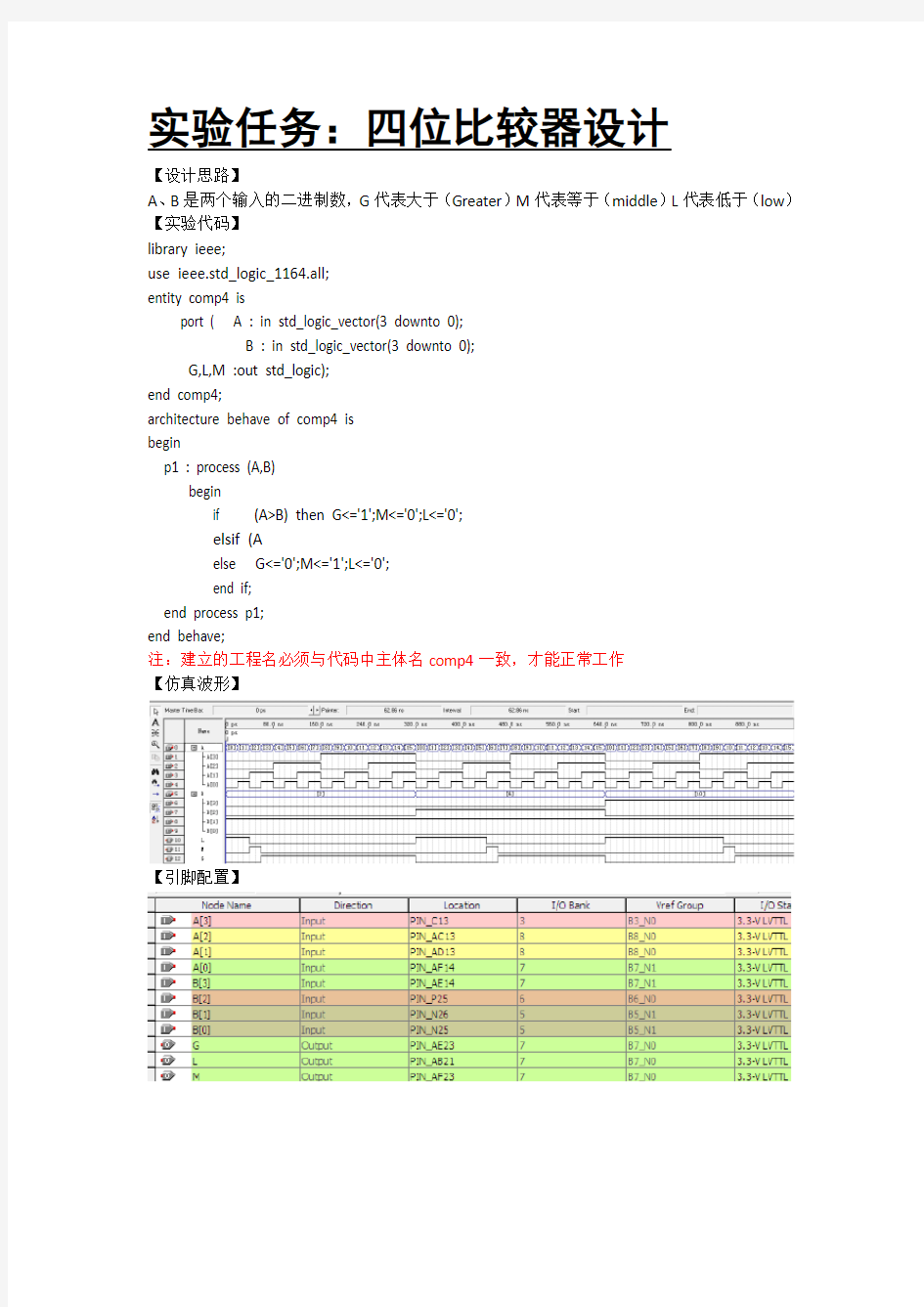

【设计思路】

A、B是两个输入的二进制数,G代表大于(Greater)M代表等于(middle)L代表低于(low)【实验代码】

library ieee;

use ieee.std_logic_1164.all;

entity comp4 is

port ( A : in std_logic_vector(3 downto 0);

B : in std_logic_vector(3 downto 0);

G,L,M :out std_logic);

end comp4;

architecture behave of comp4 is

begin

p1 : process (A,B)

begin

if (A>B) then G<='1';M<='0';L<='0';

elsif (A else G<='0';M<='1';L<='0'; end if; end process p1; end behave; 注:建立的工程名必须与代码中主体名comp4一致,才能正常工作 【仿真波形】 【引脚配置】 【设计思路】 数a,b是两个四位二进制数,和放在sum里,溢出位是cout 【实验代码】 library ieee; use ieee.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity add is port(a:in std_logic_vector(3 downto 0); b:in std_logic_vector(3 downto 0) cin:in std_logic; sum:out std_logic_vector(3 downto 0); cout:out std_logic); end add; architecture behav of add is signal aa,bb,s:std_logic_vector(4 downto 0); begin aa<='0'&a; bb<='0'&b; s<=aa+bb+cin; sum<=s(3 downto 0); cout<=s(4); end behav; 注:建立的工程名必须与代码中主体名add一致,才能正常工作作出仿真波形如下: 引脚配置如下: 实验任务:七人表决器设计 【设计思路】 定义a是七位二进制数,表示七个人的表决结果,0是否定,1是肯定 如果有4个或以上的1,那么结果y就是1 遍历a的每一个数,每遇见一个1,i=i+1,当i≥4时,y=1 【实验代码】 library ieee; use ieee.std_logic_1164.all; entity vote is port(a:in std_logic_vector(6 downto 0); y:out std_logic); end vote; architecture behav of vote is begin process(a) variable i:integer; begin i:=0; if(a(0)='1') then i:=i+1; end if; if(a(1)='1') then i:=i+1;, end if; if(a(2)='1') then i:=i+1; end if; if(a(3)='1') then i:=i+1; end if; if(a(4)='1') then i:=i+1; end if; if(a(5)='1') then i:=i+1; end if; if(a(6)='1') then i:=i+1; end if; if(i>3) then y<='1'; else y<='0'; end if; end process; end behav; 注:建立的工程名必须与代码中主体名vote一致,才能正常工作 【仿真波形】 【引脚配置】 实验任务:七段译码器(共阳极) 源代码如下: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity qiduanyima is port( a:in std_logic_vector(3 downto 0); rst:std_logic; dataout:out std_logic_vector(6 downto 0)); end qiduanyima; architecture one of qiduanyima is begin process(a) begin case a is when"0000"=>dataout<="1000000"; when"0001"=>dataout<="1111001"; when"0010"=>dataout<="0100100"; when"0011"=>dataout<="0110000"; when"0100"=>dataout<="0011001"; when"0101"=>dataout<="0010010"; when"0110"=>dataout<="0000010"; when"0111"=>dataout<="1111000"; when"1000"=>dataout<="0000000"; when"1001"=>dataout<="0010000"; when others=>dataout<="1111111"; end case; end process; end one; 注:建立的工程名必须与代码中主体名qiduanyima一致,才能正常工作 实验任务:分频器设计 【实验代码】 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; Entity my_clk is port(in_clk:in std_logic; out_clk:out std_logic); end my_clk; Architecture toe of my_clk is Begin counter:process(in_clk) Variable c1 :integer :=0; begin if(in_clk'event and in_clk='1' and c1<24999999) then c1:=c1+1; out_clk<='1'; elsif(in_clk'event and in_clk='1' and c1<49999999) then c1:=c1+1; out_clk<='0'; elsif(in_clk'event and in_clk='1' and c1=49999999) then c1:=0; out_clk<='1'; end if; end process counter; end toe; 注:建立的工程名必须与代码中主体名my_clk一致,才能正常工作【引脚配置】 实验任务:十进制计数器设计 【源代码】 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity jishuqi10 is port(en: in std_logic; to0: in std_logic; clock:in std_logic; out10:out std_logic_vector(3 downto 0); co:out std_logic); end; architecture one of jishuqi10 is signal num:integer range 0 to 10; begin process(clock) begin if en='1' then if clock'event and clock= '1' then if num=9 then num<=0; else num<=num+1; end if; end if; end if; if to0='0' then num<=0; end if; if num=9 then co<='1'; else co<='0'; end if; case num is when 1=>out10<="0001"; when 2=>out10<="0010"; when 3=>out10<="0011"; when 4=>out10<="0100"; when 5=>out10<="0101"; when 6=>out10<="0110"; when 7=>out10<="0111"; when 8=>out10<="1000"; when 9=>out10<="1001"; when 0=>out10<="0000"; when others=>out10<="0000"; end case; end process; end; 注:建立的工程名必须与代码中主体名jishuqi10一致,才能正常工作 作出仿真波形如下: 保存并封装后,重新建立一个工程,把十进制译码器和七段译码管联合使用: 引脚配置如下: 实验任务:百进制计数器设计十进制封装后,保存并重新建立一个工程,连接成为100进制的计数器: 引脚配置如下: 实验任务:巴克码发生器 源代码如下: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity bakema is port(clk:in std_logic; bakema:out std_logic; jp:out std_logic); end; architecture one of bakema is signal count:integer range 0 to 6; begin process(clk) begin jp<=clk; if clk'event and clk= '1' then if count=6 then count<=0; else count<=count+1; end if; end if; case count is when 0=>bakema<='1'; when 1=>bakema<='1'; when 2=>bakema<='1'; when 3=>bakema<='0'; when 4=>bakema<='0'; when 5=>bakema<='1'; when 6=>bakema<='0'; when others=>bakema<='0'; end case; end process; end; 注:建立的工程名必须与代码中主体名bakema一致,才能正常工作作出仿真波形如下: 引脚配置如下: 实验任务:红绿灯设计 【设计思路】 东西方向和南北方向的代码大致相近 都是配置了50个状态(num) 红色(red)是状态26-50 绿色(gre)是状态6-25 黄色(yel)是状态1-5 当复位键按下(to0=1)时,南北方向会置状态50(红),东西置25(绿)然后状态参数(num)每秒减一,不断循环 【实验代码】 南北方向芯片的代码: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity nanbei is port(en: in std_logic; to0: in std_logic; clock:in std_logic; out10:out std_logic_vector(3 downto 0); out20:out std_logic_vector(3 downto 0); red: out std_logic; gre: out std_logic; yel: out std_logic); end; architecture one of nanbei is signal num:integer range 1 to 50; begin process(clock) begin if en='1' then if clock'event and clock= '1' then if num=1 then num<=50; else num<=num-1; end if; end if; end if; if to0='0' then num<=50; end if; if num>25 then red<='1';gre<='0';yel<='0'; elsif num>5 then red<='0';gre<='1';yel<='0'; else red<='0';gre<='0';yel<='1'; end if; if 44 out20<="0010"; elsif 34 out20<="0001"; elsif 25 out20<="0000"; elsif 25=num then out20<="0010"; elsif 14 out20<="0001"; elsif 5 out20<="0000"; elsif 0 out20<="0000"; end if; case num is when 1=>out10<="0001"; when 2=>out10<="0010"; when 3=>out10<="0011"; when 4=>out10<="0100"; when 5=>out10<="0101"; when 6=>out10<="0001"; when 7=>out10<="0010"; when 8=>out10<="0011"; when 9=>out10<="0100"; when 10=>out10<="0101"; when 11=>out10<="0110"; when 12=>out10<="0111"; when 13=>out10<="1000"; when 14=>out10<="1001"; when 15=>out10<="0000"; when 16=>out10<="0001"; when 17=>out10<="0010"; when 18=>out10<="0011"; when 19=>out10<="0100"; when 20=>out10<="0101"; when 21=>out10<="0110"; when 22=>out10<="0111"; when 23=>out10<="1000"; when 24=>out10<="1001"; when 25=>out10<="0000"; when 26=>out10<="0001"; when 27=>out10<="0010"; when 28=>out10<="0011"; when 29=>out10<="0100"; when 30=>out10<="0101"; when 31=>out10<="0110"; when 32=>out10<="0111"; when 33=>out10<="1000"; when 34=>out10<="1001"; when 35=>out10<="0000"; when 36=>out10<="0001"; when 37=>out10<="0010"; when 38=>out10<="0011"; when 39=>out10<="0100"; when 40=>out10<="0101"; when 41=>out10<="0110"; when 42=>out10<="0111"; when 43=>out10<="1000"; when 44=>out10<="1001"; when 45=>out10<="0000"; when 46=>out10<="0001"; when 47=>out10<="0010"; when 48=>out10<="0011"; when 49=>out10<="0100"; when 50=>out10<="0101"; when others=>out10<="0000"; end case; end process; end; end; 注:建立的工程名必须与代码中主体名nanbei一致,才能正常工作 东西方向芯片的代码如下 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity dongxi is port(en: in std_logic; to0: in std_logic; clock:in std_logic; out10:out std_logic_vector(3 downto 0); out20:out std_logic_vector(3 downto 0); red: out std_logic; gre: out std_logic; yel: out std_logic); architecture one of dongxi is signal num:integer range 1 to 50; begin process(clock) begin if en='1' then if clock'event and clock= '1' then if num=1 then num<=50; else num<=num-1; end if; end if; end if; if to0='0' then num<=25; end if; if num>25 then red<='1';gre<='0';yel<='0'; elsif num>5 then red<='0';gre<='1';yel<='0'; else red<='0';gre<='0';yel<='1'; end if; if 44 out20<="0010"; elsif 34 out20<="0001"; elsif 25 out20<="0000"; elsif 25=num then out20<="0010"; elsif 14 out20<="0001"; elsif 5 out20<="0000"; elsif 0 out20<="0000"; end if; case num is when 1=>out10<="0001"; when 2=>out10<="0010"; when 3=>out10<="0011"; when 4=>out10<="0100"; when 5=>out10<="0101"; when 6=>out10<="0001"; when 7=>out10<="0010"; when 8=>out10<="0011"; when 9=>out10<="0100"; when 10=>out10<="0101"; when 11=>out10<="0110"; when 12=>out10<="0111"; when 13=>out10<="1000"; when 14=>out10<="1001"; when 15=>out10<="0000"; when 16=>out10<="0001"; when 17=>out10<="0010"; when 18=>out10<="0011"; when 19=>out10<="0100"; when 20=>out10<="0101"; when 21=>out10<="0110"; when 22=>out10<="0111"; when 23=>out10<="1000"; when 24=>out10<="1001"; when 25=>out10<="0000"; when 26=>out10<="0001"; when 27=>out10<="0010"; when 28=>out10<="0011"; when 29=>out10<="0100"; when 30=>out10<="0101"; when 31=>out10<="0110"; when 32=>out10<="0111"; when 33=>out10<="1000"; when 34=>out10<="1001"; when 35=>out10<="0000"; when 36=>out10<="0001"; when 37=>out10<="0010"; when 38=>out10<="0011"; when 39=>out10<="0100"; when 40=>out10<="0101"; when 41=>out10<="0110"; when 42=>out10<="0111"; when 43=>out10<="1000"; when 44=>out10<="1001"; when 45=>out10<="0000"; when 46=>out10<="0001"; when 47=>out10<="0010"; when 48=>out10<="0011"; when 49=>out10<="0100"; when 50=>out10<="0101"; when others=>out10<="0000"; end case; end process; end; 注:建立的工程名必须与代码中主体名dongxi一致,才能正常工作 【电路连接】 东西南北连接同一个时钟,输出各自接两个显示译码管(qiduanyima),时钟信号用分频器(my_clk)提供 引脚配置如下: