A CMOS Voltage Controlled Ring Oscillator with Improved Frequency Stability

SCIENTIFIC PUBLICATIONS OF THE STATE UNIVERSITY OF NOVI PAZAR

S ER.A:A PPL.M ATH.I NFORM.AND M ECH.vol.2,1(2010),1-9.

A CMOS Voltage Controlled Ring Oscillator with Improved

Frequency Stability

G.Jovanovi′c,M.Stojˇc ev,Z.Stamenkovic

Abstract:A CMOS voltage controlled ring oscillator based on N-stage single-ended chain of different inverter types is described in this paper.The proposal is characterized by increased frequency stability(?f/f<2%)in term of power supply voltage variations in respect to stan-dard solutions(?f/f>4%).The presented results are obtained using HSpice simulation and CMOS library model,level49,for1.2μm technology.

Keywords:V oltage controlled oscillator,ring oscillator,CMOS,frequency stability.

1Introduction

A voltage controlled oscillator(VCO)is one of the most important basic building blocks in analog and digital circuits[1]-[6].There are many different implementations of VCOs. One of them is a ring oscillator based VCO,which is commonly used in the clock generation subsystem.The main reason of ring oscillator popularity is a direct consequence of its easy integration.Due to their integrated nature,ring oscillators have become an essential building block in many digital and communication systems.They are used as voltage-controlled oscillators(VCO’s)in applications such as clock recovery circuits for serial data communications[1],[2],disk-drive read channels[3],on-chip clock distribution[4],and integrated frequency synthesizers[5],[6].The design of a ring oscillator involves many tradeoffs in terms of speed,power,area,and application domain[13].The problem of designing a ring oscillator is in focus of our interest in this paper.This paper proposes a suitable method for increasing frequency stability of a CMOS ring VCO.

The rest of the text is organized as follows.In Section2,we give a brief review of volt-age controlled ring oscillators,and de?ne some crucial operating parameters.Hardware description of the proposed ring oscillator is presented in Section3.In addition we present the simulation results which relate to frequency stability in terms of temperature and supply Manuscript received January27,2010;revised April17,2010;accepted May31,2010.

G.Jovanovi′c,M.Stojˇc ev are with the University of Niˇs,Faculty of Electronic Engineering,Serbia;Z. Stamenkovic is with the IHP GmbH,Innovations for High Performance Microelectronics Leibniz-Institut fuer innovative Mikroelektronik,Im Technologiepark25,15236Frankfurt(Oder)Germany

1

A CMOS V oltage Controlled Ring Oscillator with Improved Frequency Stability2 voltage variation.In Section4,we de?ne the terms of jitter and phase noise in ring oscilla-tors,and present the appropriate simulation results.Finally,conclusion is given in Sections 5.

2CMOS ring VCO-a review

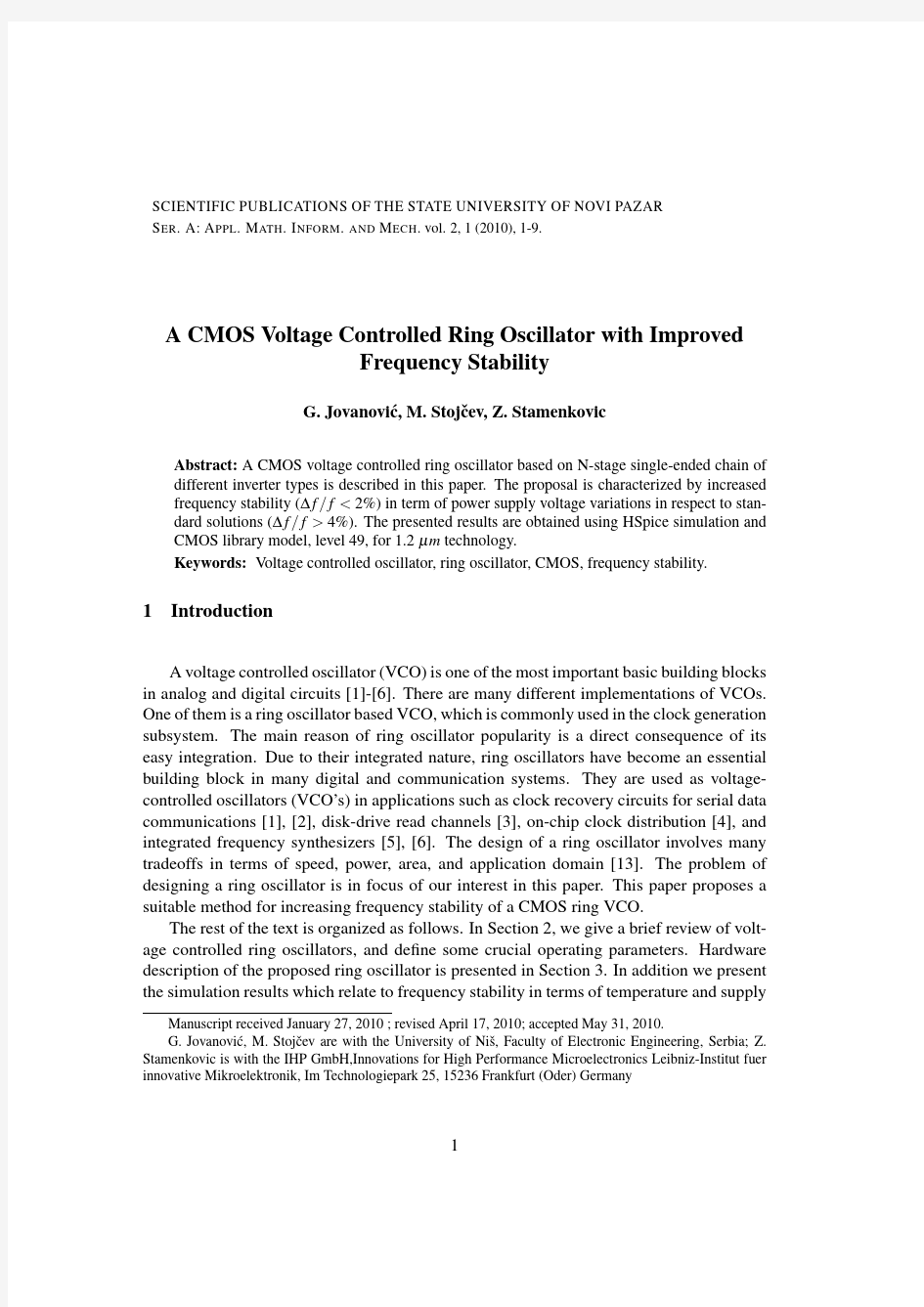

A ring oscillator is comprised of a number of delay stages,with the output of the last stage fed back to the input of the?rst.To achieve oscillation,the ring must provide a phase shift of2πand have unity voltage gain at the oscillation frequency.Each delay stage must provide a phase shift ofπ/N,where N is the number of delay stages.The remaining phase shift is provided by a dc inversion[7].This means that for an oscillator with single-ended delay stages,an odd number of stages are necessary for the dc inversion.If differential delay stages are used,the ring can have an even number of stages if the feedback lines are swapped.Examples of these two circuits are shown in Fig. 1.

A 1

A

2

A

N

A

1

A

2

A

N

(a)

(b)

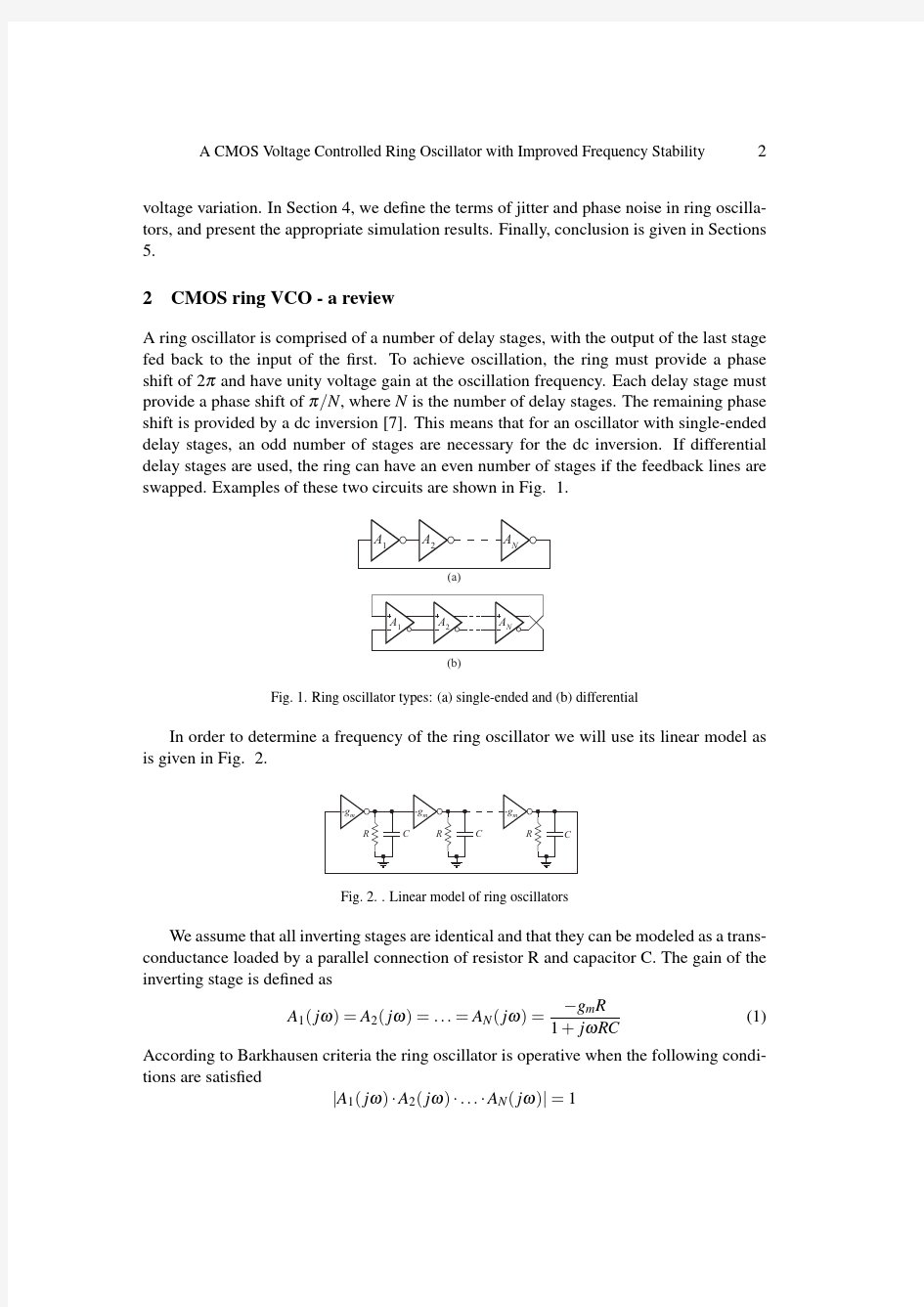

Fig.1.Ring oscillator types:(a)single-ended and(b)differential In order to determine a frequency of the ring oscillator we will use its linear model as is given in Fig. 2.

Fig.2..Linear model of ring oscillators

We assume that all inverting stages are identical and that they can be modeled as a trans-conductance loaded by a parallel connection of resistor R and capacitor C.The gain of the inverting stage is de?ned as

A1(jω)=A2(jω)=...=A N(jω)=

?g m R

1+jωRC

(1)

According to Barkhausen criteria the ring oscillator is operative when the following condi-tions are satis?ed

|A1(jω)·A2(jω)·...·A N(jω)|=1

A CMOS V oltage Controlled Ring Oscillator with Improved Frequency Stability3

∠A(jω)=θ=arctanωRC=2kπ

N

(2) The frequency of oscillation is given by

ω0=tanθ

RC

(3) and the minimal single stage gain is

g m R≥

1

cosθ

(4)

Alternatively we can derive an equation for the frequency of oscillation if we assume that each stage provides a delay of t d.The signal goes through each of the N delay stages once to provide the?rst phase shift in a time of Nt d.Then,the signal must goes through each stage a second time to obtain the remaining phase shift,resulting in a total period of2Nt d. Therefore,the frequency of oscillation is

f0=

1

2Nt d

(5)

The dif?culty in obtaining a value for the frequency arises when trying to determine t d, mainly due to the nonlinearities and parasitic of the circuit.As is referred in[7]the delay per stage is de?ned as the change in output voltage at the midpoint of the transition,V SW, divided by the slew rate,I ss/C,resulting in a delay per stage of CV SW/I https://www.360docs.net/doc/2718722691.html,ing de?nition (5),the oscillation frequency is given by

f0=

I ss

2NV sw C

(6)

3Ring oscillator inverting stage

As we have already mentioned,the ring oscillators is realized with N inverter stages.There are numerous types of inverter stages by which a ring oscillator can be realized[8],[9]. Some of the standard solutions are pictured in Fig. 3.

Designs given in Fig.3b),c),d)are of current starved type,for which the charging and discharging output capacitor current is limited by a bias circuit.More details related to realization of this type of inverter stage can be found in References[8],[9].

Relative frequency deviations in term of temperature variations for3-stages ring os-cillators based on type of inverters stages presented in Fig.3are given in Fig. 4.In general all frequency deviations have similar behavior,but the basic type(Fig.3a))and current starved with symmetrical load(Fig.3d))inverters have the highest,while cur-rent starved with output-switching(Fig.3b))inverter has the lowest sensitivity.The ratio of relative frequency deviations between basic type(Fig.3a))and current starved with output-switching(Fig.3b))inverters is5:1.

A CMOS V oltage Controlled Ring Oscillator with Improved Frequency Stability4

(a)

Fig.3.Invertor:(a)basic type;(b)current starved with output-switching;(c)current starved with power-switching;(d)current starved with symmetrical load.

Relative frequency deviations in term of power voltage supply variations for3-stages ring oscillators based on type of inverters stages presented in Fig.3are given in Fig. 5. As can be seen from Fig5,the basic type(Fig.3(a))and current starved with symmetrical load(Fig.3(d))inverters have characteristics with negative slope,while current starved with output-switching(Fig.3(b))and current starved with power-switching(Fig.3(c)) inverters have characteristics with positive slope.Absolute value of inverters sensitivity in function to power supply voltage variation is within a range of10%excluding current starved inverter with power-switching(Fig.3c))inverters which has sensitivity of5%. Taking into consideration the opposite slope characteristics of the relative frequency de-viations in terms of power voltage supply variations of the mentioned inverters(Fig.5), we can conclude that is reasonable to design a ring oscillator composed of cascade chain of inverters.For example,odd numbered inverters can have positive,while even numbered negative slope.In this way,the relative frequency deviation in term of power voltage supply can be drastically reduced(more than100%).

Several typical design solutions of3-,5-and7-stages ring oscillators with reduced sensitivity are given in Fig.6a),b)and c),respectively.We call them as combined ring

A CMOS V oltage Controlled Ring Oscillator with Improved Frequency Stability5

Fig.4.Relative frequency deviation in term of temperature variation

Fig.5.Relative frequency deviation in term of power supply voltage variation oscillators.Let note that in combined ring oscillators the odd numbered inverter stages are implemented with basic type,while even numbered as current starved with output-switching inverters.

The relative frequency deviations in term of power supply voltage for all three type of ring oscillators pictured in Fig.6are given in Fig.7.By analyzing the results presented in Fig.7we can conclude the following:The relative sensitivity of the ring oscillator from Fig.6a)is less than2%,while for those given in Fig.6b)and c)is less than1%.

A CMOS V oltage Controlled Ring Oscillator with Improved Frequency Stability 6V

ctrl

V dd V dd

dd

dd V ctrl

V dd V dd dd dd V dd

dd

V ctrl

V dd V dd dd dd V dd dd V dd

dd

https://www.360docs.net/doc/2718722691.html,bined ring VCOs

Fig.7.Relative frequency deviation in term of power supply voltage variation for proposed ring VCOs

A CMOS V oltage Controlled Ring Oscillator with Improved Frequency Stability7 4Jitter and phase noise in ring oscillators

In general,CMOS circuits are sensitive both to power supply and temperature variations,as well as to noise generated in IC’s building blocks(noise is inserted through power supply and the substrate).Due to these effects,the propagation delay,t d,is variable[10],[11],[12]. As a consequence there are variations in t d,in respect to its nominal value.This deviation is manifested as variation of the rising and falling pulse edges,and is referred as jitter(see Fig.8).

d

Fig.8.Jitter effect

As can be seen from Fig.8the jitter for the rising edge is de?ned as a rms time error value,?t d2.The normalized jitter value is de?ned as a ratio between the effective time

error and its nominal delay value,i.e.?t drms

t d .

Consider now a VCO with nominal period T0,and with a timing error accompanying each period that is Gaussian,with zero mean and variance?t VCO2.If this timing error is expressed in terms of phase,?Φ=2π?t/T0,then the variance of the phase error per cycle of oscillation is given by[10]

σ2Φ=(2π)2(

?T VCOrms

T0

)2

(7)

The amount of phase noise for all types of ring oscillators discussed in this paper is sketched in Fig.9.By analyzing Fig.9we can conclude that the best performance(phase noise approx.0.06rad)have ring oscillators based on current starved inverters with output-switching,while the worst(phase noise approx.0.3rad)correspond to ring oscillators realized with basic type or current starved with power-switching https://www.360docs.net/doc/2718722691.html,bined ring oscillators,composed of basic and current starved with output-switching inverters,have approximately phase noise within the range0.16-0.2rad.

A CMOS V oltage Controlled Ring Oscillator with Improved Frequency Stability8

Fig.9.Relative frequency deviation in term of power supply voltage variation for proposed ring VCOs

5Conclusion

Ring oscillators are basic building blocks of complex integrated circuits.They are mainly used as clock generating circuits.Many different types of ring oscillators are presented in literature[1]-[4].They differ in respect to architectural,realization of inverters stages, number of inverter stages,etc.In this paper we have considered realization of ring oscillator based on four different types of single-ended inverters.The simulation was performed using HSpice Version03.2006and library model for1.2μm CMOS technology.According to the obtained simulation results we can conclude:

a)that for frequency stability in terms of temperature variations the best performance

(?f/f<2%)has current starved inverters with output-switching;

b)that for frequency stability in terms of power supply voltage variations the best per-

formance(?f/f<4%)has current starved inverters with power-switching;

c)by realizing combined types of ring oscillator the relative frequency deviation in

terms of power supply voltage variations can be signi?cantly decreased(?f/f<2%) in respect to the best standard solutions(?f/f>4%).

d)in respect to phase noise,ring oscillators based on current starved inverters with

output-switching have the best performance(phase noise approx.0.06rad).

References

[1] C.H.P ARK,O.K IM,B.K IM,A1.8-GHz self-calibrated phase locked loop with precise

I/Q matching,IEEE J.Solid-State Circuits,vol.36,(2001),777-783.

[2]L.S UN AND T.A.K WASNIEWSKI,A1.25-GHz0.35-m monolithic CMOS PLL based on a

multiphase ring oscillator,IEEE J.Solid-State Circuits,vol.36,(2001),910-916.

[3]J.S AVOJ AND B.R AZAVI,A10-Gb/s CMOS clock and data recovery circuit with a half-rate

linear phase detector,IEEE J.Solid-State Circuits,vol.36,(2001),761-767.

A CMOS V oltage Controlled Ring Oscillator with Improved Frequency Stability9

[4] C.K.K.Y ANG,R.F ARJAD-R AD,M.A.H OROWITZ,A0.5-m CMOS4.0-Gbit/s serial

link transceiver with data recovery using oversampling,IEEE J.Solid-State Circuits,vol.33, (1998),713-722.

[5]M.A LIOTO,G.P ALUMBO,”Oscillation frequency in CML and ESCL ring oscillators”,

IEEE Trans.Circuits Syst.I,vol.48,(2001),210-214.

[6] B.R AZAVI,A2-GHz 1.6-mW phase-locked loop,IEEE J.Solid-State Circuits,vol.

32,(1997),730-735.

[7]S.Docking,M.Sachdev,A Method to Derive an Equation for the Oscillation Frequency

of a Ring Oscillator,IEEE Trans.on Circuits and Systems-I:Fundamental Theory and Applications,vol.50,2,(2003),259-264.

[8]G.J OVANOVI′C,M.S TOJˇCEV,Current starved delay element with symmetric load,Interna-

tional Journal of Electronics,V ol.93,3,(2006),167-175.

[9]O.-C.C HEN,R.S HEEN,A Power-Ef?cient Wide-Range Phase-Locked Loop,IEEE Journal

of Solid State Circuits,vol.37,1,(2002),51-,.

[10]T ODD C HARLES W EIGANDT,Low-Phase-Noise,Low-Timing-Jitter Design Techniques for

Delay Cell Based VCOs and Frequency Synthesizers,PhD dissertation,University of Cali-fornia,Berkeley,1998.

[11]S.D OCKING,AND M.S ACHDEV,An Analytical Equation for the Oscillation Frequency of

High-Frequency Ring Oscillators,IEEE Journal of Solid State Circuits,vol.39,3,(2004), 533-537.

[12] A.H AJIMIRI,S.L IMOTYRAKIS,T.L EE,Jitter and Phase Noise in Ring Oscillators,IEEE

Journal of Solid State Circuits,vol.34,6,(1999),790-804.

[13]G.J OVANOVI′C,M.S TOJˇC EV,A Method for Improvement Stability of a CMOS Voltage

Controlled Ring Oscillators,ICEST2007,Proceedings of Papers,vol.2,pp.715-718,Ohrid, Jun2007.

γ射线能谱测量

γ射线能谱测量 ——物理0805 乔英杰u200810200 王振宇u200810256 实验背景:19世纪下半叶,物理学家对X射线和阴极射线进行了大量的研究,导致了放射性、电子以及α、β、γ射线的发现,这些射线的发现同时也为原子科学的发展奠定了基础。 自20世纪进入原子能时代,科学家对射线进行了更进一步的研究,射线在科学技术中开始渗透,根据γ射线具有波长短、能量高、穿透能力强和对细胞有很强的杀伤力的特性,γ射线的应用也成了一门新兴产业,现在它已经应用到了国民经济和社会生活的各个领域,特别是在工农业、医疗卫生和生物学方面取得了巨大的成果和效益,为科学技术和人类历史的进程起了巨大而深刻的影响。 目前γ射线的应用正在蓬勃快速的发展,应用领域仍在不断拓宽,它以低能耗、无污染、无残留、安全卫生等优点,深受众多行业的青睐,可是,其危害性也不容忽视。我们需要对γ射线深入了解,才能在降低其危害性的同时让其更好的为我们服务。本实验采用闪烁探测器和多道脉冲幅度分析器对γ射线的能量分布谱进行测量,以便我们了解用闪烁探测器测量γ射线的方法,学会分析能谱的特征及其影响因素。 实验原理: 1、闪烁探测器工作原理:闪烁探测器探测γ射线时,γ光子与物质作用不直接产生电离,而是发生光电效应、康普顿效应、电子对效应,闪烁体的原子、分子、电离或激发的作用来自三种效应所产生的次级电子。这样,我们就得到了对应于γ射线能量强度的电信号。之后,光电倍增管将所得电信号放大(倍增管阴极与阳极之间有十余个打那级,每个打那级均发生电子的倍增现象),其阳极最后收集电子的电极,与射级跟随器电路相连,使收集到的电子流以电压脉冲的方式输出。 2、γ闪烁能谱仪的工作原理:如下图(1)所示,整个仪器的信号传递大致是:由γ射线放射源放出的γ射线被闪烁探测器接受并转换为电压脉冲,前置放大器和脉冲放大器对探测器输出的电压脉冲进行放大,最后这些脉冲被多道分析器采集、处理。 多道分析器的到是指在分析器中存在的记录不同高度脉冲的位置。我们在试验中采用的是1024道分析器,即将脉冲电压范围分成1024份,然后计算机记录探测器输出的脉冲落在每份范围上的数目。

简单电路设计设计大全

装饰材料购销合同 简单电路设计设计大全 1.保密室有两道门,只有当两道门都关上时(关上一道门相当于闭合一个开关),值班室内的指示灯才会发光,表明门都关上了.下图中符合要求的电路是 2.小轿车上大都装有一个指示灯,用它来提醒司机或乘客车门是否关好。四个车门中只要有一个车门没关好(相当于一个开关断开),该指示灯就会发光。下图为小明同学设计的模拟电路图,你认为最符合要求的是 3.中考试卷库大门控制电路的两把钥匙分别有两名工作人员保管,单把钥匙无法打开,如图所示电路中符合要求的是 ”表示)击中乙方的导电服时,电路导通,4.击剑比赛中,当甲方运动员的剑(图中用“S 甲 乙方指示灯亮。下面能反映这种原理的电路是 5.家用电吹风由电动机和电热丝等组成,为了保证电吹风的安全使用,要求:电动机不工作时,电热丝不能发热;电热丝发热和不发热时,电动机都能正常工作。如图所示电路中符合要求的是( )

6.一辆卡车驾驶室内的灯泡,由左右两道门上的开关S l、S2和车内司机右上方的开关S3共同控制。S1和S2分别由左右两道门的开、关来控制:门打开后,S1和S2闭合,门关上后,S l和S2断开。S3是一个单刀三掷开关,根据需要可将其置于三个不同位置。在一个电路中,要求在三个开关的共同控制下,分别具有如下三个功能:(1)无论门开还是关,灯都不亮; (2)打开两道门中的任意一道或两道都打开时,灯就亮,两道门都关上时,灯不亮;(3)无论门开还是关,灯都亮。如图所示的四幅图中,符合上述要求的电路是 A.图甲 B.图乙 C.图丙 D.图丁 7.教室里投影仪的光源是强光灯泡,发光时必须用风扇给予降温。为了保证灯泡不被烧坏,要求:带动风扇的电动机启动后,灯泡才能发光;风扇不转,灯泡不能发光。则在如图3所示的四个电路图中符合要求的是 ( ) 8.一般家用电吹风机都有冷热两挡,带扇叶的电动机产生风,电阻R产生热。冷热风能方便转换,下面图3中能正确反应电吹风机特点的电路图是 ( ) 9.飞机黑匣子的电路等效为两部分。一部分为信号发射电路,可用等效电阻R1表示,用开关S1控制,30天后自动断开,R1停止工作。另一部分为信息存储电路,可用等效电阻R2表示,用开关S2控制,

用Si光电二极管标定软X射线探测器_曹继红

第12卷 第1期2004年2月 光学精密工程 Optics and Precis ion E ngineering Vol.12 No.1 Jan.2004 文章编号 1004-924X(2004)01-0118-04 用Si光电二极管标定软X射线探测器 曹继红,尼启良,陈 波 (中国科学院长春光学精密机械与物理研究所,吉林长春130033) 摘要:为了实现软X射线波段光源相对光谱分布的测量,引进了一种利用新型软X射线波段传递标准探测器—Si光电二极管对软X射线探测器进行标定。标定了软X射线波段光谱测量实验中常用的探测器—通道电子倍增器在放大电压为1.3kV时的量子效率,并对实验结果进行了分析,得出在8~30n m波段内探测器标定误差为5.7%~8.9%。 关 键 词:软X射线探测器;软X射线;硅光电二极管;标定;量子效率 中图分类号:TN366 文献标识码:A Calibration of soft X-ray detector C AO Ji-hong,NI Qi-liang,CHE N Bo (Changchun Institute of Optics,Fine Me chanics&Physics, Chinese A cademy of Scienc es,Changc hun130033,China) A bstract:In order to measure the r elative spectrum distribution of soft X-ray source,it is proposed to calibrate the channel electr on multiplier(CE M)using a silic on transfer standard photodiode calibrated by NIST.The quantum effi-ciency of the CE M has been determined using the calibration method proposed while CE M was biased to1.3kV.The analysis of calibration results indicates that the calibration error of CE M is11%~17%in the8~30nm region. Key words:soft X-ray detector;soft X-ray;silicon photodiode;detector calibration;quantum efficienc y 1 引 言 实验室经常需要测量软X光源的绝对或相对光谱分布,并对其光谱特性进行研究。在过去的十几年里,这种要求在基础和应用研究方面更是与日俱增。如医学领域,由于只有某个波段的X 射线能治疗肿瘤,就必须知道X射线源是否在这个波段有最大的辐射强度。然而,在实际光谱测量中,单色仪、探测器在不同的波段对光源的辐射有不同的响应效率,未经标定的测量系统的测量结果不能反映光源光谱辐射的真实情形,所以需要对单色仪、探测器在不同波段的响应效率进行标定。标定软X射线探测器的传统方法是利用同步辐射、稀有气体电离室或壁稳氩弧灯等标准(或传递标准)仪器进行标定,而本文则是利用一种新型的传递标准探测器—Si光电二极管对软X 射线探测器进行标定。虽然Si光电二极管在可见光和红外线等波段已得到广泛应用,但在软X射线波段的使用在国内尚无先例。 收稿日期:2003-11-22;修订日期:2003-12-04. 基金项目:国家重点基金项目(No.10333010)

最详细解读射频芯片

最详细解读射频芯片 传统来说,一部可支持打电话、发短信、网络服务、APP应用的手机,一般包含五个部分部分:射频部分、基带部分、电源管理、外设、软件。 射频部分:一般是信息发送和接收的部分; 基带部分:一般是信息处理的部分; 电源管理:一般是节电的部分,由于手机是能源有限的设备,所以电源管理十分重要; 外设:一般包括LCD,键盘,机壳等; 软件:一般包括系统、驱动、中间件、应用。 在手机终端中,最重要的核心就是射频芯片和基带芯片。射频芯片负责射频收发、频率合成、功率放大;基带芯片负责信号处理和协议处理。那么射频芯片和基带芯片是什么关系? 1. 射频芯片和基带芯片的关系 先讲一下历史,射频(Radio Frenquency)和基带(Base Band)皆来自英文直译。其中射频最早的应用就是Radio——无线广播(FM/AM),迄今为止这仍是射频技术乃至无线电领域最经典的应用。 基带则是band中心点在0Hz的信号,所以基带就是最基础的信号。有人也把基带叫做“未调制信号”,曾经这个概念是对的,例如AM为调制信号(无需调制,接收后即可通过发声元器件读取内容)。 但对于现代通信领域而言,基带信号通常都是指经过数字调制的,频谱中心点在0Hz的信号。而且没有明确的概念表明基带必须是模拟或者数字的,这完全看具体的实现机制。 言归正传,基带芯片可以认为是包括调制解调器,但不止于调制解调器,还包括信道编解码、信源编解码,以及一些信令处理。而射频芯片,则可看做是最简单的基带调制信号的上变频和下变频。 所谓调制,就是把需要传输的信号,通过一定的规则调制到载波上面让后通过无线收发器(RF Transceiver)发送出去的工程,解调就是相反的过程。 2.工作原理与电路分析 射频简称RF射频就是射频电流,是一种高频交流变化电磁波,为是Radio Frequency的缩写,表示可以辐射到空间的电磁频率,频率范围在300KHz~300GHz之间。每秒变化小于1000次的交流电称为低频电流,大于10000次的称为高频电流,而射频就是这样一种高频电流。高频(大于10K);射频(300K-300G)是高频的较高频段;微波频段(300M-300G)又是射频的较高频段。射频技术在无线通信领域中被广泛使用,有线电视系统就是采用射频传输方式。

简易门铃电路设计

《电子线路CAD》课程论文题目:简易门铃电路的设计

1 电路功能和性能指标 简易门铃是一种简单的门铃电路,它由分立元件和中规模集成芯片的构成,主要采用NE555定时器电路和扬声器组成门铃,利用多谐振荡电路来制作一简易单音门铃电路。它主要由一个NE555、一个47uf的电容、一个0.047uf电容、一个0.01uf电容、一个36kΩ的电阻、一个30kΩ的电阻、两个22k电阻、一个喇叭、两个IN4148高速开关二极管、一个9013三极管、一个开关和一个6v电源组成。NE555作为多谐振荡器,发出脉冲波。与传统的门铃相比,其可靠性、抗干扰性都较好,应用领域也相对较广泛。 2 原理图设计 2.1原理图元器件制作 方法和步骤: ①右键点击项目文件,选择追加新文件到项目中,在二级菜单下选择Schematic Library。 ②在放置菜单中,选择放置矩形。 ③在放置菜单中选择放置引脚。 ④在放置引脚时,按Tab键,选择引脚属性。 图1 注:在放置引脚的过程中,引脚有一端会附带着一个×形灰色的标记,该标记表示引脚端是用来连接外围电路的,所以该端方向一定要朝外,而不能向着矩形的方向。若需要调整引脚的方向,可按键盘撒花上的空格键,每按一次,可将引脚逆时针旋转90°。

2.2 原理图设计 步骤: ①创建PCB工程项目,执行File→New→Project→PCB Project,在弹出对话框中选择Protle Pcb类型并点击OK。将新建默认名为“PCB Project1.PrjPCB”的项目保存,命名为“简易门铃”。 ②创建原理图,在该项目文件名上点击右键,选择追加新文件到项目中,在二级菜单下选择Schematic。 ③保存项目目录下默认名为“Sheet1.SchDOC”的原理图文件。并命名为“简易门铃”。 ⑤绘图环境其他参数采用默认设置。 图2 编译原理图步骤: ①在原理图编辑页面,执行“Project→Compile PCB Project 简易门铃.PRJPCB” 菜单命令。 ②在Messages工作面板中,出现提醒为“Warning”的检查结果可以忽略。 图3

X射线探测器的发展趋势

PILATUS X射线光子计数探测器 PILATUS系列

PILATUS 探测器 一、概述 1、混合像素探测器,为您的实验室精心准备PILATUS 混合像素探测器的设计是X 射线探测领域的一次革命性成果,其能够实现最好的数据质量。该探测器将单光子计数和混合像素技术这两项关键技术相结合,应用于同步辐射和常规实验室光源等各个领域。单光子计数技术能够消除所有探测器噪声,并提供优质的实验数据。在采集数据时,能够有效排除读出噪声和暗电流的干扰,其在实验室光源的应用中具有特别优势。实验室X 射线光源相比于同步辐射光源光强低得多,因而在成像过程中需要更长的曝光时间,其获得的信号也要弱的多。由于排除了暗电流和 读出噪声,PILATUS 探测器更加适合在实验室使用。混合像素技术可以直接探测X 射线,与其他探测器技术相比能够获得更清晰,更易分辨的信号。加上读取时间短和连续采集的特点,PILATUS 探测器可以高效提供优质数据。低功耗和低冷却需求,为您提供一个维护量极小的探测器系统,。PILATUS 探测器系列是专为您在实验室中的需求定制,并且提供具有无与伦比价值的同步辐射验证的成熟探测技术。利用PILATUS 独特的功能,可以从你的最具挑战性的样品获得最佳的 2、针对您的需求 PILATUS 探测器在众多同步辐射束线上获得成功应用。PILATUS 的独特功能在实验室和相关工业应用的优势也很明显。现在PILATUS 的产品家族,包括一系列的PILATUS 探测器,能够满足您在实验室的独特需求。固定能量标定和简化的读出电子器件可以完美匹配实验室相关需求,而且PILATUS 完全符合您的预算。 混合像素技术和单光子计数技术,这两项能够提升数据质量和采集效率的关键技术,在所有PILATUS 探测器中完美应用。越来越多的实验室和工业应用的仪器可配备或升级为PILATUS 探测器。您可以在设备中自由集成PILATUS 探测器模块,也可以直接采用 PILATUSOEM 合作伙伴的现成产品。 3、OEM 合作整机合作 PILATUS 探测器是现成的配套产品, 可以选择仪器的OEM 配套合作: - JJ X 射线 - 理学 - STOE -Xenocs 器 传感器层厚度[μm] 表1:基于PTB 实验室的BESSY II 实验装置上测量的PILATUS 传感器的量子效率。 4、可定制,以符合您的要求 除了标准的320微米厚的硅传感器,你可以定制您的PILATUS 探测器450或1000微米厚的硅传感器以匹配您的X 射线光源能量(见表1)。这样能够在所有常见的实验室X 射线能量下实现高量子效率。水冷机型PILATUS300K 和300K-W 提供了可选的真空兼容性。此定制使得探测器能够在真空中使用,如在SAXS 装置的飞行管中。连续可调的能量阈值的选项可以有效抑制荧光信号

溴化镧探测器效率的标定

溴化镧探测器效率的标定 利用三种γ射线标准源(137Cs、60Co、152Eu),标定了一个溴化镧闪烁体探测器能量区间内的本征探测效率。然后在中国原子能科学研究院的高压倍加器上,利用16O*反应法得到6.13 MeV高能γ射线,对该探测器的6.13MeVγ射线的本征探测效率进行了标定。最后用最小二乘法对效率曲线进行拟合,给出了较宽能量范围内溴化镧探测器的本征效率。 标签:LaBr3:Ce3+探测器;本征探测效率;最小二乘法 1 引言 1.1 溴化镧探测器概述 溴化镧(LaBr3:Ce3+)探测器是近几年发展起来的新型卤化物闪烁体探测器,它是由LaBr3掺杂少量激活剂Ce3+(铈)元素组成的。与常用的NaI(Tl)等闪烁体探测器相比,LaBr3:Ce3+探测器主要优势在于它拥有很好的能量分辨率和极短的闪烁衰减时间[1]。 1.2 探测效率 探测效率可以分为两大类:源探测效率和本征探测效率[3]。其定义是: 其中,?赘是探测器的灵敏体积对源所张的立体角。 由于源距足够远和方便得到立体角,在计算时将直径为2 mm标准源近似为点源。用MCNP4C软件计算了0.611MeV时γ标准源由面源近似为点源的误差。经计算,误差在2.5%内。 2 实验过程 2.1 γ标准源实验 分别对137Cs、60Co、152Eu进行测定,得到如下能谱。如图2-图4其中用137Cs的662keV的能量点计算了能量分辨率。FWHW=19.126 η=ΔE/E=2.89%。 2.2 6.13 MeV能点的实验刻度 3 实验数据处理 参考文献 [1]谢建军等.卤化镧系LnX3(Ce)闪烁晶体的研究进展[J].无机材料学报,

GM计数管能量响应测定

GM 计数管的能量响应范围确认 如果要保证GM 计数管的剂量测量的置信度,就必须刻度出探测系统的γ能量响应。由于没有合适的系列单能γ辐射源,为此利用康普顿散射原理将强60 Co 源释放出的γ射线转换为系列单能γ射线进行探测系统γ能量响应的标定。然后拟合出能量响应曲线。 一、原理和方法 当辐射源(60 Co )释放的γ光子与靶物质(一般选用Cu 或Al )相互作用时,产生康普顿散射效应。散射光子的能量为: 201(1cos )E E E m c θ'=+- 0m 为电子静止质量,θ为散射γ光子的出射角。由上式可知,当确定能量的入射光子与靶物质发生作用时,对于确定的θ角,就有与之相对应确定能量的散射γ光子产生。 二、主要事项 一般来说,对GM 计数管能量响应的测定,其要考虑的影响因素多。首先即为辐射屏蔽,对辐射的屏蔽,由于实验环境中的墙壁和地面等散射物的影响,存在大量的空间杂散本底,一般来说在离散射靶70cm 测点处比本底信号强度高4个量级。因此,减少本底干扰、提高信噪比是能量响应标定的关键技术之一。为此可以做如下图所示的设计。 1、放射源; 2、准直器; 3、散射靶; 4、探测器 铅屏蔽的厚度一般为50cm ,用以阻挡放射源放出的γ射线直接到达探测系统产生干扰,屏蔽体后壁需开一斜喇叭口,以避免射线经后壁反照到散射靶。同时,为了降低通道内本底的干扰,需对准直器进行特殊设计。一般来说,根据GM 计数管灵敏区的大小,准直器前喇叭口直径为4cm ,中段口径为2cm ,使辐射源释放的γ射线照射到斜喇叭口的管壁后不再反射到散射靶上;准直器的后喇叭口直径为5cm ,放探测器一面的斜度要适当,一方面要阻挡辐射源释放的γ射线直接到达散射角为25°的探测器,另一方面要尽量减少γ射线经管壁到散射靶的量;不放探测器一面的斜度要以避免γ射线经准直器内管壁反射后到达探测器和散射靶上为宜。 另外, γ光子与靶物质发生作用产生散射了的同时, 还伴随有康普顿电子射线的产生。因此在探测器与散射靶之间需放Fe (约1mm 厚度)吸收片以消除电子射线对探测器输出的影响。

2017年大学生数学建模A题CT系统标定成像论文

CT系统参数标定及成像摘要:本文运用MATLAB等工具对已给出的数据进行分析和处理,通过反射投影算法,等比例转换法,radon变换和iradon变换,还原180次扫描信息和图形信息。 对于问题1,通过radon变换法,在MATLAB中得出该介质以正方形托盘左上角为原点的坐标系下的位置分布图,然后根据题目中已经给出的介质物体实际图,以椭圆圆心为原点建立直角坐标系,得出两个坐标系之间的比例关系,通过位置与长度的等比例变换得出旋转中心在正方形托盘中的坐标为(-8.7755, 6.1697),通过观察附件2发现存在探测器接收到的非零信号个数稳定在28个,对比小圆的直径得出探测器的间距为0.2857mm,探测器接收到的非零信号个数与角度曲线没有发生突变,且最高点与最低点横坐标相差90次,可以认为每次旋转1度,初始位置与坐标系X轴正方向夹角为29度。 对于问题2,通过使用iradon变换,得出了投影重建结构的解,对附件3中某未知介质的投影数据进行滤波反投影重建运算,实现从其它空间向图像空间进行转换的过程,最终通过MATLAB运行结果获得该未知介质模型的重建图像,得出该未知介质在正方形托盘中的几何形状和位置信息,然后采用比例变换的方式,根据10个点的位置和相对于实物图位置,得出这10个位置介质点的吸收率结果。 对于问题3,采用与问题2相似的方式,利用MATLAB中的iradon算法,根据附件5中提供的另一未知介质的吸收信息,通过反投影重建可以得到该未知介质的位置,形状和吸收率等信息,同样采用等比例变换的方式,根据点的位置和相对于实物图的位置,得出这10个位置点的吸收率结果。 对于问题4,通过对已经给定的数据进行分析,用iradon验证扫描次数对成像质量的影响,在不同滤波环境下比较成像质量,分别对18,36,90,180个角度投影进行观察和分析,能够得出随着投影角度个数的增加,图像的重影越来越少,也即是稳定性和精确度越来越高。运用shepp-lagon模型重新优化模型。 关键词:反射投影重建;MATLAB软件;radon变换;iradon变换;比例变换;成像质量;

数字钟的设计与仿真

目录 摘要 (3) 前言 (4) 第一章理论分析 1.1 设计方案 (5) 1.2 设计目的 (5) 1.3 设计指标 (6) 1.4 工作原理及其组成框图 (6) 第二章系统设计 2.1 多谐振荡器 (8) 2.2 计数器 (10) 2.3 六十进制电路 (12) 2.4 译码与LED显示器 (13) 2.5 校时电路 (14) 2.6 电子时钟原理图 (15) 2.7 仿真与检测 (16) 2.8 部分元器件芯片结构图 (18) 2.9 误差分析 (19) 第三章小结 心得体会 (20) 致谢 (21) 参考文献 (22)

摘要 时钟,自从它发明的那天起,就成为人类的朋友,但随着时间的推移,科学技术的不断发展,人们对时间计量的精度要求越来越高,应用越来越广。怎样让时钟更好的为人民服务,怎样让我们的老朋友焕发青春呢?这就要求人们不断设计出新型时钟。在这次的毕业设计中,针对一系列问题,设计了如下电子钟。 本系统由555多谐振荡器,分频器,计数器,译码器,LED显示器和校时电路组成,采用了CMOS系列(双列直插式)中小规模集成芯片。总体方案手机由主题电路和扩展电路两大分组成。 其中主体电路完成数字钟的基本功能,扩展电路完成数字钟的扩展功能,进行了各单元设计,总体调试。 关键词:555多谐振荡器;分频器;计数器;译码器;LED显示器

前言 20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。数字钟已成为人们日常生活中:必不可少的必需品,广泛用于个人家庭以及车站、码头、剧场、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大的方便。由于数字集成电路技术的发展和采用了先进的石英技术,使数字钟具有走时准确、性能稳定、集成电路有体积小、功耗小、功能多、携带方便等优点,因此在许多电子设备中被广泛使用。 电子钟是人们日常生活中常用的计时工具,而数字式电子钟又有其体积小、重量轻、走时准确、结构简单、耗电量少等优点而在生活中被广泛应用,因此本次设计就用数字集成电路和一些简单的逻辑门电路来设计一个数字式电子钟,使其完成时间及星期的显示功能。 本次设计以数字电子为主,分别对1S时钟信号源、秒计时显示、分计时显示、小时计时显示、整点报时及校时电路进行设计,然后将它们组合,来完成时、分、秒的显示并且有走时校准的功能。并通过本次设计加深对数字电子技术的理解以及更熟练使用计数器、触发器和各种逻辑门电路的能力。电路主要使用集成计数器,例如CD4060、CD4518,译码集成电路,例如CD4511,LED数码管及各种门电路和基本的触发器等,电路使用5号电池共电,很适合在日常生活中使用。

γ射线能谱测量

γ射线能谱测量 0802班,程道辉,U200710222 0802班,安志强,U200710210 前言: γ射线首先由法国科学家P.V.维拉德发现的,γ射线是光子,是由原子核的衰变产生的,当原子核从激发态跃迁到较低能态或基态时,就有可能辐射出γ射线。γ射线强度按能量分布即为γ射线能谱。通过分析γ能谱可以确定原子核激发态的能级,对放射性分析、同位素应用及鉴定核素等方面都有重要的意义。本实验采用闪烁探测器和多道脉冲分析器对γ射线的能量分布谱进行测量. 原子核的衰变产生γ射线,不同能级间的衰变跃迁可以产生不同能量的γ射线,我们可以通过射线探测器对这些γ射线的能谱分析就可以推断出原子核的一些性质。射线探测器的是根据射线与物质的相互作用规律研制的,可分为“信号型”和“径迹型”, γ射线在与物质相互作用的时候可能产生三种效应:光电效应、康普顿效应和电子对效应,这三种效应会产生次级电子,γ闪烁探测器就是利用这些次级电子激发电离闪烁体分子,当闪烁分子退激发时会放出大量的光子,并照射在光阴极上产生光电子,这些光电子经过倍增管放大而产生可探测的电信号并通过电子仪器的记录得到γ射线能谱,具体结构图如下: 经过闪烁探测器后得到的电信号为电压脉冲信号,其幅值与入射的γ射线的能量成正比,线号脉冲的个数正比于γ射线的强度。接收电信号的仪器可以分为单道和多道脉冲分析器,其功能是通过测量不同幅值电压脉冲信号的脉冲个数来画出入射γ射线能量与强度的关系。 单道分析器有一个下甄别电压1V 和一个上甄别电压2V ,只有当脉冲幅值在 12V V 之间的信号才能通过,这样就可以测量出信号幅值在12V V 之间的个数,通过改变1V 并保持12V V 不变,就可以测量出不同幅值所对应的个数,即为γ射

射频电路和射频集成电路线路设计

射频电路和射频集成电路线路设计(9天) 培训时间为9天 课程特色 1)本讲座总结了讲演者20多年的工作,报告包括 o设计技术和技巧的经验, o获得的美国专利, o实际工程设计的例子, o讲演者的理论演译。 o 【主办单位】中国电子标准协会 【协办单位】智通培训资讯网 【协办单位】深圳市威硕企业管理咨询有限公司 o 2)本讲座分为三个部分: A. 第一部分讨论和強调在射频电路设计中的设计技术和技巧, 着重论述设计中关鍵性 的技术和技巧,譬如,阻抗匹配,射频接地, 单端线路和差分线路之間的主要差別,射频集成电路设计中的难题……可以把它归类为橫向论述. 到目前为止,这种着重于设计技巧的論述是前所未有的,也是很独特的。讲演者认为,作为一位合格的射频电路设计的设计者,不论是工程师,还是教授,应当掌握这一部分所论述的基本的设计技术和技巧,包括: ?阻抗匹配; ?接地; ?射频集成电路设计; ?测试 ?画制版图; ? 6 Sigma 设计。 B. 第二部分: 描述射频系统的基本参数和系统设计的基本原理。

C. 第三部分: 提供个别射频线路设计的基本知识。这一部份和现有的有关射频电路和 射频集成电路设计的书中的论述相似, 其內容是讨论一个个射频方块,譬如,低噪声放大器,混频器,功率放大器,壓控振蕩器,頻率综合器……可以把它归类为纵向论述,其中的大多数内容来自本讲座的讲演者的设计 ?在十几年前就已经找到了最佳的低噪声放大器的设计方法但不曾经发表过。在低噪声放大器的设计中可以同时达到最大的增益和最小的噪 声; ?获得了可调谐濾波器的美国专利; ?本讲座的讲演者所建立的用单端线路的设计方法来进行差分对线路的设计大大简化了设计并缩短了线路仿真的时间; ?获得了双线巴伦的美国专利。 学习目标在本讲座结束之后,学员可以了解到 o比照数码电路,射頻电路设计的主要差別是什麼? o什么是射频设计中的基本概念? o在射频电路设计中如何做好窄带的阻抗匹配? o在射频电路设计中如何做好宽带的阻抗匹配? o在射频线路板上如何做好射频接地的工作? o为什么在射频和射频集成电路设计中有从单端至双差分的趋势? o为什么在射频电路设计中容许误差分析如此重要? o什么是射频和射频集成电路设计中的主要难题?射频和射频集成电路设计师如何克服这些障碍?

第5章 电路级设计与仿真

第5章 电路级设计与仿真 电路设计技术是EDA 技术的核心和基础。电路设计可以分为数字电路、模拟电路、常规电路和集成电路。现代EDA 与传统的电路CAD 相比其主要区别是比较多地依赖于电路描述语言,常用的电路描述语言有描述模拟电路的SPICE (Simulation Program with Integrated Circuit Emphasis )语言,描述数字电路的硬件描述语言。弄清电路结构形式与语言的关系以及各种语言的基本功能是学习EDA 技术非常重要的环节,这也是本章的主要目的所在。 本章将从最基本的数学和物理模型出发,引入程序化模型,介绍模拟电路与仿真、数字电路与仿真。从一般的设计原理上讲,常规电路与集成电路并没有本质的区别,本章采用的例子主要以常规电路为主,其基本设计原理也同样适合于相应的集成电路,关于集成电路设计将在后续章节中详细介绍。 5.1模拟电路模型与SPICE 程序 5.1.1 模拟电路模型 电路的物理模型是指利用电路元件(如:电阻、电容、电感等无源元件,三极管、集成电路等有源元件)按照一定的电路连接方式进行连接的图形描述方法。其中电路元件是器件的物理模型,器件模型的建立以及器件的连接是按照电学参数和基本电路功能的描述为依据的。这种电路的物理模型也叫做等效电路模型,也就是我们常说的电路。 电路的物理模型是一种简化了的直观的电路图,可以十分方便地反映电路的连接关系和基本功能,但是这个模型并不能进行直接分析,如果要对电路进行分析,还需要建立电路的数学模型。电路数学模型是根据电路的物理模型和电路分析原理得到的电路行为特性及各参数之间的数学关系。 我们在《电路分析原理》中已经建立起这样的概念,这个概念是基于一些基本的电路定律和基本定理,例如基尔霍夫定律、叠加定理、代文宁定理、欧姆定律等。 基尔霍夫定律:; 0i n 1k k =∑=0v n 1k k =∑=欧姆定律:V=IR 对于特定的电路,这些定律和定理构成了电路中物理参数之间的特定关系,这种特定关系是约束电路的基本数学模型。不同的元件具有不同的参数运算或转换关系,这种关系如表5-1所示,这是一些最基本和最简单的元件及其数学模型,复杂元件的数学模型也是由这些简单的元件按照功能需求组成的。因此,描述模拟电路的数学模型是微分方程或代数方程。 《电路分析基础》课程就是在建立了这些电路模型的基础上对电路进行分析,不论是建立电路模型或者是分析运算,电路分析是在基于电压、电流的等效模型进行的。 表5-1 电路元件及其数学描述 电路元件 符号 物理模型 数学模型(VI 关系) R v = R·i C i = C·dv/dt v = L t ·di/d v = v s , i 电阻电容电感 L 电压源 Vs 103

γ射线法在医用186Re样品分析中的应用

第23卷第2期2000年2月 核技术 NUCLEARTECHNIQUES V01.23No2 February,2000 Y射线法在医用186Re样品分析中的应用 方克明刘静恬庄道玲周桢堂石最惠 (中国科学院上海原子拔研究所上海201800) 摘要描述了以Y射线测量为基础分析医用186Re样品的步骤和方法.用HPGeY射线探测器对 NH?Re0?进行了丫(X)射线谱测量.根据谱中Y(X)射线的能量和强度鉴别了1懿Re,鉴定了 1蛳Re的核纯度,通过与标准源进行比较,给出了样品的放射性活度。 关键词丫(x)射线谱,”6Re,按纯度,放射性活度 中图分类号065735 1“置e作为新一代的放射性治疗药物核素,以其特有的半衰期和核衰变性质越来越受到核医学界的重视“1。“。Re的产生方法通常有两种;一种是天然铼在反应堆中用中子照射后经过化学处理得到的有载体“Re,一种是”5w在加速器上用质子照射后经过化学分离得到的无载体“5Re。原料的不纯、照射时的副反应和化学分离的不彻底会造成”6Re制品的不纯,半衰期的差异会引起放射性核素的含量随存放时问的长短而变化。为保证”6Re核素标记放射性药物可用于临床使用,详细可靠地了解这些信息至关重要。为此,需要对“Re制品的核纯度、放射性杂质、放射性活度以及它们随时间的变化关系进行准确的检测和分析。本工作用高分辨率HPGeY射线探测器测量N}王4ReOt样品的Y射线谱,用一套完善的谱学分析方法对1,射线谱进行分析,鉴别1“Re,得出”6Re的放化纯度、放射性活度和它们随时问的变化关系。 1实验方法 1_1仪器和材料 GMx一20190一PHPGeY射线探测器,美国ORTEc公司产品,灵敏体积为毋4.65cm x677cm.对叫Co的1332_5keVY射线的能量分辨率为1.9keVjPC—CAMAC多参数数据获取系统,国内研制j971213号NH4Re04溶液,中国核动力研究设计院第一研究所提供,由天 然铼在该所高通量堆中用堆中子照射后经化学处理得到;2085号”2Eu标准源,中国原子能科 学研究院提供,1985年11月28日标定的放射性活度为(4.03±O.12)×103Bq.根据放射性活度衰减公式A=Aoe….至1997年12月15日使用时放射性活度衰减为(2.18±O06)×106Bq。1.2刻度 在铅室中用”。Eu标准源对探测器进行能量刻度和效率刻度。源距8cm,铅室厚50cm, 内部尺寸为40.Ocm×40.0cm×32.0cm。以PC—CAMAC多参数数据获取系统记录Y射线谱,测量数据储存于磁盘上。 采用类似Okano…等程序结构的微机解谱程序SANA拟合出较强v射线的峰位置和峰面 积。用线性多项式对能量与峰位置的关系进行最小二乘法拟舍得到能量剡度曲线。由计数率收稿日期199806—29.修回日期:199耻10—2s 万方数据

电子电路设计与仿真工具

电子电路设计与仿真工具 我们大家可能都用过试验板或者其他的东西制作过一些电子制做来进行实践。但是有的时候,我们会发现做出来的东西有很多的问题,事先并没有想到,这样一来就浪费了我们的很多时间和物资。而且增加了产品的开发周期和延续了产品的上市时间从而使产品失去市场竞争优势。有没有能够不动用电烙铁试验板就能知道结果的方法呢?结论是有,这就是电路设计与仿真技术。 说到电子电路设计与仿真工具这项技术,就不能不提到美国,不能不提到他们的飞机设计为什么有很高的效率。以前我国定型一个中型飞机的设计,从草案到详细设计到风洞试验再到最后出图到实际投产,整个周期大概要10年。而美国是1年。为什么会有这样大的差距呢?因为美国在设计时大部分采用的是虚拟仿真技术,把多年积累的各项风洞实验参数都输入电脑,然后通过电脑编程编写出一个虚拟环境的软件,并且使它能够自动套用相关公式和调用长期积累后输入电脑的相关经验参数。这样一来,只要把飞机的外形计数据放入这个虚拟的风洞软件中进行试验,哪里不合理有问题就改动那里,直至最佳效果,效率自然高了,最后只要再在实际环境中测试几次找找不足就可以定型了,从他们的波音747到 F16都是采用的这种方法。空气动力学方面的数据由资深专家提供,软件开发商是IBM,飞行器设计工程师只需利用仿真软件在计算机平台上进行各种仿真调试工作即可。同样,他们其他的很多东西都是采用了这样类似的方法,从大到小,从复杂到简单,甚至包括设计家具和作曲,只是具体软件内容不同。其实,他们发明第一代计算机时就是这个目的(当初是为了高效率设计大炮和相关炮弹以及其他计算量大的设计)。 电子电路设计与仿真工具包括SPICE/PSPICE;multiSIM7;Matlab;SystemView;MMICAD LiveWire、Edison、Tina Pro Bright Spark等。下面简单介绍前三个软件。 ①SPICE(Simulation Program with Integrated Circuit Emphasis):是由美国加州大学推出的电路分析仿真软件,是20世纪80年代世界上应用最广的电路设计软件,

简单逻辑电路设计与仿真

VHDL与集成电路CAD 实验四十二简单逻辑电路设计与仿真 验项目名称:简单逻辑电路设计与仿真 实验项目性质:普通实验 所属课程名称:VHDL与集成电路CAD 实验计划学时:2学时 一.实验目的 1.学习并掌握MAX+PLUSⅡ的基本操作; 2.学习在MAX+PLUSⅡ下设计简单逻辑电路与功能仿真的方法。 二.实验要求 1.MAX+PLUSⅡ使用的相关内容; 2.阅读并熟悉本次实验的内容; 3.用图形输入方式完成电路设计; 4.分析器件的延时特性。 三.实验主要仪器设备和材料 1.PC机。 2.MAX+PLUSⅡ软件。 四.实验内容及参考实验步骤 1.用D触发器设计一个4进制加法计数器并进行功能仿真。 (1)开机,进入MAX+PLUSⅡ系统。 (2)点击File菜单Project子菜单之Name项,出现Project Name 对话框。为当 前的实验选择恰当的路径并创建项目名称(注意MAX+PLUSⅡ不识别中文 路径)。 (3)点击File菜单之New项,出现对话框,选择Graphic Editor File输入方式。 出现图形编辑窗口(注意界面发生了一定变化)。 (4)双击空白编辑区,出现Enter Symbol 对话框(或点击Symbol 菜单Enter Symbol项)从Symbol Libraries项中选择mf子目录(双击),然后在 Symbol File 中选择7474元件(双D触发器);在prim子目录中选择电源 vcc、输入脚input 和输出引脚output。(或直接在Symbol Name 中输入所 需元件的名称回车亦可)。 (5)在图形编辑窗口中的左侧点击连线按钮(draws a horizontal or vertical line), 并完成对电路的连线。各元件布置在合适的位置上(参考电路如图1)。 (6)在引脚的PIN_NAME处左键双击使之变黑,键入引脚名称。 (7)点击File菜单Project子菜单之set project to current file,也可点击工具栏中

射频介绍

《射频集成电路设计基础》讲义 课程概述 关于射频(RF) 关于射频集成电路 无线通信与射频集成电路设计 课程相关信息 RFIC相关IEEE/IEE期刊和会议

关于射频 ? 射频= Radio Frequency (RF) → Wireless! ? Why Wireless? – 可移动(Mobile) – 个人化(Personalized) – 方便灵活(Self-configuring) – 低成本(在某些情况下) – and more ... ? Why Wired? <<>><>?

<<>><>? ? 多高的频率才是射频? ? 为什么使用高频频率? 30-300kHz LF 中波广播530-1700 kHz 300kHz-3MHz MF 短波广播 5.9-26.1 MHz 3-30MHz HF RFID 13 MHz 30-300MHz VHF 调频广播88-108 MHz 我们关心的频段 300-1000MHz UHF (无线)电视54-88, 174-220 MHz 1-2 GHz L-Band 遥控模型72 MHz 2-4 GHz S-Band 个人移动通信900MHz, 1.8, 1.9, 2 GHz 4-8 GHz C-Band WLAN, Bluetooth (ISM Band) 2.4-2.5GHz, 5-6GHz 注1:本表主要参考国外标准 注2:ISM =Industrial, Scientific and Medical

关于射频集成电路 ? 是什么推动了RFIC的发展? – Why IC? – 体积更小,功耗更低,更便宜→移动性、个人化、低成本 – 功能更强,适合于复杂的现代通信网络 – 更广泛的应用领域如生物芯片、RFID等 ? Quiz: why not fully integrated? ? 射频集成电路设计最具挑战性之处在于,设计者向上必须 懂得无线系统的知识,向下必须具备集成电路物理和工艺 基础,既要掌握模拟电路的设计和分析技巧,又要熟悉射频 和微波的理论与技术。(当然,高技术应该带来高收益:) <<>><>?

模电课程设计简易门铃

科技学院 《模拟电子技术》课程设计 题目简易门铃 学生梦蔚 专业班级11级电科一班 学号201131002 院(系)电气工程学院 指导教师月英 完成时间 2013年5月16日

目录 1 课程设计的目的 (1) 2 课程设计的任务与要求 (1) 3 实验设计方案及论证 (1) 3.1方案一 (1) 3.2方案二 (2) 3.3两种方案的比较 (3) 4 设计原理及功能说明 (4) 5硬件的制作与调试 (6) 6 总结 (12) 参考文献 (13) 附录1:总体电路原理图 (14) 附录2:元器件清单 (15)

1 课程设计的目的 ?通过该项目的学习,学生应当能够读懂项目任务书,看懂任务书中的电路原理图,分析电路工作原理,根据项目实训评价明确制考核要求和评分标准。 ?能熟练运用万用表检测各元器件的质量。 ?能熟练使用各焊接工具按照电路原理较长和工艺要求完成电路的连接。 ?熟练运用电子测量工具完成电路的调试和故障的排除。 ?具备一定的团队合作开发能力。 2 课程设计的任务与要求 ?设计一个门铃电路,两端接6v的电压,设置一个按钮开关,当按下开关时发出门铃在任听觉围的“铃”声,松开开关,则声音消失。 ?其中先设计出电路图,再通过电路图演示软件演示出其可用性,最后进行实际操作进行电路元件的选择与焊接。 ?要求用部中断实现,当按下门铃时,门铃发出响声,直到释放。 3 实验设计方案及论证 3.1 方案一

图3-1 原理图 电路原理: 由VT1、VT2及相关元件组成多谐振荡器,用以控制两种音调转换,由VT3、VT4等组成音频振荡器,当VT2导通时,相当于R1与R2并联,这时产生一种音调,当VT2截止时,只有R1参与音频振荡器工作,因此产生的是另外一种声音,电路中的R1、R2和C5的值决定了音调的高低当按下门铃开关后,门铃便会交替产生二种不同音调的声音。 3.2 方案二

电路四输入与非门设计 - 副本

四输入与非门课程设计任务书 学生姓名:专业班级: 指导教师:工作单位: 题目: CMOS四输入与非门电路设计 初始条件: 计算机、ORCAD软件、L-EDIT软件 要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求) 1、课程设计工作量:2周 2、技术要求: (1)学习ORCAD软件、L-EDIT软件。 (2)设计一个CMOS四输入与非门电路。 (3)利用ORCAD软件、L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。 2013.11.25-11.27学习ORCAD软件、L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 2013.11.28-12.5对CMOS四输入与非门电路进行设计仿真工作,完成课设报告的撰写。 2013.12.6 提交课程设计报告,进行答辩。 指导教师签名:年月日 系主任(或责任教师)签名:年月日

摘要........................................................................ I Abstract ................................................................... II 1 绪论 (1) 2 设计内容及要求 (2) 2.1 设计的目的及主要任务 (2) 2.2 设计思想 (2) 3软件介绍 (3) 3.1 OrCAD简介 (3) 3.2 L-Edit简介 (4) 4 COMS四输入与非门电路介绍 (5) 4.1 COMS四输入与非门电路组成 (5) 4.2 四输入与非门电路真值表 (6) 5 Cadence中四输入与非门电路的设计 (7) 5.1 四输入与非门电路原理图的绘制 (7) 5.2 四输入与非门电路的仿真 (8) 6 L-EDIT中四输入与非门电路版图的设计 (10) 6.1 版图设计的基本知识 (10) 6.2 基本MOS单元的绘制 (11) 6.3 COMS四输入与非门的版图设计 (13) 7课程设计总结 (14) 参考文献 (15)