M74HC699中文资料

M54/74HC696/697M54/74HC698/699

March 1993

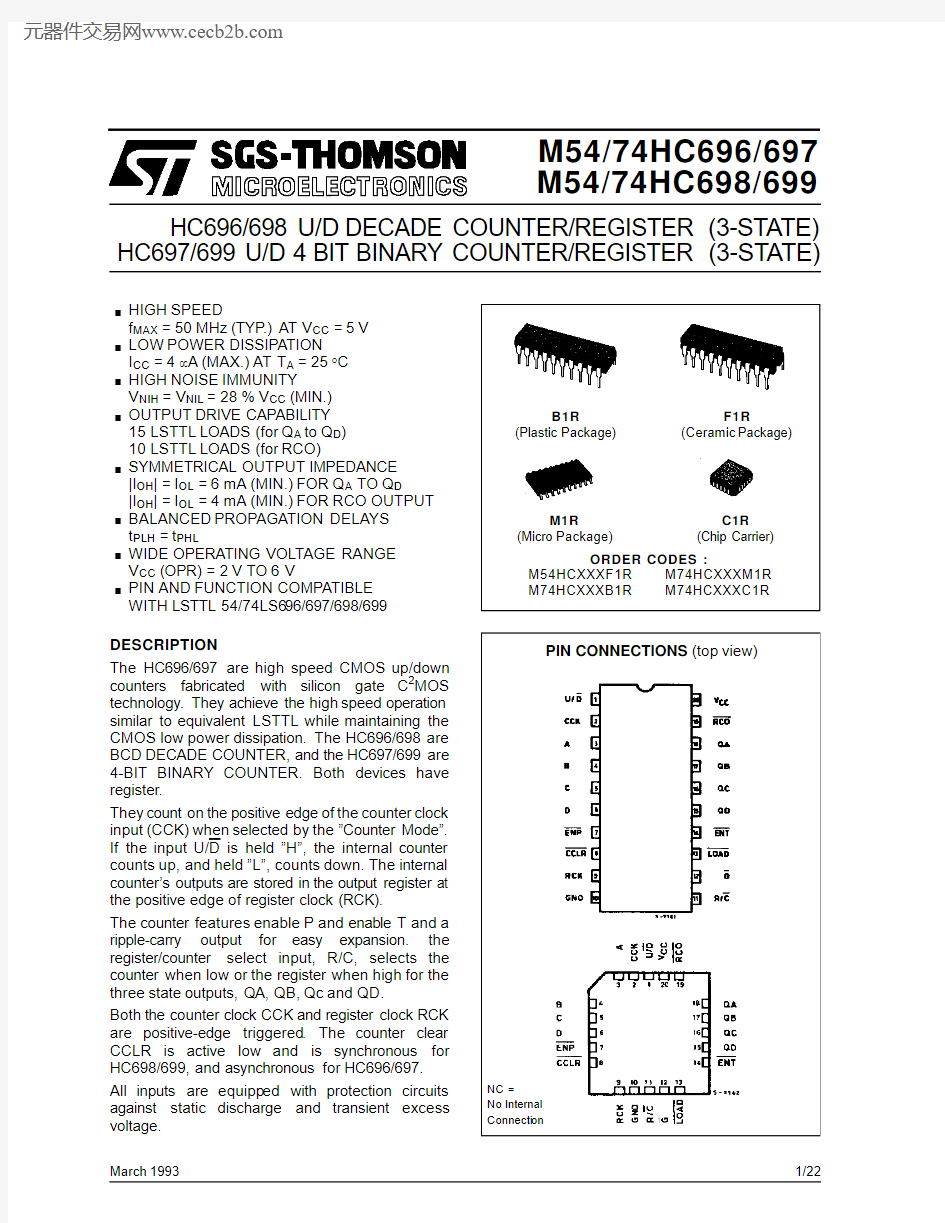

HC697/699U/D 4BIT BINARY COUNTER/REGISTER (3-STATE)

HC696/698U/D DECADE COUNTER/REGISTER (3-STATE)B1R

(Plastic Package)ORDER CODES :

M54HCXXXF1R M74HCXXXM1R M74HCXXXB1R M74HCXXXC1R

F1R

(Ceramic Package)

M1R

(Micro Package)C1R (Chip Carrier)

PIN CONNECTIONS (top view)

NC =

No Internal Connecti o n

.HIGH SPEED

f MAX =50MHz (TYP.)AT V CC =5V .LOW POWER DISSIPATION I CC =4μA (MAX.)AT T A =25°C .HIGH NOISE IMMUNITY

V NIH =V NIL =28%V CC (MIN.).OUTPUT DRIVE CAPABILITY 15LSTTL LOADS (for Q A to Q D )10LSTTL LOADS (for RCO)

.SYMMETRICAL OUTPUT IMPEDANCE |I OH |=I OL =6mA (MIN.)FOR Q A TO Q D

|I OH |=I OL =4mA (MIN.)FOR RCO OUTPUT .BALANCED PROPAGATION DELAYS t PLH =t PHL

.WIDE OPERATING VOLTAGE RANGE V CC (OPR)=2V TO 6V

.

PIN AND FUNCTION COMPATIBLE WITH LSTTL 54/74LS696/697/698/699

DESCRIPTION

The HC696/697are high speed CMOS up/down counters fabricated with silicon gate C 2MOS technology.They achieve the high speed operation similar to equivalent LSTTL while maintaining the CMOS low power dissipation.The HC696/698are BCD DECADE COUNTER,and the HC697/699are 4-BIT BINARY COUNTER.Both devices have register.

They count on the positive edge of the counter clock input (CCK)when selected by the ”Counter Mode”.If the input U/D is held ”H”,the internal counter counts up,and held ”L”,counts down.The internal counter’s outputs are stored in the output register at the positive edge of register clock (RCK).

The counter features enable P and enable T and a ripple-carry output for easy expansion.the register/counter select input,R/C,selects the counter when low or the register when high for the three state outputs,QA,QB,Qc and QD.

Both the counter clock CCK and register clock RCK are positive-edge triggered .The counter clear CCLR is active low and is synchronous for HC698/699,and asynchronous for HC696/697.All inputs are equipp ed with protection circuits against static discharge and transient excess voltage.

1/22

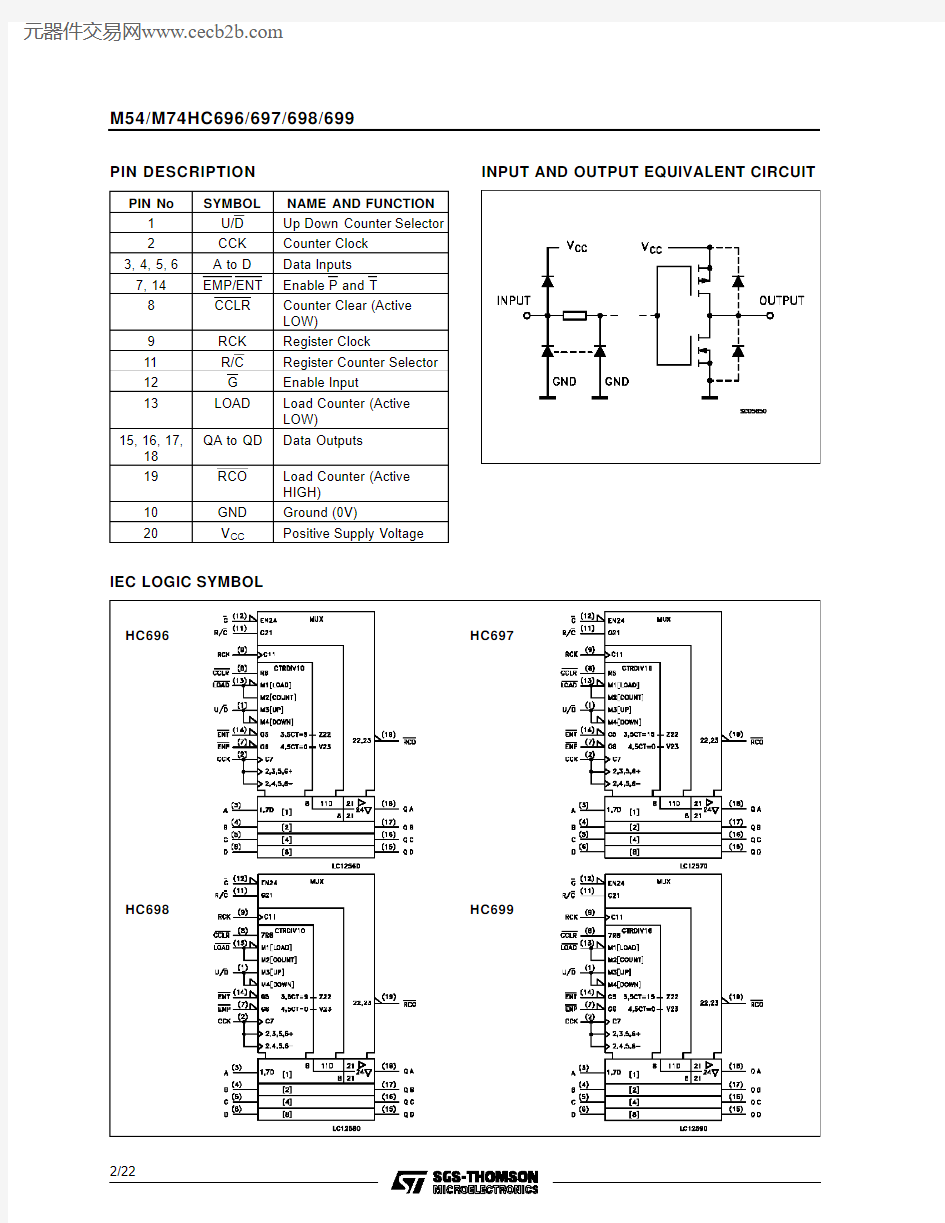

PIN DESCRIPTION

PIN No SYMBOL NAME AND FUNCTION 1U/D Up Down Counter Selector 2CCK Counter Clock 3,4,5,6A to D Data Inputs

7,14EMP/ENT Enable P and T

8CCLR Counter Clear (Active LOW)9RCK Register Clock

11R/C Register Counter Selector 12G Enable Input 13LOAD Load Counter (Active LOW)15,16,17,

18

QA to QD Data Outputs 19RCO Load Counter (Active HIGH)

10GND Ground (0V)

20

V CC

Positive Supply Voltage

INPUT AND OUTPUT EQUIVALENT CIRCUIT

IEC LOGIC SYMBOL

HC697

HC698HC699

HC696

M54/M74HC696/697/698/699

2/22

M54/M74HC696/697/698/699

TRUTH TABLE

INPUTS OUTPUTS

FUNCTION CCLR LOAD ENP ENT CCK U/D RCK R/C G QA QB QC QD X X X X X X X X H Z Z Z Z HIGH IMPEDANCE L X X X X(*)X X L L L L L L CLEAR COUNTER

H L X X X X L L a b c d LOAD COUNTER

H H H X X X L L NO CHANGE NO COUNT

H H X H X X L L NO CHANGE NO COUNT

H H L L H X L L COUNT UP COUNT UP

H H L L L X L L COUNT DOWN COUNT DOWN

H X X X X X L L NO CHANGE NO COUNT

X X X X X X H L a’b’c’d’LOAD REGISTER X X X X X X H L NO CHANGE NO LOAD (*):For HC698/699

X:Don’t care

Z:High impeda nce

a-d:The level of stead y state input at inputs a through D respect ively

a’-d’:The level of stead y state outputs at internal coun ter outputs QA’through QD’respe ctively

RCO function:HC696/8-RCO=(UP?QA?QD?ENT+UP?QA?QD?ENT)

HC697/9-RCO=(UP?QA?QB?QC?QD?ENT+UP?QA?QB?QC?QD?ENT)

BLOCK DIAGRAM

3/22

M54/M74HC696/697/698/699 LOGIC DIAGRAM(HC696)

4/22

M54/M74HC696/697/698/699 TIMING CHART(HC696)

5/22

M54/M74HC696/697/698/699 LOGIC DIAGRAM(HC697)

6/22

M54/M74HC696/697/698/699 TIMING CHART(HC697)

7/22

M54/M74HC696/697/698/699 LOGIC DIAGRAM(HC698)

8/22

M54/M74HC696/697/698/699 DECADE COUNTER,SYNCHRONOUS CLEAR(HC698)

9/22

M54/M74HC696/697/698/699 LOGIC DIAGRAM(HC699)

10/22

M54/M74HC696/697/698/699 BINARY COUNTER,SYNCHRONOUS CLEAR(HC699)

11/22

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit V CC Supply Voltage-0.5to+7V V I DC Input Voltage-0.5to V CC+0.5V V O DC Output Voltage-0.5to V CC+0.5V

I IK DC Input Diode Current±20mA

I OK DC Output Diode Current±20mA

I O DC Output Source Sink Current Per Output Pin(RCO)

(QA to QD)±25

±35

mA

I CC or I GND DC V CC or Ground Current±70mA

P D Power Dissipation500(*)mW T stg Storage Temperature-65to+150o C T L Lead Temperature(10sec)300o C Absolute Maximum Ratings are those values beyond whichdamage to the device may occu r.Functiona l ope ration und er these cond ition isnotimplied. (*)500mW:?65o C derate to300mW by10mW/o C:65o C to85o C

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Value Unit V CC Supply Voltage2to6V V I Input Voltage0to V CC V V O Output Voltage0to V CC V

T op Operating Temperature:M54HC Series

M74HC Series -55to+125

-40to+85

o C

o C

t r,t f Input Rise and Fall Time V CC=2V0to1000ns

V CC=4.5V0to500

V CC=6V0to400

M54/M74HC696/697/698/699

12/22

DC SPECIFICATIONS

Symbol Parameter

Test Conditions Value

Unit V CC

(V)

T A=25o C

54HC and74HC

-40to85o C

74HC

-55to125o C

54HC

Min.Typ.Max.Min.Max.Min.Max.

V IH High Level Input

Voltage 2.0 1.5 1.5 1.5

V 4.5 3.15 3.15 3.15

6.0 4.2 4.2 4.2

V IL Low Level Input

Voltage 2.00.50.50.5

V 4.5 1.35 1.35 1.35

6.0 1.8 1.8 1.8

V OH High Level

Output Voltage

(RCO)2.0

V I=

V IH

or

V IL

I O=-20μA

1.9

2.0 1.9 1.9

V 4.5 4.4 4.5 4.4 4.4

6.0 5.9 6.0 5.9 5.9

4.5I O=-4.0mA 4.18 4.31 4.13 4.10

6.0I O=-5.2mA 5.68 5.8 5.63 5.60

V OH High Level

Output Voltage

(QA-QD)2.0

V I=

V IH

or

V IL

I O=-20μA

1.9

2.0 1.9 1.9

V 4.5 4.4 4.5 4.4 4.4

6.0 5.9 6.0 5.9 5.9

4.5I O=-6.0mA 4.18 4.31 4.13 4.10

6.0I O=-

7.8mA 5.68 5.8 5.63 5.60

V OL Low Level Output

Voltage

(RCO)2.0

V I=

V IH

or

V IL

I O=20μA

0.00.10.10.1

V 4.50.00.10.10.1

6.00.00.10.10.1

4.5I O=4.0mA0.170.260.330.40

6.0I O=5.2mA0.180.260.330.40

V OL Low Level Output

Voltage

(QA-QD)2.0

V I=

V IH

or

V IL

I O=20μA

0.00.10.10.1

V 4.50.00.10.10.1

6.00.00.10.10.1

4.5I O=6.0mA0.170.260.330.40

6.0I O=

7.8mA0.180.260.330.40

I I Input Leakage

Current 6.0

V I=V CC or GND±0.1±1±1μA

I OZ3State Output

Off State Current 6.0

V I=V IH or V IL

V O=V CC or GND

±0.5±5±10μA

I CC Quiescent Supply

Current 6.0V I=V CC or GND44080μA

M54/M74HC696/697/698/699

13/22

AC ELECTRICAL CHARACTERISTICS(Input t r=t f=6ns)

Symbol Parameter

Test Conditions Value

Unit V CC

(V)

C L

(pF)

T A=25o C

54HC and74HC

-40to85o C

74HC

-55to125o C

54HC

Min.Typ.Max.Min.Max.Min.Max.

t TLH t THL Output Transition

Time

(Qn)

2.0

50

25607590

ns

4.57121918

6.06101315

t TLH t THL Output Transition

Time

(RCO)

2.0

50

307595115

ns

4.58151923

6.07131620

t PLH t PHL Propagation

Delay Time

(CCK-Q)

2.0

50

90215270325

ns

4.528435465

6.024374655

2.0

150

103245305370

ns

4.532496174

6.027425263

t PLH t PHL Propagation

Delay Time

(RCK-Q)

2.0

50

82185230280

ns

4.524374656

6.020313948

2.0

150

95215270325

ns

4.528435465

6.024374655

t PLH t PHL Propagation

Delay Time

(CCK-RCO)

2.0

50

109245305370

ns

4.532496174

6.027425263

t PLH t PHL Propagation

Delay Time

(R/C-Q)

2.0

50

61155195235

ns

4.520313947

6.017263340

2.0

150

73185230280

ns

4.524374656

6.020313948

t PLH t PHL Propagation

Delay Time

(ENT-RCO)

2.0

50

63140175210

ns

4.518283542

6.015243036

t PLH t PHL Propagation

Delay Time

(CCLR-Q)

2.0

50

for

HC696

HC697

78195245295

ns

4.526394959

6.022334250

2.0

150

90235295355

ns

4.530475971

6.026405060

t PLH t PHL Propagation

Delay Time

(CCLR-RCO)

2.0

50

for

HC696

HC697

98220275330

ns

4.529445566

6.025374756

f MAX Maximum Clock

Frequency 2.0

50

5124 3.4

MHz 4.525452017

6.030532420

M54/M74HC696/697/698/699 14/22

Symbol

Parameter

Test Conditions

Value

Unit

V CC (V)C L (pF)

T A =25o

C 54HC and 74HC -40to 85o C 74HC -55to 125o C

54HC Min.Typ.Max.

Min.Max.Min.Max.

t PZL t PZH Output Enable Time

2.050R L =1K ?

45120150180ns

4.5152430366.0132026312.0150R L =1K ?57150190225ns

4.5193038456.016263238t PLZ t PHZ Output Disable Time

2.050R L =1K ?32115145175ns

4.5172329356.014202530t W(H)t W(L)Minimum Pulse Width

(CCK,RCK) 2.050407595110ns

4.58

1519226.07131619t W(L)

Minimum Pulse Width (CCLR) 2.050for HC696HC697407595110ns

4.581519226.07131619t s

Minimum Set-up Time (CCLR) 2.050for HC698HC699

16506575ns

4.541013156.0391113t s

Minimum Set-up Time (LOAD,ENT,ENP) 2.05064150190220ns

4.5163038446.014263237t s

Minimum Set-up Time

(A,B,C,D) 2.05016506575ns

4.541013156.0391113t s

Minimum Set-up Time

(CCK,RCK) 2.05044100125150ns

4.5112025306.09172126t s

Minimum Set-up Time (U/D)

2.05044100125145ns

4.5112025296.09

172125t h

Minimum Hold Time

2.050

555ns

4.55556.0555t REM

Minimum

Removal Time 2.050for HC696HC697

555ns 4.55556.0

555C IN Input Capacitance 510

10

10

pF C PD (*)

Power Dissipation Capacitance

HC696/697/699

HC698

7177

pF

(*)C PD is defined as the value of the IC’s internal equivalent capac itanc e which is calculated from the operating current con sump tion without load.(Refer to Test Circuit).Average operting current can be obtained by the following equ ation.I CC (opr)=C PD ?V CC ?f IN +I CC /2(per circuit)

AC ELECTRICAL CHARACTERISTICS (Continued)

M54/M74HC696/697/698/699

15/22

M54/M74HC696/697/698/699

SWITCHING CHARACTERISTICS TEST WAVEFORM(HC696/697) 16/22

M54/M74HC696/697/698/699 SWITCHING CHARACTERISTICS TEST WAVEFORM(continued)

OUTPUT DISABLE,ENABLE

TEST CIRCUIT I CC(Opr.)

17/22

M54/M74HC696/697/698/699

Plastic DIP20(0.25)MECHANICAL DATA

mm inch DIM.

MIN.TYP.MAX.MIN.TYP.MAX.

a10.2540.010

B 1.39 1.650.0550.065

b0.450.018

b10.250.010

D25.4 1.000 E8.50.335

e 2.540.100

e322.860.900

F7.10.280

I 3.930.155

L 3.30.130

Z 1.340.053

P001J 18/22

M54/M74HC696/697/698/699 Ceramic DIP20MECHANICAL DATA

mm inch

DIM.

MIN.TYP.MAX.MIN.TYP.MAX.

A250.984

B7.80.307

D 3.30.130

E0.5 1.780.0200.070

e322.860.900

F 2.29 2.790.0900.110

G0.40.550.0160.022

I 1.27 1.520.0500.060

L0.220.310.0090.012

M0.51 1.270.0200.050

N14°(min.),15°(max.)

P7.98.130.3110.320

Q 5.710.225

P057H

19/22

M54/M74HC696/697/698/699

SO20MECHANICAL DATA

mm inch DIM.

MIN.TYP.MAX.MIN.TYP.MAX.

A 2.650.104

a10.100.200.0040.007 a2 2.450.096 b0.350.490.0130.019 b10.230.320.0090.012 C0.500.020

c145°(typ.)

D12.6013.000.4960.512 E10.0010.650.3930.419

e 1.270.050

e311.430.450

F7.407.600.2910.299 L0.50 1.270.190.050 M0.750.029 S8°(max.)

P013L 20/22