L293D接口简介

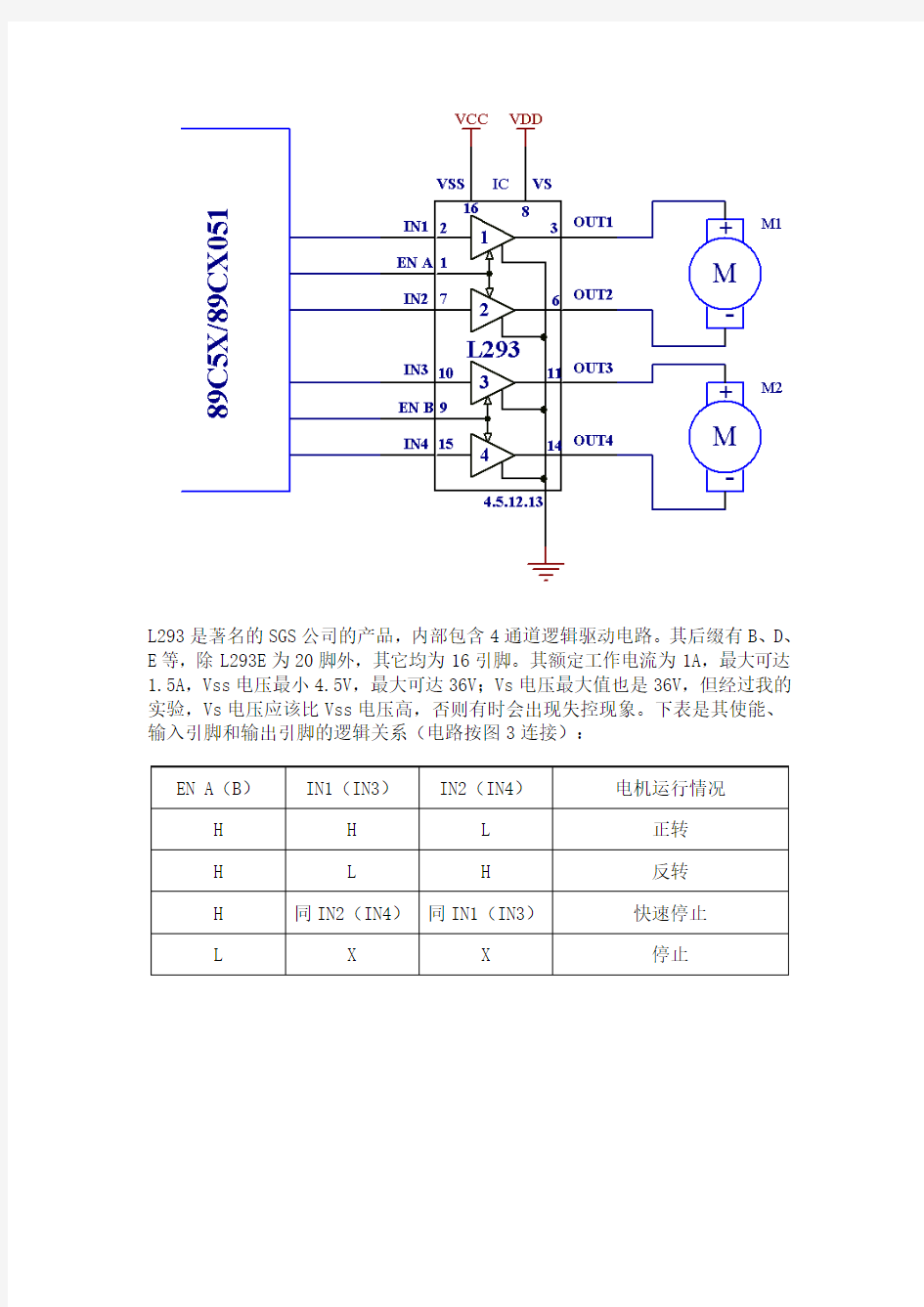

L293是著名的SGS公司的产品,内部包含4通道逻辑驱动电路。其后缀有B、D、E等,除L293E为20脚外,其它均为16引脚。其额定工作电流为1A,最大可达1.5A,Vss电压最小4.5V,最大可达36V;Vs电压最大值也是36V,但经过我的实验,Vs电压应该比Vss电压高,否则有时会出现失控现象。下表是其使能、

输入引脚和输出引脚的逻辑关系(电路按图3连接):

CAN总线接口

CAN总线接口 1.CAN模块简介 控制器局域网(CAN)模块是用于与其他外围设备或单片机 进行通信的模块,这种接口协议能在较大的噪声环境中进行通信,具有良好的扰干扰性能。 CAN模块是一个通信控制器,执行的是Bosch公司的CAN2.0A/B协议。它能支持CAN1.2、CAN 2.0A、CAN 2.OB 协议的旧版本和CAN2.OB现行版本,此控制器模块包含完整的CAN系统。 CAN模块由协议驱动和信息缓冲及控制组成,CAN协议驱动CAN总线 上接收和发送信息的所有功能。信息装载到某个相应的数据寄存器后再发送,通过读相应的寄存器可检查状态与错误信息。在CAN总线 上检测到的任何信息都要进行错误检查,然后与过滤器进行比较,判断是否被接收和存储到两个接收寄存器之一。 2.CAN模块支持的帧类型 CAN模块支持以下帧类型:标准数据帧、扩展数据帧、远程帧、出错帧、过载帧和空闲帧。 (1)数据帧。 用于各节点之间传送数据消息,由7个不同的位场组成:帧起始、仲裁场、控制场、数据场、CRC场、应答场和帧结束。数据帧结构如图1所示。 图1 数据帧组成

(2)远程帧。 当CAN网络上一个节点需要其他节点所拥有的数据信息时,可以通过发送远程帧来请求另一节点发送。该远程帧的标识符标识了所需数据的类型,因此,被送回的数据信息的标识符和远程帧的标识符完全一致。数据源节点在接收到远程帧后,根据远程帧的标识符判断所需数据信`患类型,并在总线空闲时将相应数据送出。远程帧由6个位场组成:帧起始、仲裁场、控制场、CRC场、应答场和帧结束。除了没有数据场和RTR为隐性外,远程帧结构和数据帧完全相同,远程帧结构如图2所示。 图2 远程帧结构 (3)错误帧。 为进行错误界定,每个CAN控制器均设有两个错误计数器 :发送错误计数器 (te C)和接收错误计数器(REC)。CAN总线上的所有节点按其错误计数器数值情况可分为3个状态:错误活动状态、错误认可状态和总线关闭状态。节点状态转换如图3所示。

总线的接口电路设计

PCI-Express总线的接口电路设计 王福泽 (天津工业大学) 一、 课题背景 计算机I/O技术在高性能计算发展中始终是一个关键技术。其技术特性决定 了计算机I/O的处理能力,进而决定了计算机的整体性能以及应用环境。从根本 上来说,无论现在还是将来,I/O技术都将制约着计算机技术的应用与发展,尤 其在高端计算领域。近年来随着高端计算市场的日益活跃,高性能I/O技术之争 也愈演愈烈。当计算机运算处理能力与总线数据传输速度的矛盾日益突出时,新 的总线技术便应运而生。在过去的十几年间,PCI(Peripheral component Interconnect)总线是成功的,它的平行总线执行机制现在看来依然具有很高的 先进性,但其带宽却早已露出疲态。PCI总线分有六种规格(表1所示),能提供133MBps到2131MBps的数据传输速率,而对于现有高性能产品例如万兆以太网 或者光纤通信,传统的PCI的数据传输速率早已入不敷出[4]。 表1 PCI总线六种规格 总线类型 总线形式 时钟频率 峰值带宽 每条总线上板卡插槽数 PCI32位 并行 33MHz 133MB/s 4-5 PCI32位 并行 66MHz 266MB/s 1-2 PCI-X 32位 并行 66MHz 266MB/s 4 PCI-X 32位 并行 133MHz 533MB/s 1-2 PCI-X 32位 并行 266MHz 1066MB/s 1 PCI-X 32位 并行 533MHz 2131MB/s 1 对于64位总线实现,上述所有带宽加倍 对于64位总线实现,上述所有带宽加倍仔细分析传统的PCI信号技术,可 发现并行式总线已逐渐走近其性能的极限,该种总线已经无法轻易地提升频率或 降低电压以提高数据传输率:其时钟和数据的同步传输方式受到信号偏移及PCB 布局的限制。高速串行总线的提出,成功的解决了这些问题,其代表应用就是PCI Express。PCI Express采用的串行方式,并且真正使用“电压差分传输” 即是两条信号线,以相互间的电压差作为逻辑“0”,“1”的表示,以此方式传输 可以将传输频率作极高的提升,使信号容易读取,噪声影响降低。由于是差分传输,所以每两条信号线才能单向传送1比特,即一根信号线为正、另一根信号线 为负,发送互为反相的信号,每一个“1比特”的两条信号线称为一个差分对。 按PCI Express技术规范规定,一个差分对的传输速率为2.5Gbps。实际使用中,

微机原理与接口技术部分复习题3(佳木斯大学)

〔习题1.1〕简答题 (1)计算机字长(Word)指的是什么? (2)总线信号分成哪三组信号? (3)PC机主存采用DRAM组成还是SRAM组成? (6)中断是什么? 〔解答〕 ①处理器每个单位时间可以处理的二进制数据位数称计算机字长。 ②总线信号分成三组,分别是数据总线、地址总线和控制总线。 ③ PC机主存采用DRAM组成。 ⑥中断是CPU正常执行程序的流程被某种原因打断、并暂时停止,转向执行事先安排好的一段处理程序,待该处理程序结束后仍返回被中断的指令继续执行的过程。 〔习题1.2〕判断题 (3)8086的数据总线为16位,也就是说8086的数据总线的个数、或说条数、位数是16。 (4)微机主存只要使用RAM芯片就可以了。 (5)处理器并不直接连接外设,而是通过I/O接口电路与外设连接。 ( 〔解答〕 ③对④错⑤对 〔习题1.3〕填空题 (2)Intel 8086支持___________容量主存空间,80486支持___________容量主存空间。 (3)二进制16位共有___________个编码组合,如果一位对应处理器一个地址信号,16位地址信号共能寻址___________容量主存空间。 〔解答〕 ② 1MB,4GB ③ 216,64KB 〔习题1.4〕说明微型计算机系统的硬件组成及各部分作用。 〔解答〕 CPU:CPU也称处理器,是微机的核心。它采用大规模集成电路芯片,芯片集成了控制器、运算器和若干高速存储单元(即寄存器)。处理器及其支持电路构成了微机系统的控制中心,对系统的各个部件进行统一的协调和控制。 存储器:存储器是存放程序和数据的部件。 外部设备:外部设备是指可与微机进行交互的输入(Input)设备和输出(Output)设备,也称I/O 设备。I/O设备通过I/O接口与主机连接。 总线:互连各个部件的共用通道,主要含数据总线、地址总线和控制总线信号。 〔习题1.7〕区别如下概念:助记符、汇编语言、汇编语言程序和汇编程序。 〔解答〕 助记符:人们采用便于记忆、并能描述指令功能的符号来表示机器指令操作码,该符号称为指令助记符。 汇编语言:用助记符表示的指令以及使用它们编写程序的规则就形成汇编语言。 汇编语言程序:用汇编语言书写的程序就是汇编语言程序,或称汇编语言源程序。 汇编程序:汇编语言源程序要翻译成机器语言程序才可以由处理器执行。这个翻译的过程称为“汇编”,完成汇编工作的程序就是汇编程序(Assembler)。

CAN总线应用电路

涡流量计CAN总线接口电路图 快速瓶劲识别-更好的负载测试方法 CAN总线是一种串行数据通信协议,在CAN总线通信接口中集成了CAN协议的物理层和数据链路层功能,可以完成对通信数据成帧处理。涡流量计CAN总线接口的具体电路如图1所示。 笔者用SJA1000作为流量计的CAN控制器,与CPU(单片机)的I/O口直接相连,再通过PCA82C250组成CAN总线。这种结构很容易实现CAN网络节点中的信息收发,从而实现对现场的控制。 SJA1000的AD0~AD7连接到MSP420F149的P0口,INT接到P1.0,/CS接到P1.1,/RD连接到P1.2,/WR连到P1.3,ALE连到P1.4,SJA1000的RX0与TX0分别通过两个高速光耦CNW137与PCA82C250相连后,连到CAN总线上。 PCA82C250为CAN总线收发器,是CAN控制器与CAN总线的接口器件,对CAN 总线差分方式发送,其RS引脚用于选择PCA82C250的工作方式:高速方式、斜率方式。

RS接地为高速,RS引脚串接一个电阻后再接地,用于控制上升和下降斜率,从而减小射频干扰。RS引脚接高电平,PCA82C250处于等待状态。此时,发送器关闭,接收器处于低电流工作,可以对CAN总线上的显性位做出反应,通知CPU。实验数据表明15~200K 为较理想的取值范围,在这种情况下,可以使用平行线或双绞线作总线,本文中PCA82C250的斜率电阻为取30K。 CNW137为高速光耦,最高速度为10Mbps,用于保护CAN总控制器SJA1000。CAN 总线的终端匹配电阻起相当重要的作用,不合适的电阻会使数据通信的抗干扰性及可靠性大大降低,甚至无法通信,范围为108~132Ω,本文使用的电阻为124Ω。 SJA1000的功能简介 CAN通信协议主要由CAN控制器完成。SJA1000是适用于汽车和一般工业环境控制器局域网(CAN)的高集成度独立控制器,具有完成高性能通信协议所要求的全部必要特性,具有简单总线连接的SJA1000可完成物理层和数据链路层的所有功能,应用层功能可由微控制器完成,SJA1000为其提供了一个多用途的接口。 SJA1000是一个独立的CAN控制器,它是Philips公司另一个CAN控制器PCA82C200的后继产品,在软件和引脚上均与PCA82C200兼容。但它不仅仅是PCA82C200的一个简单替代产品,它增加了许多新的功能,使得其性能更佳,尤其适用于对系统优化、诊断和维护要求比较高的场合。 SJA1000的功能框图如图2所示,由以下几部分构成:接口管理逻辑;发送缓冲器,能够存储1个完整的报文(扩展的或标准的);验收滤波器;接收FIFO;CAN核心模块。

7总线与接口

总线与接口部分 09-20.假设某系统总线在一个总线周期中并行传输4字节信息,一个总线周期占用2个时钟周期,总线时钟频率为10 MHz,则总线带宽是 A.10 MB/s B.20 MB/s C.40 MB/s D.80 MB/s 10-20.下列选项中的英文缩写均为总线标准的是 A.PCI、CRT、USB、EISA B.ISA、CPI、VESA、EISA C.ISA、SCSI、RAM、MIPS D.ISA、EISA、PCI、PCI-Express 11-20.在系统总线的数据线上,不可能传输的是 A.指令B.操作数C.握手(应答)信号D.中断类型号 12-19.某同步总线的时钟频率为100MHz,宽度为32位,地址/数据线复用,每传输一个地址或数据占用一个时钟周期。若该总线支持突发(猝发)传输方式,则一次“主存写”总线事务传输128位数据所需要的时间至少是()。 A.20ns B.40ns C.50ns D.80ns 12-20. 下列关于USB总线特性的描述中,错误的是()。 A.可实现外设的即插即用和热插拔 B.可通过级联方式连接多台外设 C.是一种通信总线,可连接不同外设 D.同时可传输2位数据,数据传输率高 12-21.下列选项中,在I/O总线的数据线上传输的信息包括()。 Ⅰ、I/O接口中的命令字Ⅱ、I/O接口中的状态字Ⅲ、中断类型号 A. 仅Ⅰ、Ⅱ B. 仅Ⅰ、Ⅲ C. 仅Ⅱ、Ⅲ D.Ⅰ、Ⅱ、Ⅲ 13-19、下列选项中,用于设备和设备控制器(I/O接口)之间互连的接口标准是 PCI B、USB C、AGP D、PCI-Express 14-19. 某同步总线采用数据线和地址线复用方式。其中数据线有32根,总线时钟频率为66MHZ,每个时钟周期传送两次数据。(上升沿和下降沿各传送一次数据)该总线的最大数据传输率是(总线带宽):() A. 132MB/S B. 264 MB/S C.528 MB/S D. 1056 MB/S 14- 20.一次总线事务中,主设备只需给出一个首地址,从设备就能从首地址开始的若干连续单元中读出或写入多个数,这种总线事务方式称为() A. 并行传输 B.串行传输 C.突发传输 D.同步传输 14-21.下列有关I/O借口的叙述中错误的是: A.状态端口和控制端口可以合用同一寄存器 B. I/O接口中CPU可访问寄存器,称为I/O端口 C.采用独立编址方式时,I/O端口地址和主存地址可能相同 D.采用统一编址方式时,CPU不能用访存指令访问I/O端口 15-19.下列有关总线定时的叙述中,错误的是() A.异步通信方式中,全互锁协议最慢 B.异步通信方式中,非互锁协议的可靠性最差 C.同步通信方式中,同步时钟信号可由多设备提供 D.半同步通信方式中,握手信号的采样由同步时钟控制 15-21.在采用中断I/O方式控制打印输出的情况下,CPU和打印控制接口中的I/O端口之间交换的信息不可能是( )

接口概念和总线技术

接口和总线 接口:是微型计算机的基本内容,是计算机与外部交换信息的桥梁。 总线:是计算机各种功能部件之间进行信息传输的公共通道。 微机接口 接口的基本概念 为了解决CPU和外设之间的速度差异以及外设各不相同的信息格式的问题,出现了带缓冲器的I/O装置,这里的缓冲器是指通过一个或几个单独的寄存器,实现主机和外设之间的数据传送。这里的缓冲器被发展为功能更强的I/O接口电路。 总结:I/O接口是微处理器与“外部世界”之间的连接电路,是主机与外设之间数据的“转接站”,同时提供主机和外设之间传送数据所需的状态信息,并能接受和执行主机发来的各种控制命令。 接口的基本功能 接口的基本功能有:数据缓冲,提供联络信息,信号与信息格式的转换,设备选择,中断管理,可编程功能。 接口的基本结构 接口一方面数据总线、地址总线以及控制总线和CPU进行联系,另一方面同响应的外设连接。接口内部都包含一组寄存器,通常有数据输入寄存器、数据输出寄存器、状态寄存器和控制寄存器,有的接口还包含中断逻辑寄存器。 数据输入寄存器用于暂存外设送往主机的数据。 数据输出寄存器用于暂存主机送往外设的数据。 状态寄存器用于保存I/O接口的状态信息。 控制寄存器用于存放CPU发出的控制命令。 中断控制逻辑电路用于实现外设准备就绪时向CPU发出中断请求信号。 与接口传输数据的方式 主机与外设之间传输数据的方式一般有三种:程序控制方式,中断控制方式,DMA方式。 程序控制方式:是指在程序控制下进行数据传送,又分为无条件传输方式和程序查询传送方式。 中断控制方式:是指CPU在执行当前程序时,若出现了紧急事件,CPU必须终止现在

系统总线和具有基本输入输出功能的总线接口实验报告

实验报告 课程名称:计算机组成原理 实验项目名称:系统总线和具有基本输入输出功能的总线接口实验 一、实 验 目 的 1.理解总线的概念及其特性。 2.掌握控制总线的功能和应用。 二、实验设备与器件 PC 机一台,TD-CMA 实验系统一套。 三、实 验 原 理 由于存储器和输入、输出设备最终是要挂接到外部总线上,所以需要外部总线提供数据信号、地址信号以及控制信号。在该实验平台中,外部总线分为数据总线、地址总线、和控制总线,分别为外设提供上述信号。外部总线和CPU 内总线之间通过三态门连接,同时实现了内外总线的分离和对于数据流向的控制。地址总线可以为外部设备提供地址信号和片选信号。由地址总线的高位进行译码,系统的I/O 地址译码原理见图4-1-1(在地址总线单元)。由于使用A6、A7进行译码, I/O 地址空间被分为四个区,如表4-1-1所示: A1B1A2B2G1N G2N Y10N Y20N Y13N Y12N Y11N Y23N Y22N Y21N 74L S 139 G N D A6A7 IOY0IOY1IOY2IOY3 图4-1-1 I/O 地址译码原理图 表4-1-1 I/O 地址空间分配 为了实现对于MEM 和外设的读写操作,还需要一个读写控制逻辑,使得CPU 能控制MEM 和I/O 设备的读写,实验中的读写控制逻辑如图4-1-2所示,由于T3的参与,可以保证写脉宽与T3一致,T3由时序单元的TS3给出(时序单元的介绍见附录2)。IOM 用来选择是对I/O 设备还是对MEM 进行读写操作,IOM=1时对I/O 设备进行读写操作,IOM=0时对MEM 进行读写操作。RD=1时为读,WR=1时为写。

什么是计算机总线 总线和接口的区别

什么是计算机总线总线和接口的区别 什么是计算机总线这个和计算机主机的构造有关系,首先,我们都知道计算机的cpu由两个部分组成,一个是控制单元,另一个是算术逻辑单元,cpu的控制单元负责计算机各个组件的协调与沟通,什么是沟通?就是数据传输,比如输入设备将信息传输到主存储器中,主存储器将数据传输到cpu中,cpu计算结果输出到输出设备等等。而cpu 的算术逻辑主要是进行逻辑上的运作,判断等,比如加减乘除运算。cpu只负责运算和协调控制各个组件,那么它所需要的数据从哪里来呢?答案是从主存储器那里来,输入设备会将用户输入的数给cpu(这是Intel的构架,AMD直接将主存储器和cpu连接而不通过北桥),北桥通往cpu的总线,因为需要连接主存储器和显示适配器等,因此需要极高的速度,我们把这条总线称之为系统总线,总线一次能传输的数据一般是32bit和64bit两种,而这些连接北桥通往cpu的设备,又有一个用来衡量传输能力的标准,叫做外频,举个例子,如果外频是333MHz的话,就意味著这些连接北桥的设备,每秒进行3.33*10 次传输,计算机中还有一个被固定死的倍频,cpu的主频(及每秒运作多少次)=外频*倍频,据说这个概念是为了协调高速cpu与低速外部设备而设计的==。外部设备的每秒数据传输量=每秒传输多少次*总线宽度即可得之。 下面来说一下南桥,南桥和北桥一样,也是用来连接计算机设备的,主要是连接低速的网卡,USB设备,音频,硬盘等设备,连接这些设备也是由一条总线牵连,我们叫做I/O总线,至于PCI,PCI-Express是啥?我们就拿PCI-Express说事吧,PCI-Express就是总线接口,从主板表面上看,就是主存储器,显示适配器的插槽嘛,PCI-Express是新一代的总线接口,用来取代老式的PCI,AGP等,别小看这个东东,他影响着数据的传输速度哦,现在很多硬件都是往匹配PCI-Express方向发展,SATA是啥?和IDE插槽一样,是用来连接硬盘设备的,最后附上一张图: 总线和接口的区别CPU与外设设备、存储器的连接和数据交换都需要通过接口设备来实现,前者被称为I/O接口,后者称为储存器接口。存储器通常在CPU的同步控制下工作,

I2C总线接口电路设计..

FPGA与I2C总线器件接口电路设计 利用FPGA模拟I2C总线协议对I2C总线接口器件AT24C256 进行读写操作。利用按键输入读写命令和相应的地址、数据,对芯片进行读写操作,读写的数据用数码管显示。 一、I2C总线接口电路设计分析 1. I2C 总线协议 I2C 总线的两根通信线,一根是串行数据线SDA,另一根是串行时钟线SCL。多个符合I2C总线标准的器件都可以通过同一条I2C总线进行通信,而不需要额外的地址译码器。每个连接到总线上的器件都有一个唯一的地址作为识别的标志,都可以发送或接收数据。I2C 总线通信速率受主机控制,标准模式下可达100kbit/s。 一般具有I2C总线的器件其SDA、SCL引脚都为集电极(或漏极)开路结构。因此实际使用时,SDA 和SCL信号线必须加3~10K的上拉电阻。总线空闲时均保持高平。I2C总线接法如图1所示。 图1 I2C总线连接示意图 (1) I2C的主机和从机,发送器和接收器 产生I2C总线时钟信号和起始、停止控制信号的器件,称为主机,被主机寻址的器件称为从机。 任何将数据传送到I2C总线的器件称为发送器,任何从I2C总线接收数据的器件称为接收器。 主机和从机都可作为发送数据器件和接收数据器件。 (2) I2C 总线上数据的有效性: 时钟线SCL为高电平时,数据线SDA的任何电平变化将被看作总线的起始或停止信号; 在数据传送过程中,当时钟线SCL为高电平时,数据线SDA必须保持稳定状态,不允许有跳变;数据线SDA的状态只能在SCL低电平期间才能改变。即进行串行传送数据时,在SCL高电平期间传送位数据,低电平期间准备数据。 (3) 从机地址 I2C总线不需要额外的片选信号或地址译码。多个I2C总线接口器件可连接到一条I2C总线上,它们之间通过地址来区分。主机是主控制器件,只有一个主机的不需要地址。其它器件均为从机,均有器件地址,但必须保证同一条I2C总线上的器件地址不能重复。一般从机地址由7位地址位和1位读写位组成,地址位为高7位,读写位为最低位。读写位为0时,表示主机将向从机写入数据;读写位为1时,表示主机将要从从机读取数据。 (4) I2C 总线的通信时序

实验四 系统总线和具有基本输入输出功能的总线接口实验

山西大学计算机与信息技术学院 实验报告 为了实现对于MEM 和外设的读写操作,还需要一个读写控制逻辑,使得CPU 能控制MEM 的读写,实验中的读写控制逻辑如图 4-2 所示,由于 T3 的参与,可以保证写脉宽与 T3 时序单元的TS3 给出(时序单元的介绍见附录2)。IOM 用来选择是对I/O 设备还是对 MEM 作,IOM=1 时对 I/O 设备进行读写操作,IOM=0 时对 MEM 进行读写操作。RD=1 时为读,

④将R0 寄存器中的数用LED 数码管显示。 先将WR、RD、IOM 分别置为1、0、1,对OUT 单元进行写操作;再将K7 置为0,打开 R0 寄存器的输出;K6 置为 0,关闭 R0 寄存器的输入;LDAR 置为 0,不将数据总线的数打入地址寄存器。连续四次点击图形界面上的“单节拍运行”按扭,观察图形界面,在T3时刻完成对OUT 单元的写入操作。

三、实验总结: 1、存储器和输入、输出设备最终是要挂接到外部总线上,因此需要外部总线提供数据信 号以及控制信号。 2、外部总线和CPU 内总线之间通过三态门连接,同时实现了内外总线的分离和对于数据流向的控制。 而地址总线可以为外部设备提供地址信号和片选信号。 3.为了实现对于MEM 和外设的读写操作,还需要一个读写控制逻辑,使得CPU 能控制MEM和 I/O 读写 4、WR=0,RD=1,IOM=0时 E0 灭,表示存储器读功能信号有效。 WR=1,RD=0,IOM=0)连续按动开关ST,当指示灯显示为 T3 时刻时,E1 灭,表示存储器写功能信号有效。 WR=0,RD=1,IOM=1时,E2 灭,表示I/O 读功能信号有效。 WR=1,RD=0,IOM=1) 时,观察扩展单元数据指示灯,指示灯显示为T3 时刻时,E3 灭,表示功能信号有效。

单片机总线接口电路的设计

Yibin University EDA技术及应用期末设计报告 题目: 单片机总线接口电路的设计 专业: 电子信息科学与技术 2013 年 12月 19 日 摘要: 单片机具有性价比高,功能灵活,易于人机交换和良好的数据

处理能力等特点;FPGA具有高速,高可靠以及开发方便快捷规范等特点,以此两类器件相结合的电路结构在许多高性能仪器仪表和电子产品中被广泛运用。在目前的单片机与FPGA的接口电路实际设计中,重要的角色之一就是并串转换电路,并且在很多其它设计中是必不可少的,尤其是在数据量庞大的设计中,如果前级电路和后级电路直接通过并行传输数据,那么数据有多少位就得有多少根通信线,这必将导致通信的准确度的降低和通信成本的增加,当距离较长时这种方式更是不可采用的。这次设计是基于FPGA设计的51单片机与外围电路通信的并串转换电路,该转换电路在接到51单片发出的访问外部RAM 的时序时,自动接受并行数据,接受完毕后自动串行发送数据,并且产生输出时钟,提供给后级电路使用。该电路可以完成51单片机与串口外围电路的通信,扩展了51单片机的I/O端口,使得单片机可以带更多的负载。 关键字: (1)并串转换 (2)FPGA (3)VHDL (4)状态机 (5)单片机 目录

摘要------------------------------------------------------------------------2 关键字---------------------------------------------------------------------2 设计概述------------------------------------------------------------------4 总的系统框图------------------------------------------------------------4 设计思路------------------------------------------------------------------5 方案论证------------------------------------------------------------------5 设计程序------------------------------------------------------------------6 设计仿真图--------------------------------------------------------------16 仿真分析-----------------------------------------------------------------17 参考文献------------------------------------------------------------------17 设计概述: 本次设计用FPGA设计一个并串转换电路,完成的功能

总线接口电路基本知识

总线接口电路基本知识 RS-232、RS-422与RS-485标准: 一、RS-232、RS-422与RS-485的由来 RS-232、RS-422与RS-485都是串行数据接口标准,最初都是由电子工业协会(EIA)制订并发布的,RS-232在1962年发布,命名为EIA-232-E,作为工业标准,以保证不同厂家产品之间的兼容。RS-422由RS-232发展而来,它是为弥补RS-232之不足而提出的。为改进RS-232通信距离短、速率低的缺点,RS-422定义了一种平衡通信接口,将传输速率提高到10Mb/s,传输距离延长到4000英尺(速率低于100kb/s时),并允许在一条平衡总线上连接最多10个接收器。RS-422是一种单机发送、多机接收的单向、平衡传输规范,被命名为TIA/EIA-422-A标准。为扩展应用范围,EIA又于1983年在RS-422基础上制定了RS-485标准,增加了多点、双向通信能力,即允许多个发送器连接到同一条总线上,同时增加了发送器的驱动能力和冲突保护特性,扩展了总线共模范围,后命名为TIA/EIA-485-A标准。由于EIA提出的建议标准都是以“RS”作为前缀,所以在通讯工业领域,仍然习惯将上述标准以RS作前缀称谓。 RS-232、RS-422与RS-485标准只对接口的电气特性做出规定,而不涉及接插件、电缆或协议,在此基础上用户可以建立自己的高层通信协议。 二、RS-232串行接口标准 目前RS-232是PC机与通信工业中应用最广泛的一种串行接口。RS-232被定义为一种在低速率串行通讯中增加通讯距离的单端标准。RS-232采取不平衡传输方式,即所谓单端通讯,DB25各引脚定义参见图1,DB9的引脚定义参见图2。 图1 图2 典型的RS-232信号在正负电平之间摆动,在发送数据时,发送端驱动器输出正电平在+5~+15V,负电平在-5~-15V电平。当无数据传输时,线上为TTL,从开始传送数据到结束,线上电平从TTL电平到RS-232电平再返回TTL电平,见图3。接收器典型的工作电平在+3~+12V与-3~-12V。由于发送电平与接收电平的差仅为2V至3V左右,所以其共模抑制能力差,再加上双绞线上的分布电容,其传送距离最大为约15米,最高速率为20kb/s。RS-232是为点对点(即只用一对收、发设备)通讯而设计的,其驱动器负载为3~7kù。所以RS-232适合本地设备之间的通信。RS-232的所传输的数据格式约定为:信息起始位,数据块停止位,奇偶校验位和若干数据位。 图3

多功能车辆总线网络接口单元的实现

多功能车辆总线网络接口单元的实现 杜振环 李常贤 王宁会 (大连理工大学电气工程与应用电子技术系 大连 116023) 摘要:1999年1月,列车通讯网络TCN被IEC61375-1标准采纳。TCN由连接车辆的列车总线和连接单节车辆或车辆组的车载设备的车辆总线组成。为简化组装,试车以及子系统的重复使用,TCN将多功能车辆总路线MVB(Multifunction Vehicle Bus)规定为车辆总路线。不同设备能过MVB网络接口单元连接到MVB。本文主要论述了MVB 设备网络接口单元的设计与实现。 关键词:列车通讯网络 ;多功能车辆总线 Abstract :The TCN was adopted as the international standard IEC 61375 in 1999.1 .The TCN architecture addresses all relevant configurations found in rail vehicles. It comprises the train bus connecting the vehicles and the vehicle bus connecting the equipment aboard a vehicle or group of vehicles. To simplify assembly, commissioning, and subsystem reuse, the TCN architecture specifies the Multifunction Vehicle Bus (MVB) as a vehicle bus. Standard MVB interface is needed to connect various equipments to the vehicle bus. In this essay, design and realization of MVB device interface module are discussed. Key Words:Train Communication Network ; Multifunction Vehicle Bus 中图分类号:TN919 文献标识码:B 1 前言 随着嵌入式控制技术和现场总线技术的发展,现代列车的过程控制已从集中型的直接数字控制系统发展成为基于网络的分布式控制系统。基于分布式控制的MVB(多功能车辆总线)是IEC61375-1(1999)TCN(列车通信网络国际标准)的推荐方案,它与WTB(绞线式列车总线)构成的列车通讯总线具有实时性强、可靠性高的特点。列车车辆的现代化的发展趋势与可靠性、安全性、通讯实时性的要求使MVB逐渐成为下一代车辆的通讯总线标准。 目前TCN 标准在国外特别是欧洲已相当普及,国内也加紧了对这一标准中关键总线技术的研制。自主研发列车通信网络设备将具有很好的市场前景和重大的意义。 - 1 -

什么是总线接口

什么是总线接口 任何一个微处理器都要与一定数量的部件和外围设备连接,但如果将各部件和每一种外围设备都分别用一组线路与CPU直接连接,那么连线将会错综复杂,甚至难以实现。为了简化硬件电路设计、简化系统结构,常用一组线路,配置以适当的接口电路,与各部件和外围设备连接,这组共用的连接线路被称为总线。采用总线结构便于部件和设备的扩充,尤其制定了统一的总线标准则容易使不同设备间实现互连。 微机中总线一般有内部总线、系统总线和外部总线。内部总线是微机内部各外围芯片与处理器之间的总线,用于芯片一级的互连;而系统总线是微机中各插件板与系统板之间的总线,用于插件板一级的互连;外部总线则是微机和外部设备之间的总线,微机作为一种设备,通过该总线和其他设备进行信息与数据交换,它用于设备一级的互连。 另外,从广义上说,计算机通信方式可以分为并行通信和串行通信,相应的通信总线被称为并行总线和串行总线。并行通信速度快、实时性好,但由于占用的口线多,不适于小型化产品;而串行通信速率虽低,但在数据通信吞吐量不是很大的微处理电路中则显得更加简易、方便、灵活。串行通信一般可分为异步模式和同步模式。 随着微电子技术和计算机技术的发展,总线技术也在不断地发展和完善,而使计算机总线技术种类繁多,各具特色。下面仅对微机各类总线中目前比较流行的总线技术分别加以介绍。 一、内部总线 1.I2C总线 I2C(Inter-IC)总线10多年前由Philips公司推出,是近年来在微电子通信控制领域广泛采用的一种新型总线标准。它是同步通信的一种特殊形式,具有接口线少,控制方式简化,器件封装形式小,通信速率较高等优点。在主从通信中,可以有多个I2C总线器件同时接到I2C总线上,通过地址来识别通信对象。2.SPI总线 串行外围设备接口SPI(serial peripheral interface)总线技术是Motorola 公司推出的一种同步串行接口。Motorola公司生产的绝大多数MCU(微控制器)都配有SPI硬件接口,如68系列MCU。SPI总线是一种三线同步总线,因其硬

RS-485总线标准及几种常见的RS-485接口电路介绍

RS-485总线标准及几种常见的RS-485接口电路介绍 本文主要简单介绍RS-485总线标准,以及比较几种常见的RS-485电路,并重点介绍美国模拟器公司(ADI)最新量产的具备±15 kV ESD保护功能的完全集成式隔离数据收发器ADM2582E/ADM2587E,一个集成隔离DC/DC电源,适合用于多点传输线路上的高速通信应用的数据收发器。 1.引言 随着现代化社会生活的迅速发展,工业自动化的程度越来越高。在工业控制、电力通讯、智能仪表等领域中,也常常使用简便易用的串行通讯方式作为数据交换的手段。但是,在工业控制等环境中,常会有电气噪声干扰传输线路,使用RS-232通讯时经常因外界的电气干扰而导致信号传输错误;另外,RS-232通讯的最大传输距离在不增加缓冲器的情况下只可以达到15 米。为了解决上述问题, RS-485标准通常被用作为一种相对经济、具有相当高噪声抑制、相对高的传输速率、传输距离远、宽共模范围的通信平台。 RS-485标准采用平衡式发送,差分式接收的数据收发器来驱动总线。因为RS-485的远距离、多节点(256个)以及传输线成本低的特性,是EIA RS-485称为工业应用中数据传输的首选标准。ADI公司的ADM2582E/ADM2587E器件针对均衡的传输线路而设计,符合 ANSI/TIA/EIA RS-485-A-98和ISO 8482:1987(E)标准。它采用ADI公司的iCoupler?技术,在单个封装内集成了一个三通道隔离器、一个三态差分线路驱动器、一个差分输入接收机和一个isoPower DC/DC转换器。该器件采用5V或3.3V单电源供电,从而实现了完全隔离的RS-485解决方案。 2.RS-485 标准介绍 电子工业协会(EIA)于1983 年制订并发布RS-485标准,并经通讯工业协会(TIA)修订后命名为TIA/EIA-485-A,习惯地称之为RS-485标准。RS-485标准是为弥补RS-232通信距离短、速率低等缺点而产生的。RS-485标准只规定了平衡发送器和接收器的电特性,而没有规定接插件、传输电缆和应用层通信协议。RS-485标准数据信号采用差分传输方式(Differential Driver Mode),也称作平衡传输,RS-485标准的最大传输距离约为1219 米。通常,RS-485网络采用平衡双绞线作为传输媒体,平衡双绞线的长度与传输速率成反比。在这里尤为注意并不是所有的RS-485收发器都能够支持高达10Mbps的通讯速率。如果采用光电隔离方式,则通讯速率一般还会受到光电隔离器件响应速度的限制。

RS232与PROFIBUS现场总线接口单元

RS232与PROFIBUS现场总线接口单元 1 序言 随着通信技术,计算机网络技术在工业生产过程中的不断推广和应用,工业控制过程对现场信号的采集、传输和数据转换提出了更新更高的要求,现有的DCS 系统和PLC 系统已经不能满足这些要求。由于数字通信技术、网络技术和微处理器技术的迅猛发展,把传统的数字信号和模拟信号混合的系统变成全数字信号系统成为可能,现场总线就是在这种背景下产生的,并成为当前工业过程控制领域的焦点。PROFIBUS 是德国开发的一种现场总线标准,得到欧洲许多大设备制造商的支持,并在国际上得到越来越多的推广和应用。然而,在工业过程控制现场,原有设备大多只具有RS2 3 2 通信接口,因此,为了在原有设备的基础上实现现场分布式控制,必须开发RS232与PROFIBUS 现场总线的接口单元。本文详细论述了接口单元的硬件实现和软件结构。 2 PROFIBUS 现场总线的基本特性 PROFIBUS 现场总线具有物理层,数据链路层和应用层。它基于令牌协议加主从总线的介质存取方式,主站以主从方式与从站通信,各主站之间由令牌协议决定总线控制权,令牌协议的制定包含优先级、状态转移和令牌移交等技术问题。 PROFIBUS 现场总线的物理层遵循RS485 标准,数据传输速率为9. 6 ~50 0 k Baud, 传输最长距离为4800 m,最多可支持120个站点的可靠数据通信3 接口单元的主要功能特性接口单元的主要功能是使具有RS232接口的现场设备作为从站与PROFIBUS 现场总线连接,从而使各个不相容的现场设备实现开放互连通信,接口单元遵循PROFIBUS 的物理层,数据链路层和应用层标准,并给用户提供应用层接口。 3 接口单元的主要功能特性 接口单元的主要功能是使具有RS232接口的现场设备作为从站与PROFIBUS 现场总线连接,从而使各个不相容的现场设备实现开放互连通信, 接口单元遵循PROFIBUS 的物理层,数据链路层和应用层标准,并给用户提供应用层接口。 4 硬件实现 接口单元的硬件原理,接口单元的核心为intel 公司生产的16位微处理器80 C1 96,主频为12 MHz; 用82 51 USART 和MAX2 3 2 发送/ 接收器产生RS232接口,并用751 76 光电耦合发送/ 接收器产生与PROFIBUS 现场总线相连的RS485 接口,考虑到标准PROFIBUS 的传输速率,微处理器外部时钟输入通过82 54 定时器接入8MHz 的外部时钟; 时钟例行程从64K 的EPROM装入16K的RAM 。从站接口单元用一片2K的ZPRAM 来存储通信参数设置,比如总线参数,通信关系表和重要事件等。参数的设置可以由PC 机或便携式电脑通过RS2 3 2 接口来实现。在参数设置期间,使用跨接线关闭PROFIBUS/ RS2 3 2 运行方式, 从站和PROFIBUS 的状态可以分别由一个两位数字显示器和一个LED来实现。 5 从站接口单元的软件结构 在上述硬件的基础上,我们就可以着手开发从站单元的软件,这里必须申明,上述的硬件结构同样支持主站,从站接口单元软件包除包含PROFIBUS现场总线的物理层、链路层和应用层外,还包括应用层接口。整个软件包由以下 3 个模块组成。 n 物理层, 链路层和应用层的协议软件; n 初始化设定, 事件记录和显示模块; n 应用层接口模块。 下面对每个模块的功能与结构予以阐述。

CAN总线接口电路设计注意事项(精)

CAN总线接口电路设计注意事项收藏 CAN 总线是一种有效支持分布式控制和实时控制的串行通信网络,以其高性能和高可靠性在自动控制领域得到了广泛的应用。为提高系统的驱动能力,增大通信距离,实际应用中多采用Philips公司的82C250作为CAN控制器与物理总线间的接口,即CAN收发器,以增强对总线的差动发送能力和对CAN控制器的差动接收能力。为进一步增强抗干扰能力,往往在CAN 控制器与收发器之间设置光电隔离电路。典型的CAN总线接口电路原理如图1所示。 图1 典型的CAN总线接口电路原理图 1 接口电路设计中的关键问题 1.1 光电隔离电路 光电隔离电路虽然能增强系统的抗干扰能力,但也会增加CAN总线有效回路信号的传输延迟时间,导致通信速率或距离减少。 82C250等型号的CAN收发器本身具备瞬间抗干扰、降低射频干扰(RFI以及实现热防护的能力,其具有的电流限制电路还提供了对总线的进一步保护功能。因此,如果现场传输距离近、电磁干扰小,可以不采用光电隔离,以使系统达到最大的通信速率或距离,并且可以简化接口电路。如果现场环境需要光电隔离,应选用高速光电隔离器件,以减少CAN总线有效回路信号的传输延迟时间,如高速光电耦合器 6N137,传输延迟时间短,典型值仅为48 ns,已接近TTL电路传输延迟时间的水平。

1.2 电源隔离 光电隔离器件两侧所用电源Vdd与Vcc必须完全隔离,否则,光电隔离将失去应有的作用。电源的隔离可通过小功率DC/DC电源隔离模块实现,如外形尺寸为DIP-14标准脚位的5 V 双路隔离输出的小功率DC/DC模块。 1.3 上拉电阻 图1中的CAN收发器82C250的发送数据输入端TXD与光电耦合器6N137的输出端OUT相连,注意TXD必须同时接上拉电阻R3。一方面,R3保证6N137中的光敏三极管导通时输出低电平,截止时输出高电平;另一方面,这也是CAN 总线的要求。具体而言, 82C250的TXD端的状态决定着高、低电平CAN 电压输入/输出端CANH、CANL的状态(见表1。CAN总线规定,总线在空闲期间应呈隐性,即CAN 网络中节点的缺省状态是隐性,这要求82C25O的TXD端的缺省状态为逻辑1(高电平。为此,必须通过R3确保在不发送数据或出现异常情况时,TXD端的状态为逻辑1(高电平。 表1 TXD与CANH、CANL的关系表 TXD CANH电CANL电CAN总 状态平(V 平(V 线状态 1 2.5 2.5 隐性(逻辑1 0 3.5 1.5 显性(逻辑0 1.4 总线阻抗匹配 CAN总线的末端必须连接2个120Ω的电阻,它们对总线阻抗匹配有着重要的作用,不可省略。否则,将大大降低总线数据通信时的可靠性和抗干扰性,甚至有可能导致无法通信。

1总线接口单元BIU负责完成CPU与存储器或I

1总线接口单元BIU负责完成CPU与存储器或I/O设备之间的数据传送。执行单元EU 负责执行指令。 2指令队列是若干个寄存器的集合。存放BIU 预取回的指令。引入使得EU和BIU可并行工作,即BIU在读指令时不影响EU单元执行指令,EU单元可连续不断的直接从指令队列中取到要执行的指令代码,从而减少了CPU取指令而等待的时间,提高CPU利用率,提高整机运行速度。 3程序传送方式:直接在程序控制下进行数据的输入输出操作。A无条件:输入设备随时准备好向CPU提供数据,输出设备随时接受CPU送来的数据。B查询:执行指令前,先查询设备相应状态。中断传送方式:外设与CPU进行信息交换时,由外设向CPU发出请求信号,是CPU暂停正在执行的程序,转去执行数据的输入/输出操作,数据传送结束后CPU再继续执行被暂停的程序。DMA 传送方式:存储器与外设或存储器之间直接进行数据传送,过程中无需CPU介入。传送速度取决于存储器和外设的速度。 4中断定义:在CPU执行程序的过程中,出现了某种紧急或异常的事件,CPU需暂停正在执行的程序,转去处理该事件,并在处理完毕后并在断点处继续执行被暂停的程序。58259A:管理控制外部中断请求。中断优先级判定。提供中断类型号。屏蔽中断输入。6中断向量表是存放中断向量的一个特定区域,存放所有中断服务程序的入口地址,按中断类型号从小到大顺序存储对应的中断向量,256个。CPU响应中断时把中断类型号n乘以4得到对应地址4n。后把由此地址开始的两个低字节单元(4n,4n+1)的内容装入IP寄存器,再把两个高字节单元(4n+2,4n+3)内容装入CS寄存器。于是CPU 转入中断类型号为N的中断服务程序。 7看价格。根据自己的预算价格,选择适合该价格的电脑。看性能。根据自己需要的电脑性能,以合理的价格购买。主机部分:1,CPU。电脑的心脏,运算器控制器寄存器整列。核心数越多,性能越好;2,显卡、电脑的显示核心,用于处理图像数据。如果是游戏玩家或者图形工作者,需要独立显卡。如果进用来上网,可以不购买独立显卡;3,内存储器。存储程序或数据,用于CPU 和硬盘交换数据,进行临时存储。内存越大性能越好;4硬盘。计算机的所有文件均存储到此。硬盘越大,存储的文件越多;5主板。计算机的各部件安插在主板上协同工作;6电源。给各部件供电;7I/O接口,有若干专用寄存器和相应的控制逻辑电路,是CPU和I/O设备之间交换信息的媒介和桥梁8 AX累加器SP堆栈指针寄存器BX基址寄存器BP基址寄存器CX计数器SI源变址寄存器DX数据寄存器DI目的变址寄存器9 DATA SEGMENT DATA 1 DB xxxx MAX DW ? DATA ENDS CODE SEGMENT ASSUME CS:CODE DS:DATA START: MOV AX,DATA MOV DS,AX MOV CX,4 MOV SI,0 MOV AX,0 LOOP1:ADD AX,DATA[SI] INC SI LOOP LOOP1 MOV SUM,AX 相加 DIV 4 MOV PJ,AX 平均 START: MOV CX,3 DONE:MOV MAX,AL LEA SI,DATA1 LOOP LOOP2 MOV MAX,[SI] OVER:CODE ENDS INC SI END START LOOP2: MOV AL,[SI] INC SI MOV BL,MAX CMP AL,BL JNC DONE LOOP LOOP2 J MP OVER 响应:CPU在每条指令执行的最后一个时钟周期检测其中中断请求输入端,判断。若CPU收到,此时CPU内中断允许触发器为1,CPU执行完现指令。发出INTA信号响应。