DDS原理及AD9851电路设计、测试

DDS原理及AD9851电路设计、测试

鼎峰电子https://www.360docs.net/doc/c615369574.html,

一.DDS(Direct Digital Synthesis)直接频率合成技术概况 在频率合成(FS, Frequency Synthesis)领域中,常用的频率合成技术有模拟锁相环、数字锁相环、小数分频锁相环(fractional-N PLL Synthesis)等,直接数字合成(Direct Digital Synthesis-DDS)是近年来新的FS技术。单片集成的DDS产品是一种可代替锁相环的快速频率合成器件。DDS是产生高精度、快速变换频率、输出波形失真小的优先选用技术。DDS以稳定度高的参考时钟为参考源,通过精密的相位累加器和数字信号处理,通过高速D/A变换器产生所需的数字波形(通常是正弦波形),这个数字波经过一个模拟滤波器后,得到最终的模拟信号波形。如图2所示,通过高速DAC产生数字正弦数字波形,通过带通滤波器后得到一个对应的模拟正弦波信号,最后该模拟正弦波与一门限进行比较得到方波时钟信号。

DDS系统一个显著的特点就是在数字处理器的控制下能够精确而快速地处理频率和相位。除此之外,DDS的固有特性还包括:相当好的频率和相位分辨率(频率的可控范围达μHz级,相位控制小于0.09°),能够进行快速的信号变换(输出DAC的转换速率300百万次/秒)。这些特性使DDS在军事雷达和通信系统中应用日益广泛。

其实,以前DDS价格昂贵、功耗大(以前的功耗达Watt级)、DAC器件转换速率不高,应用受到限制,因此只用于高端设备和军事上。随着数字技术和半导体工业的发展,DDS芯片能集成包括高速DAC器件在内的部件,其功耗降低到mW级(AD9851在3.3v 时功耗为650mW),功能增加了,价格便宜。因此,DDS也获得广泛的应用:现代电子器件、通信技术、医学成像、无线、PCS/PCN系统、雷达、卫星通信。

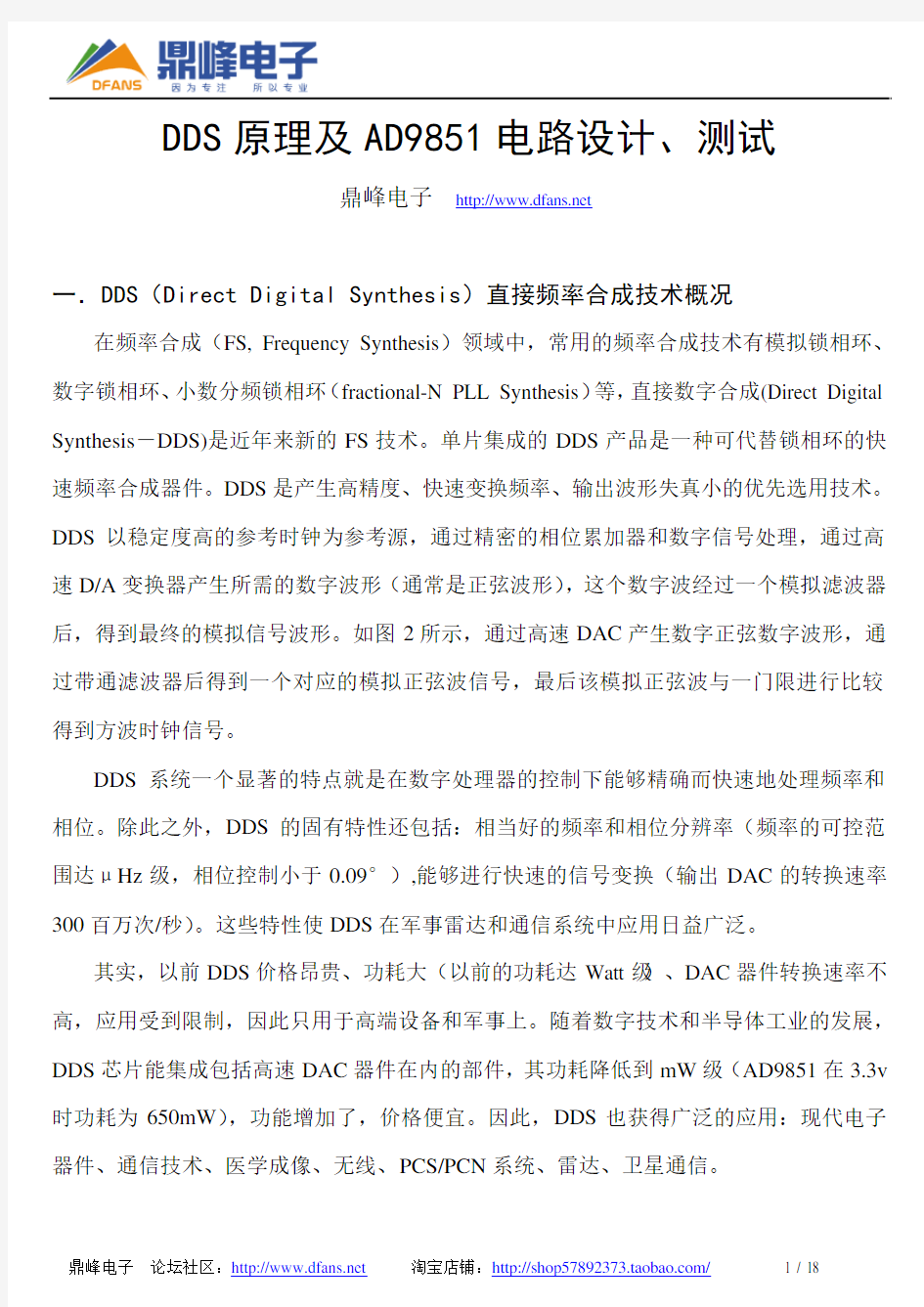

二.DDS工作原理:

图1

图1是一个DDS的基本内部结构。图中,U1是一个容量16字节,按照一维排列的8位只读存储器,U1的16个字节依次存放了完整的一个周期正弦波的量化数值n1-n16,相当于把一个正弦波0-2π的相位平分为16等份。我们把ROM中的n1-n16波形数据称作正弦查找表,A0-A15对应着正弦波的一个相位。当A0-A15地址选通线上某一位的电平为0时(同一时刻A0-A15中只能有一位为0电平),其对应ROM单元的存储值n将立即从D0-D7 8位总线输出。U2为4-16线译码器,负责把从B3-B0输入的4位二进制码转变为A0-A15的0电平状态。

U4 是一个高速数模转换器(DAC) ,他负责把D0-D7输入的数字信号变成对应的模拟信号,在基准时钟的驱动下,每个基准时钟周期转换一次。例如最大值n4对应模拟输

出5V,中间值n8输出2.5V,最小值n12对应输出0V。

ROM地址总线B0-B3, ROM地址选通线A0-A15以及ROM数据输出总线D0-D7的电平状态(逻辑关系)如下表:

U3为相位累加器,它是DDS的结构中最关键的算法单元。相位累加器有一个时钟输入端,一组频率控制字输入总线M3-M0,一组相位地址输出总线B3-B0。

相位累加器U3由N位加法器与N位累加寄存器级联构成。每来一个时钟脉冲F0,加法器将频率控制字M与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。此过程的伪代码表述如下:

If(clock)

B=B+M;

这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。用相位累

加器输出的数据B0-B3产生波形存储器(ROM)的相位取样地址A0-A15,这样就可把存储在波形存储器内的波形量化值(n,二进制编码)经查找表查出输出到数据总线D0-D7,完成相位到幅值转换。波形存储器的输出送到模数转换器DAC, DAC将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。

明白了DDS的工作过程后,我们可以假定几个工作状态来分析其工作过程。(假定基准时钟连续产生,频率为16Hz,B0-B3初始值为0000)

M=0时:B=B+0,则B一直保持恒定的值,意味着输出频率为0。

M=1时:B=B+1,B按1递增,依次将ROM中的n1-n16从D0-D7数据口输出。每2N =16个时钟,相位累加器溢出一次,从新开始累加。同时DAC输出一个完整的正弦波。此正弦波的频率为Fi/16=Fi/2N=1Hz。

M=2时:B=B+2,B按2递增,n1,n3,n5,n7……n15,依次从D0-D7数据口输出。每2N/2 =8个时钟,相位累加器溢出一次,从新开始累加。同时DAC输出两个完整的正弦波。此正弦波的频率为Fi*M/2N=2Hz。

查表的过程如下:

三.DDS相关计算

由上面的计算规律,我们可以总结出以下几个公式,各符号的定义为:Fi:基准频率;Fo:DDS输出频率;M:频率控制字;N:相位累加器位数;K:DDS每个输出周期的抽样点数;Fmin:DDS最小输出频率(频率分辨率);Fmax:DDS最大输出频率。

Fo=(M/2N)Fi (1)

Fmin=(1/2N)Fi (2)

Fmax= (Mmax/2N)Fi (3)

K=2N/M (4)

由此可以看出,当N比较大时,对于很大范围内的M值,DDS系统都可以在一个周期内输出足够的点,保证输出波形失真很小。上图中N和M相差不大,处于同一量级,导致抽样点数极少。从合成出的波形来看,M=3时已经不能很好复原出正弦波的样子。

四.DDS频率合成的特点

(1)输出频率相对带宽较宽

输出频率带宽为50%Fi(理论值)。但考虑到低通滤波器的特性和设计难度以及对输出信号杂散的抑制,实际的输出频率带宽仍能达到40%Fi。

(2)频率转换时间短

DDS是一个开环系统,无任何反馈环节,这种结构使得DDS的频率转换时间极短。事实上,在DDS的频率控制字改变之后,需经过一个时钟周期之后按照新的相位增量累加,才能实现频率的转换。因此,频率转换的时间等于频率控制字的传输时间,也就是一个时钟周期的时间。时钟频率越高,转换时间越短。DDS的频率转换时间可达纳秒数量级,比使用其它的频率合成方法都要短数个数量级。

(3)频率分辨率极高

若时钟Fi的频率不变,DDS的频率分辨率就由相位累加器的位数N决定。只要增加相位累加器的位数N即可获得任意小的频率分辨率。目前,大多数DDS的分辨率在1Hz 数量级,许多小于1mHz甚至更小。

(4)相位变化连续

改变DDS输出频率,实际上改变的每一个时钟周期的相位增量,相位函数的曲线是连续的,只是在改变频率的瞬间其频率发生了突变,因而保持了信号相位的连续性。(5)输出波形的灵活性

只要在DDS内部加上相应控制如调频控制FM、调相控制PM和调幅控制AM,即可以方便灵活地实现调频、调相和调幅功能,产生FSK、PSK、ASK和MSK等信号。另外,只要在DDS的波形存储器存放不同波形数据,就可以实现各种波形输出,如三角波、锯齿波和矩形波甚至是任意的波形。当DDS的波形存储器分别存放正弦和余弦函数表时,既可得到正交的两路输出。

(6)其他优点

由于DDS中几乎所有部件都属于数字电路,易于集成,功耗低、体积小、重量轻、可靠性高,且易于程控,使用相当灵活,因此性价比极高。

五.ADI公司常用的DDS芯片性能对比

六.AD9851简介

1.AD9851芯片是美国模拟器件公司采用先进DDS直接数字频率合成技术生产的高集成度产品。AD9851是在AD9850的基础上,做了一些改进以后生成的具有新功能的DDS芯片。AD9851相对于AD9850的内部结构,只是多了一个6倍参考时钟倍乘器,当系统时钟为180MHz时,在参考时钟输入端,只需输入30MHz的参考时钟即可。如图4(AD9851内部结构)所示,AD9851是由数据输入寄存器、频率/相位寄存器、具有6倍参考时钟倍乘器的DDS芯片、10位的模/数转换器、内部高速比较器这几个部分组成。其中具有6倍参考时钟倍乘器的DDS芯片是由32位相位累加器、正弦函数功能查找表、D/A变换器以及低通滤波器集成到一起。这个高速DDS芯片时钟频率可达180MHz,输出频率可达70 MHz,分辨率为0.04Hz。

AD9851可以产生一个频谱纯净、频率和相位都可编程控制且稳定性很好的模拟正弦波,这个正弦波能够直接作为基准信号源,或通过其内部高速比较器转换成标准方波输出,作为精密可编程时钟发生器来使用。

其引脚图如下:

AD9851的各引脚功能如下:

D0~D7:8位数据输入口,可给内部寄存器装入40位控制数据。

PGND:6倍参考时钟倍乘器地。

PVCC:6倍参考时钟倍乘器电源。

W-CLK:字装入信号,上升沿有效。

FQ-UD:频率更新控制信号,时钟上升沿确认输入数据有效。

FREFCLOCK:外部参考时钟输入。

CMOS/TTL 脉冲序列可直接或间接地加到6倍参考时钟倍乘器上。在直接方式中,输入频率即是系统时钟;在6倍参考时钟倍乘器方式,系统时钟为倍乘器输出。AGND:模拟地。

A VDD:模拟电源(+5V)。

DGND:数字地。

DVDD:数字电源(+5V)。

RSET:DAC外部参考电阻连接端。

VOUTN:内部比较器负向输出端。

VOUTP:内部比较器正向输出端。

VINN:内部比较器的负向输入端。

VINP:内部比较器的正向输入端。

DACBP:DAC旁路连接端。

IOUTB:“互补”DAC输出。

IOUT:内部DAC输出端。

RESET:复位端。低电平清除DDS累加器和相位延迟器为0Hz和0 相位,同时置数据输入为串行模式以及禁止6倍参考时钟倍乘器工作。

2.AD9851的寄存器位置和并行写入时序如下

AD9851的寄存器位置和串行写入时序如下

3.AD9851的基本运用原理如下(清晰版本见附件PDF文档)

4.电路基本原理说明:

J1为数据总线和控制线的引出端口,和外部MCU,MPU连接。

J4为有源晶振,为能充分利用AD9851的高时钟频率特性,晶振选用30.0000MHz。

C1-C8为电源退耦电容,滤除AD9851各部分(数字,模拟,PLL)电源的高频寄生干扰。

R1为AD9851内部DAC的参考电阻

R2,R3为“跷跷板分压器”两个电阻的节点处电压时钟为IOUT和IOUTB两个倒相的正弦信号电压的平均值,也就是节点电压高度始终处于正弦波的中点处。

C9为滤波电容,滤除R2,R3分压得到的中点电压,送往AD9851内部比较器反相输入端作为比较器参考电压。IOUT信号经过R7后直接送进比较器同相输入端。这样,比较器在DDS输出任何频率,任何幅度的时候,都能保证输出的方波占空比接近1:2.

L1,L2与周边的电容构成2阶椭圆低通滤波器,滤除1/2Fi以上的频率成分。使输出频谱更干净。

R4,R5,R6为DDS正弦输出的负载电阻。

J2,J3分别为正弦信号输出SMA插座和方波信号SMA输出插座。

5.AD9851PCB设计

在设计此类高频电路的时候,要注意良好接地,并避免走线角度过于尖锐,一般采用大面积覆铜来解决接地,散热和屏蔽的问题。

6.AD9851PCB单片机驱动设计

AD9851工作前必须对其进行初始化,AD9851上电后默认为并行通信方式,如需采用串行通信方式,上电后应将AD9851的D7~D0置为二进制数XXXXX011,紧接着依次往W_CLK和FQ_UD端输入宽度约1μS的高电平脉冲就可以使AD9851工作在串行模式下。

************A VR单片机驱动*********

//AVR并行驱动,数据输出口用PA口,控制线放在PC口//端口定义

#define clk 0

#define fq_ud1

#define rst 2

unsigned char phase_word=0x00; //相位控制字,使用低5位unsigned char power_down=0x00; //低功耗模式

unsigned char mult=0x01; //6倍频是否打开unsigned char ww[5]={0x09,0x0E,0x38,0xE3,0x8E};

unsigned long freq,set_value;

//往AD9851写数据

void write_dds(unsigned long dds)

{

unsigned char i;

ww[0]=0x01; //开启6倍频功能

ww[0]= (phase_word<<3)|| power_down<<2 || mult;

ww[1]=dds>>24; //频率字最高字节

ww[2]=(dds>>16)&0xFF;

ww[3]=(dds>>8)&0xFF;

ww[4]=dds&0xFF; //频率字最低字节

PORTC&=~(1< PORTC&=~(1< for(i=0;i<5;i++) //送入5个字节的控制字 { PORTA=ww[i]; delay_us(2); PORTC|=(1< delay_us(2); PORTC&=~(1< delay_us(2); } PORTC|=(1< delay_us(3); PORTC&=~(1< } //写入频率 void write_freq(unsigned long freq) { unsigned long dds; dds=23.860929422*freq; //频率字计算,可进行微调 write_dds(dds); } void init_dds(void) { PORTC|=(1< delay_us(10000); //延时10mS PORTC&=~(1< delay_us(10000); //延时10mS } //51并行驱动,数据输出口用PA口,控制线放在PC口//端口定义 sbit clk =P2^0; sbit fq_ud =P2^1; sbit rst =P2^2; unsigned char phase_word=0x00; //相位控制字,使用低5位unsigned char power_down=0x00; //低功耗模式 unsigned char mult=0x01; //6倍频是否打开unsigned char ww[5]={0x09,0x0E,0x38,0xE3,0x8E}; unsigned long freq,set_value; //往AD9851写数据 void write_dds(unsigned long dds) { unsigned char i; //控制字 ww[0]= (phase_word<<3)|| power_down<<2 || mult; ww[1]=dds>>24; //频率字最高字节 ww[2]=(dds>>16)&0xFF; ww[3]=(dds>>8)&0xFF; ww[4]=dds&0xFF; //频率字最低字节 fq_ud=0; //FQ_UD置低 clk=0; //CLK置低 for(i=0;i<5;i++) //送入5个字节的控制字 { P0=ww[i]; delay_us(2); clk=1; delay_us(2); clk=0; delay_us(2); } fq_ud=1; //使能信号 delay_us(3); fq_ud=0; } //写入频率 void write_freq(unsigned long freq) { unsigned long dds; dds=23.860929422*freq; //频率字计算,可进行微调 write_dds(dds); } void init_dds(void) { rst=1; //高电平复位 delay_us(10000); //延时10mS rst=0; delay_us(10000); //延时10mS } //AVR串行驱动,数据输出口用PA口,控制线放在PC口//端口定义 #define clk 0 #define fq_ud1 #define rst 2 #define dat 3 unsigned char phase_word=0x00; //相位控制字,使用低5位unsigned char power_down=0x00; //低功耗模式 unsigned char mult=0x01; //6倍频是否打开unsigned char ww[5]={0x09,0x0E,0x38,0xE3,0x8E}; unsigned long freq,set_value; //AD9851初始化,在此之前请确认D0,D1和D2的电平状态void init_dds(void) { PORTC|=(1< delay_us(10000); //延时10mS PORTC&=~(1< delay_us(10000); //延时10mS PORTC&=~(1< PORTC&=~(1< delay_us(2); 七.实际测试 测试仪器泰克TDS2102B A VR最小系统板 这是制作出来的PCB 下面是AD9851模块设置输出不同频率的,波形和频率,频谱实测图: 可以看出,DDS的输出频率十分精确和稳定。在60MHz以下,波形比较完美,频谱比较干净。越接近1/2Fi,波形失真越严重,频谱的各次谐波逐渐增多。所以在实际使用的时候,尽量控制在30%Fi以内使用。 七.经验之谈 1.在3.3V供电时,内部时钟6倍频器工作不稳定 2.串行模式的时候,注意数据口的状态设置 3.可以通过修改程序中计算频率字算法dds=23.860929422*freq;中的23.860929422,来微调输出频率。 4.AD9851内部比较器的截止频率在30MHz左右,在10MHz以上,输出波形发生畸变。如果要用到更高频的方波,务必使用外部高速比较器。 5.DDS正弦输出的幅度随频率增高而下降。低频端约1Vpp,高频端约200mVpp。实际应用中应外加合适的宽带放大器。 欢迎大家光临https://www.360docs.net/doc/c615369574.html,鼎峰电子论坛 机械原理模拟试卷 一单向选择(每小题1分共10分) 1. 对心直动尖顶盘形凸轮机构的推程压力角超过了许用值时,可采用措施来解决。 (A 增大基圆半径 B 改为滚子推杆 C 改变凸轮转向) 2. 渐开线齿廓的形状取决于的大小。 (A 基圆 B 分度圆 C 节圆) 3. 斜齿圆柱齿轮的标准参数指的是上的参数。 (A 端面 B 法面 C 平面) 4. 加工渐开线齿轮时,刀具分度线与轮坯分度圆不相切,加工出来的齿轮称为齿轮。 (A 标准 B 变位 C 斜齿轮) 5. 若机构具有确定的运动,则其自由度原动件数。 ( A 大于 B 小于 C 等于) 6. 两齿轮的实际中心距与设计中心距略有偏差,则两轮传动比__ _____。 ( A 变大 B 变小 C 不变 ) 7.拟将曲柄摇杆机构改变为双曲柄机构,应取原机构的_____ __作机架。 ( A 曲柄 B 连杆 C 摇杆 ) 8. 行星轮系是指自由度。 ( A 为1的周转轮系 B 为1的定轴轮系 C 为2的周转轮系) 9. 若凸轮实际轮廓曲线出现尖点或交叉,可滚子半径。 ( A 增大 B 减小 C 不变) 10.平面连杆机构急回运动的相对程度,通常用来衡量。 ( A 极位夹角θ B 行程速比系数K C 压力角α) 二、填空题(每空1分共10分) 1. 标准渐开线直齿圆锥齿轮的标准模数和压力角定义在端。 2. 图(a),(b),(c)中,S为总质心,图中转子需静平衡,图中转子需动平衡。 3. 平面移动副自锁条件是,转动副自锁条件是。 4. 周期性速度波动和非周期性速度波动的调节方法分别为应用和。 5. 惰轮对并无影响,但却能改变从动轮的。 6. 平面连杆机构是否具有急回运动的关键是。 三、简答题(每小题6分共24分) 1. 什么是运动副、低副、高副?试各举一个例子。平面机构中若引入一个高副将带入几个约束?若引入一个低副将带入几个约束? 2.何谓曲柄?铰链四杆机构有曲柄存在的条件是什么?当以曲柄为主动件时,曲柄摇杆机构的最小传动角将可能出现在机构的什么位置? 3.什么是渐开线齿廓的根切现象?产生根切原因是什么?标准直齿圆柱齿轮不根切的最小齿数是多少? 4.如图所示平面四杆机构,试回答: (1) 该平面四杆机构的名称; (2) 此机构有无急回运动,为什么? (3) 此机构有无死点,在什么条件下出现死点; (4) 构件AB为主动件时,在什么位置有最小传动角。 四、计算题(共36分) 1. 图所示穿孔式计算机中升杆和计算卡停止机构,有箭头标记的为原动件,试判断此机构运动是否确定。(若有复合铰链、局部自由度、虚约束请指出来)(8分) 2. 在电动机驱动的剪床中,作用在剪床主轴上的阻力矩M r的变化规律如图所示,等效驱动力矩I H 一、实验名称:基于F P G A的D D S信号源设计 二、技术规范: 1.实验目标: 设计一个直接数字频率合成(DDS,Direct Digital Synthesis),DDS是一种新型的频率合成技术。DDS 技术是一种把一系列数字形式的信号通过DAC 转换成模拟信号的合成技术。 DDS 技术具有频率切换时间短,频率分辨率高,频率稳定度高,输出信号的频率和相位可以快速切换,输出相位可连续,并且在改变时能够保持相位的连续,很容易实现频率、相位和幅度的数字控制。它在相对带宽、频率转换时间、相位连续性、高分辨率以及集成化等一系列性能指标方面远远超过了传统频率合成技术。 因此在现代电子系统及设备的频率源设计中,尤其在通信领域,直接数字频率合成器的应用越来越广泛。 2.实现功能: 本实验最后将设计出一个具有频率控制和相位移控制功能的DDS。 3.引脚: 本实验有三个输入端口,8位的频率控制字端口,分别接8个开关按键,8位的相位控制字端口,分别接另外的8个开关按键,系统时钟输入端口;一个8位输出端口,接D/A的输入端口。FPGA板上的时钟频率为50MHz,本实验将其10分频后得到5MHz再使用。 三.总体设计方案; 原理: 实验采用目前使用最广泛的一种DDS 方式是利用高速存储器作查找表,然后通过高速DAC 输出已经用数字形式存储的波形。 图1:DDS 系统的基本原理图 图1中虚方框部分是DDS 的核心单元,它可以采用CPLD/FPGA 来实现。图中的相位累加器由N位全加器和N位累加寄存器级联而成,可对频率控制字的二进制码进行累加运算,是典型的反馈电路。 频率控制字M和相位控制字分别控制DDS 输出正(余)弦波的频率和相位。每来一个时钟脉冲,相位寄存器以步长M递增。相位寄存器的输出与相位控制字相加,其结果作为正(余)弦查找表的地址。正(余)弦查找表的数据存放在ROM中,内部存有一个周期的正弦波信号的数字幅度信息,每个查找表的地址对应于正弦波中0°~360°范围内的一个相位点。查找表把输入的址信息映射成正(余)弦波的数字幅度信号,同时输出到数模转换器DAC 的输入端,DAC输出的模拟信号经过低通滤波器(LPF),可得到一个频谱纯净的正(余)弦波。 DDS 具体工作过程如下:每来一个时钟脉冲clk,N 位全加器将频率控制数据M 与累加寄存器输出的累加相位数据N 相加,把相加后的结果送至累加寄存器的输入端。累加寄存器一方面将上一时钟周期作用后所产生的新的数据反馈到加法器的输入端,以使加法器在下一时钟的作用下继续与频率控制数据M 相加;另一方 DDS基本原理及技术指南 2012年03月20日12:03 eechina 分享 关键词:DDS , 频率合成 随着数字技术在仪器仪表和通信系统中的广泛使用,可从参考频率源产生多个频率的数字控制方法诞生了,即直接数字频率合成(DDS)。其基本架构如图1所示。该简化模型采用一个稳定时钟来驱动存储正弦波(或其它任意波形)一个或多个整数周期的可编程只读存储器(PROM)。随着地址计数器逐步执行每个存储器位置,每个位置相应的信号数字幅度会驱动DAC,进而产生模拟输出信号。最终模拟输出信号的频谱纯度主要取决于DAC。相位噪声主要来自参考时钟。 DDS是一种采样数据系统,因此必须考虑所有与采样相关的问题,包括量化噪声、混叠、滤波等。例如,DAC 输出频率的高阶谐波会折回奈奎斯特带宽,因而不可滤波,而基于PLL的合成器的高阶谐波则可以滤波。此外,还有其它几种因素需要考虑,稍后将会讨论。 图1:直接数字频率合成系统的基本原理 这种简单DDS系统的基本问题在于,最终输出频率只能通过改变参考时钟频率或对PROM重新编程来实现,非常不灵活。实际DDS系统采用更加灵活有效的方式来实现这一功能,即采用名为数控振荡器(NCO)的数字硬件。图2所示为该系统的框图。 图2:灵活的DDS系统 系统的核心是相位累加器,其内容会在每个时钟周期更新。相位累加器每次更新时,存储在△相位寄存器中的数字字M就会累加至相位寄存器中的数字。假设△相位寄存器中的数字为00...01,相位累加器中的初始内容为00...00。相位累加器每个时钟周期都会按00...01更新。如果累加器为32位宽,则在相位累加器返回至00...00前需要232(超过40亿)个时钟周期,周期会不断重复。 相位累加器的截断输出用作正弦(或余弦)查找表的地址。查找表中的每个地址均对应正弦波的从0°到360°的一个相位点。查找表包括一个完整正弦波周期的相应数字幅度信息。(实际上,只需要90°的数据,因为两个MSB中包含了正交数据)。因此,查找表可将相位累加器的相位信息映射至数字幅度字,进而驱动DAC。图3用图形化的“相位轮”显示了这一情况。 考虑n = 32,M = 1的情况。相位累加器会逐步执行232个可能的输出中的每一个,直至溢出并重新开始。相应的输出正弦波频率等于输入时钟频率232分频。若M=2,相位累加器寄存器就会以两倍的速度“滚动”计算,输出频率也会增加一倍。以上内容可总结如下: 图3:数字相位轮 1. 信号产生部分 1.1 频率控制字输入模块 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity ddsinput is port(a,b,c,clk,clr:in std_logic; q1,q2,q3,q4,q5:buffer unsigned(3 downto 0)); end ddsinput; architecture a of ddsinput is signal q:std_logic_vector(2 downto 0); begin q<=c&b&a; process(cp,q,clr) begin if clr='1'then q1<="0000";q2<="0000";q3<="0000";q4<="0000";q5<="0000"; elsif clk 'event and clk='1'then DDS信号信号发生器电路设计 case q is when"001"=>q1<=q1+1; when"010"=>q2<=q2+1; when"011"=>q3<=q3+1; when"100"=>q4<=q4+1; when"101"=>q5<=q5+1; when others=>NULL; end case; end if; end process; end a; 1.2 相位累加器模块 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity xiangwei is port(m:in std_logic_vector(19 downto 0); clk,clr:in std_logic; data:out std_logic_vector(23 downto 0)); end xiangwei; architecture a of xiangwei is signal q:std_logic_vector(23 downto 0); begin process(clr,clk,m,q) begin if clr='1'then q<="000000000000000000000000"; elsif (clk'event and clk='1')then q<=q+m; end if; data<=q; end process; end a; 电磁无损检测中信号发生器的设计与实 现 [日期:2005-6-24] 来源:国外电子元器件作者:彭国标 [字体:大中 小] 摘要:在电磁无损检测系统中,信号频率及其稳定性对检测效果影响很大,为了解决该难题,文中给出了一种应用DDS技术设计的新型信号发生器解决方案。该信号发生器具有频率精度高、稳定性好、分辨率高的特点,有利于提高电磁无损检测的效果。 关键词:电磁无损检测;信号发生器;直接数字频率合成 电磁无损检测(如涡流)是基于电磁感应原理的无损检测技术。当载有交变电流的检测线圈靠近导体时,由于交变电流在周围空间中会产生交变磁场,因而在被测试件(导体)表面产生趋肤效应并感应出交变电流。通过优化设计可使被测试件表面电流达到均匀分布,从而使周围磁场也达到均匀,而当被测试件表面有缺陷时,电流就会发生畸变,均匀磁场随之发生变化,这样,直接或间接测量出该磁场的变化,就能检测试件的缺陷。虽然人们在电磁无损检测方面已取得了许多进展,但仍有许多不尽人意之处,其中一个重要的因素便是检测系统信号的稳定性,这一点对测量结果会产生严重的影响。因为信号发生电路是整个检测系统的信号源,它的信号频率是否稳定将对整个检测系统的工作起十分关键的作用,信号频率不稳定会给信号的后续处理带来极大的困难,甚至使电磁检测难以进行。为了解决上述问题,笔者应用DDS技术设计了一个高稳定性信号发生器。 1DDS的工作原理 直接数字合成(DDS-DirectDigitalSynthesizer)是近几年发展起来的一种新的频率/波形合成技术。该技术具有频率分辨率高、转换速度快、信号纯度高、相位可控、输出信号无电流脉冲叠加、输出可平稳过渡且相位保持连续变化等优点。近年来在通讯、雷达、GPS、蜂窝基站、图像处理及HDTV等领域得到了广泛应用。 试题1 一、填空题(每小题2分,共20分) 1、 平面运动副的最大约束数为2个,最小约束数为 1个。 2、 当两构件组成转动副时,其相对速度瞬心在转动副中心处。 3、 对心曲柄滑块机构,若以连杆为机架,则该机构演化为曲柄摇块机构。 4、 传动角越大,则机构传力性能越好。 5、 凸轮机构推杆的常用运动规律中,二次多项式运动规律具有柔性冲击。 6、 蜗杆机构的标准参数从中间平面中取。 7、 常见间歇运动机构有:棘轮机构、槽轮机构等。 8、 为了减小飞轮的重量和尺寸,应将飞轮装在高速轴上。 9、 实现往复移动的机构有:曲柄滑块机构、凸轮机构等。 10、 外啮合平行轴斜齿轮的正确啮合条件为: 212121n n n n m m ααββ==-=,,。 二、简答题(每小题5分,共25分) 1、何谓三心定理? 答:三个彼此作平面运动的构件的三个瞬心必位于同一直线上。 2、 简述机械中不平衡惯性力的危害? 答:机械中的不平衡惯性力将在运动副中引起附加的动压力,这不仅会增大运动副中的摩擦和构件中的内应力,降低机械效率和使用寿命,而且会引起机械及其基础产生强迫振动。 3、 铰链四杆机构在死点位置时,推动力任意增大也不能使机构产生运动,这与机构的自锁 现象是否相同?试加以说明? 答:(1)不同。 (2)铰链四杆机构的死点指:传动角=0度时,主动件通过连杆作用于从动件上的力恰好通过其回转中心,而不能使从动件转动,出现了顶死现象。 死点本质:驱动力不产生转矩。 机械自锁指:机构的机构情况分析是可以运动的,但由于摩擦的存在,却会出现无论如何增大驱动力,也无法使其运动的现象。 自锁的本质是:驱动力引起的摩擦力大于等于驱动力的有效分力。 4、 棘轮机构与槽轮机构均可用来实现从动轴的单向间歇转动,但在具体的使用选择上,又 有什么不同? 答:棘轮机构常用于速度较低和载荷不大的场合,而且棘轮转动的角度可以改变。槽轮机构较棘轮机构工作平稳,但转角不能改变。 5、 简述齿廓啮合基本定律。 答:相互啮合传动的一对齿轮,在任一位置时的传动比,都与其连心线被其啮合齿廓在接触 2 基本原理 2.1 直接数字频率合成器 直接数字合成(Direct Digital Synthesis,简称DDS)技术是从相位概念出发,直接对参考正弦信号进行抽样,得到不同的相位,通过数字计算技术产生对应的电压幅度,最后滤波平滑输出所需频率。 2.1.1 DDS工作原理 下面,通过从相位出发的正弦函数产生描述DDS的概念。 图1表示了半径R为1的单位圆,半径R绕圆心旋转与X轴的正方向形成夹角θ(t),即相位角。 图1 单位圆表示正弦函数S= R sinθ(t) DDS的原理框图如图2所示。图中相位累加器可在每一个时钟周期来临时将频率控制字(FTW)所决定的相位增量M累加一次,如果记数大于2N,则自动溢出,而只保留后面的N位数字于累加器中[9]。 图2 DDS原理框图 DDS的数学模型可归结为:在每一个时钟周期T c 内,频率控制字M与N比特相位累加器累加一次,并同时对2N取模运算,得到的和(以N位二进制数表示)作为相位值,以二进制代码的形式去查询正弦函数表ROM,将相位信息转变成相应的数字量化正弦幅度值,ROM输出的数字正弦波序列再经数模转换器转变为阶梯模拟信号,最后通过低通滤波器平滑后得到一个纯净的正弦模拟信号。 由于ROM表的规模有限,相位累加器一般仅取高位作为寻址地址送入正弦查询表获得波形幅度值。正弦查询表中以二进制数形式存入用系统时钟对正弦信号进行采样所得的样值点,可见只需改变查询表内容就可实现不同的波形输出。 2.1.2 DDS的结构 DDS的基本结构包括相位累加器、正弦查询表(ROM)、数模转换器(DAC)和低通滤波器(LPF),其中从频率控制字到波形查询表实现由数字频率值输入生成相应频率的数字波形,其工作过程为: ⑴确定频率控制字M; ⑵在时钟脉冲f c 的控制下,该频率控制字累加至相位累加器生成实时数字相位值; ⑶将相位值寻址ROM转换成正弦表中相应的数字幅码。 模块DAC实现将数字幅度值高速且线性地转变为模拟幅度值,DDS产生的混叠干扰由DAC之后的低通滤波器滤除]7[。 ㈠相位累加器 相位累加器是DDS最基本的组成部分,用于实现相位的累加并存储其累加结果。 若当前相位累加器的值为Σ n ,经过一个时钟周期后变为Σ 1+ n ,则满足 Σ 1+ n =Σ n +M Σ n 为一等差数列,不难得出:Σ n =nM+Σ 其中Σ 为相位累加器的初始相位值。 ㈡正弦查询表(ROM) DDS查询表所存储的数据是每一个相位所对应的二进制数字正弦幅值,在每一个时钟周期内,相位累加器输出序列的高m位对其进行寻址,最后的输出为该相位相对应的二进制正弦幅值序列。 ㈢数模转换器(DAC) 数模转换器的作用是将数字形式的波形幅值转换成所要求合成频率的模拟形式 一、填空题(10 道小题,20 个空,每空1 分,共20 分) 1.平面运动副的最大约束数为,最小约束数为。 2.移动副的自锁条件是,转动副的自锁条件是。 93.969mm,3.已知一对渐开线直齿圆柱齿轮传动,其主动轮齿数z1= 20 ,基圆直径d b1= 从动轮齿数z2= 67 ,则从动轮的基圆直径d b2=。 4.正变位齿轮与标准齿轮比较,其分度圆齿厚,齿根高。 5.在凸轮机构推杆的四种常用运动规律中,运动规律有刚性冲击; 运动规律无冲击。 功之比,它反映了功在机械中的有效利用程6.机械效率等于输入功与 度。 7.刚性转子的动平衡条件是,。 8.在单销四槽外接槽轮机构中,已知主动拨盘的角速度为ω = π / 4 rad/s, 则在主动拨盘运动 一周的时间内,槽轮运动了秒,停歇了秒;槽轮机构的运动系数 为。 9.微动螺旋机构的两段螺纹的旋向应,两导程应。 10.当两构件组成转动副时,其速度瞬心在处,组成移动副时,其瞬心在处。 二、简答题(4 道小题,每道小题5 分,共20 分) 1.何谓急回运动?试列出三种具有急回运动的连杆机构。 2.何谓周期性速度波动和非周期性速度波动?为什么要加以调节?各用什么办法来加以调节? 3.平底推杆凸轮机构的压力角为多少?这种凸轮机构是否存在自锁现象?为什么? 4.设计直动推杆盘形凸轮机构的凸轮轮廓时,若机构的最大压力角超过了许用值,试问可采取 哪几种措施以减小最大压力角? 注:学生必须在答题纸上答题,否则没有成绩。第 1 页共 4 页 = 250mm,cm, 图三、1 ,而其他各杆的长度不变,则当分别以1、2、3 图三、2 分) 所示冲床机构的自由度,若存在局部自由度、复合铰链或虚约束,请指出其 注:学生必须在答题纸上答题,否则没有成绩。第 2 页共 4 页 DDS详细设计方案 1.DDS简介: DDS同DSP(数字信号处理)一样,是一项关键的数字化技术。DDS 是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。 一块DDS芯片中主要包括频率控制寄存器、高速相位累加器和正弦计算器三个部分(如Q2220)。频率控制寄存器可以串行或并行的方式装载并寄存用户输入的频率控制码;而相位累加器根据频率控制码在每个时钟周期内进行相位累加,得到一个相位值;正弦计算器则对该相位值计算数字化正弦波幅度(芯片一般通过查表得到)。DDS芯片输出的一般是数字化的正弦波,因此还需经过高速D/A转换器和低通滤波器才能得到一个可用的模拟频率信号。 2.DDS规格: Xxx 3.实现原理 DDS的核心部分是相位累加器,相位累加器有一个累加器和相位寄存器组成,它的作用是再基准时钟源的作用下进行线性累加,当产生溢出时便完成一个周期,即DDS的一个频率周期。其中频率字的位宽为K位,作为累加器的一个输入,累加器的另一个输入端位宽为N位(N>K),每来一个时钟,频率字与累加器的另一个输入相加的结果存入相位寄存器,再反馈给累加器,这相当于每来一个时钟,相位寄存器的输出就累加一次,累加的时间间隔为频率字的时间,输入加法器的位宽为(N-K)位,它与同样宽度的相位控制字相加形成新的相位,并以此作为查找表的地址。每当累加器的值溢出一次,输入加法器的值就加一,相应的,作为查找表的地址就加一,而查找表的地址中保存波形的幅度值,这些离散的幅度值经DAC和PLF便课还原为模拟波形。 DDS原理及AD9851电路设计、测试 鼎峰电子https://www.360docs.net/doc/c615369574.html, 一.DDS(Direct Digital Synthesis)直接频率合成技术概况在频率合成(FS, Frequency Synthesis)领域中,常用的频率合成技术有模拟锁相环、数字锁相环、小数分频锁相环(fractional-N PLL Synthesis)等,直接数字合成(Direct Digital Synthesis-DDS)是近年来新的FS技术。单片集成的DDS产品是一种可代替锁相环的快速频率合成器件。DDS是产生高精度、快速变换频率、输出波形失真小的优先选用技术。DDS以稳定度高的参考时钟为参考源,通过精密的相位累加器和数字信号处理,通过高速D/A变换器产生所需的数字波形(通常是正弦波形),这个数字波经过一个模拟滤波器后,得到最终的模拟信号波形。如图2所示,通过高速DAC产生数字正弦数字波形,通过带通滤波器后得到一个对应的模拟正弦波信号,最后该模拟正弦波与一门限进行比较得到方波时钟信号。 DDS系统一个显著的特点就是在数字处理器的控制下能够精确而快速地处理频率和相位。除此之外,DDS的固有特性还包括:相当好的频率和相位分辨率(频率的可控范围达μHz级,相位控制小于0.09°),能够进行快速的信号变换(输出DAC的转换速率300百万次/秒)。这些特性使DDS在军事雷达和通信系统中应用日益广泛。 其实,以前DDS价格昂贵、功耗大(以前的功耗达Watt级)、DAC器件转换速率不高,应用受到限制,因此只用于高端设备和军事上。随着数字技术和半导体工业的发展,DDS芯片能集成包括高速DAC器件在内的部件,其功耗降低到mW级(AD9851在3.3v 时功耗为650mW),功能增加了,价格便宜。因此,DDS也获得广泛的应用:现代电子器件、通信技术、医学成像、无线、PCS/PCN系统、雷达、卫星通信。 《机械原理》试卷参考答案 开课单位:机械工程学院,考试形式:闭卷,允许带 计算器、绘图仪器 入场 题序 一 二 三 四 五 六 七 八 总 分 得分 评卷人 一、是非题(共10分,每小题2分,对者在括号内打“√”,错者打“×”)得分︳ 1、(× ) 当机构的自由度数小于机构的原动件数时,机构将具有确定的相对运动。 2、(√ ) 不论刚性转子上有多少个不平衡质量,也不论它们如何分布,只需在任意选定的两个平面内,分别 适当地加一平衡质量,即可达到动平衡。 3、(× ) 在其他参数不变的前提下,槽面摩擦较平面摩擦的摩擦力较大,是因为前者摩擦系数较大。 4、(√ ) 在移动副中,当驱动力作用线在摩擦锥之内,则发生自锁。 5、(√ ) 对于单自由度的机械系统,若选定等效构件为移动件时,其等效质量是按等效前后动能相等的条 件进行计算的。 二、填空题(共10分,每空1分)得分︳ 1、飞轮主要用以调节 周期性 速度波动,若不考虑其他因素,只为了减小飞轮尺寸和重量,应将其安装 在 高速 轴上。 2、刚性转子的静平衡就是要使 惯性力 之和为零;而刚性转子的动平衡则要使 惯性力 之和及 惯性力偶矩 之和均为零。 3、三个彼此作平面相对运动的构件共有 3 个瞬心,且必位于 同一直线 上。 4、在机构运动分析的速度多边形中,机架的速度影像是 极点 。速度影像和加速度影像原理只适用 于 同一构件 。 5、当机械的效率0≤η时,机构则发生 自锁 。 三、(共10分)计算图1所示机构的自由度,并判断机构的运动确定性,如机构中存在复合铰链、局部自由度和虚约束,请在图上示出。得分︳ 图1 虚约束 局部自由度 复合铰链 复合铰链 b) a) DDS的原理及镜像频谱分析 1.目的: (1)了解DDS的原理。 (2)分析DDS的镜像频谱 2.DDS的原理 2.1.DDS的概述 直接数字式频率综合器DDS(Direct Digital Synthesizer),实际上是一种分频器:通过编程频率控制字对系统时钟进行分频以产生所需要的频率。DDS 有两个突出的特点,一方面,DDS工作在数字域,一旦更新频率控制字,输出的频率就相应改变,其跳频速率高;另一方面,由于频率控制字的宽度宽(48bit或者更高),频率分辨率高。 图1是DDS的内部结构图,它主要分成3部分:相位累加器(PHASE_ACCMULATOR),相位幅度转换(AMPLITUDE/SINE_CONV.ALGORITHM),数模转换器(D/A_CONVERTER) 图1 DDS的结构框图 2.2.DDS的组成 1、相位累加器:一个正弦波,它的幅度不是线性的,但是它的相位却是线性增加的。DDS就是 利用了这一特点来产生正弦信号。如图 2,根据DDS的频率控制字的位数N,把 360°平均分成了2N等份。假设系统时钟为Fc,输出频率为Fout。每次转动一个 角度360°/2N,则可以产生一个频率为Fc/2N的正弦波的相位递增量。那么只要 选择恰当的频率控制字M,使得Fout/Fc= M/2N,就可以得到所需要的输出频率 Fout=Fc*M /2N。 图2 相位累加器原理 2、相位幅度转换:通过相位累加器,我们已经得到了合成Fout频率所对应的相位信息,然后相 位幅度转换器把0°~360°的相位转换成相位相应的幅度值。比如当DDS选 择为2Vp-p的输出时,45°对应的幅度值为 0.707V,这个数值则以二进制的 形式被送入DAC。这个相位到幅度的转换是通过查表完成的。 3、数模转换器:的二进制数字信号被送入DAC中,并转换成为模拟信号输出。★注意★DAC 的 位数并不影响输出频率的分辨率。输出频率的分辨率是由频率控制字的位数决 定的。 3. DDS的镜像频谱分析: 我们已经知道DDS是一个分频器,在提供一个系统主频的情况下,能够输出低于系统主频,分辨率为2N的正弦波。即每一个主频周期,DAC都会输出一个点,而2N/M个点形成输出频率的一个周期。这就相当于以系统时钟的频率对输出时钟进行采样,根据奈奎斯特定律,这就是为什么输出频率要低于系统时钟的50%的原因。 下图3为DDS在300M主频,输出80M频率时的频谱。图4为AD9954(主频为400M)输出80M 频率时的频谱(无参考时钟倍频器)。 试题1 一、选择题(每空2分,共10分) 1、平面机构中,从动件的运动规律取决于 D 。 A、从动件的尺寸 B、机构组成情况 C、原动件运动规律 D、原动件运动规律和机构的组成情况 2、一铰链四杆机构各杆长度分别为30mm ,60mm,80mm,100mm,当以30mm的杆为机架时,则该机构为 A 机构。 A、双摇杆 B、双曲柄 C、曲柄摇杆 D、不能构成四杆机构 3、凸轮机构中,当推杆运动规律采用 C 时,既无柔性冲击也无刚性冲击。 A、一次多项式运动规律 B、二次多项式运动规律 C、正弦加速运动规律 D、余弦加速运动规律 4、平面机构的平衡问题中,对“动不平衡”描述正确的是 B 。 A、只要在一个平衡面内增加或出去一个平衡质量即可获得平衡 B、动不平衡只有在转子运转的情况下才能表现出来 C、静不平衡针对轴尺寸较小的转子(转子轴向宽度b与其直径D之比b/D<0.2) D、使动不平衡转子的质心与回转轴心重合可实现平衡 5、渐开线齿轮齿廓形状决定于 D 。 A、模数 B、分度圆上压力角 C、齿数 D、前3项 二、填空题(每空2分,共20分) 1、两构件通过面接触而构成的运动副称为低副。 2、作相对运动的三个构件的三个瞬心必在同一条直线上。 3、转动副的自锁条件是驱动力臂≤摩擦圆半径。 4、斜齿轮传动与直齿轮传动比较的主要优点: 啮合性能好,重合度大,结构紧凑。 5、在周转轮系中,根据其自由度的数目进行分类:若其自由度为2,则称为差动轮系, 若其自由度为1,则称其为行星轮系。 6、装有行星轮的构件称为行星架(转臂或系杆)。 7、棘轮机构的典型结构中的组成有:摇杆、棘爪、棘轮等。 三、简答题(15分) 1、什么是构件? 答: 构件:机器中每一个独立的运动单元体称为一个构件;从运动角度讲是不可再分的单位体。 DDS设计实验报告实验名称:直接数字频率合成器 指导老师:花汉兵,姜萍 姓名:陈维兵 学号:114108000808 院系:能源与动力工程学院 目录 目录 (1) 摘要 (2) 正文 一、设计内容 (3) 二、设计原理 (3) 三、设计要求 (5) 四、设计思路以及部分电路图 (6) 五、实验感想 (16) 六、参考书目 (16) 摘要 本文介绍的是数字频率合成器(DDS)的设计以及其附加功能的拓展,附加功能有双通道显示、多波形显示、输出频率测量,另外,本文还介绍了一些在原有数字频率合成器的基础上做一些改进的想法和思路,虽然有的想法并没有实施,但是,作为一种参考也未尝不可。希望本文对读者有所帮助。 关键字:数字频率合成,附加功能,改进想法 Abstract The page introduces the design of the Direct Digital Frequency Synthesizer , which shorts for DDS , and other new more additions of it , the additions includes double-rows vision , wave-patterns vision , measuring of the output frequency , what’s more , this page introduces many more thoughts of improving the system which has been made ,even though the thoughts have not been applied , still they are good references for we and you .Wishing it helpful to you. Keywords: DDS ,addition of the system ,improving thoughts 2016-2017 学年第 二 学期 期末 考试试题 B 卷 第 1 页 共 6 页 考试科目:机械原理 考试时间:120分钟 试卷总分:100分 考试方式: 闭卷 考生院系: 机械工程学院 一、判断题(每题 2 分,共 10 分 1、两构件通过面接触而构成的运动副称为高副。 ( X ) 2、作相对运动的三个构件的三个瞬心必在同一条直线上。 ( √ ) 3、转动副的自锁条件是驱动力臂≤摩擦圆半径。 ( √ ) 4、渐开线的形状取决于基圆的大小。 ( √ ) 5、斜齿轮传动与直齿轮比较的主要优点是啮合性能好,重合度大,结构紧凑。( √ ) 二、选择题(每题 2 分,共 10 分) 1、平面机构中,从动件的运动规律取决于 D 。 A 、 从动件的尺寸 C 、机构组成情况 B 、 原动件运动规律 D 、原动件运动规律和机构的组成情况 2、一铰链四杆机构各杆长度分别为30mm ,60mm ,80mm ,100mm ,当以30mm 的杆为 机架时,则该机构为 A 机构。 A 、双摇杆 B 、双曲柄 C 、曲柄摇杆 D 、不能构成四杆机构 3、凸轮机构中,当推杆运动规律采用 B 时,既无柔性冲击也无刚性冲击。 A 、 一次多项式运动规律 C 、二次多项式运动规律 B 、 正弦加速运动规律 D 、余弦加速运动规律 4、平面机构的平衡问题中,对“动不平衡”描述正确的是 B 。 A 、 只要在一个平衡面内增加或出去一个平衡质量即可获得平衡 B 、 动不平衡只有在转子运转的情况下才能表现出来 C 、 静不平衡针对轴尺寸较小的转子(转子轴向宽度b 与其直径 D 之比b/D<0.2) D 、 使动不平衡转子的质心与回转轴心重合可实现平衡 5、渐开线齿轮齿廓形状决定于 D 。 A 、 模数 C 、分度圆上压力角 B 、 齿数 D 、前三项 三、简述题(每题 4 分,共 20 分) DDS 电路设计 摘要 本文介绍了DDS的原理,给出了用Altera Cyclone 1 EP1CQ240C8 FPGA芯片实现直接数字频率合成器的工作原理、设计思路、电路结 构和仿真结果以及频谱纯度分析。 关键词:直接数字频率合成(DDS);现场可编程门阵列(FPGA);相位累 加器 一、DDS原理概述 1、DDS在基本原理 框图如图所示。它主要由标准参考频率源、相位累加器、波形存储器、数/模转换器、 低通平滑滤波器等构成。其中,参考频率源一般是一个高稳定度的晶体振荡器,其输出信号 用于DDS中各部件同步工作。DDS的实质是对相位进行可控等间隔的采样。 为实现全数字化的频率可调的频率合成器,本系统基于FPGA采用Verilog HDL设计而 成直接数字频率合成器(DDS)。 系统由加法器、累加寄存器、波形存储器、D/A转换器、低通滤波器构成。在FPGA 里面做到的是D/A转换器之前的部分。 图一DDS原理图 DDS 系统的核心是相位累加器,它由一个N 位累加器与N 位相位寄存器构成。时钟脉冲每触发一次,累加器便将频率控制数据与相位寄存器输出的累加相位数据相加,然后把相加后的结果送至相位寄存器的数据输入端。相位寄存器将累加器在上一个时钟作用后所产生的新相位数据反馈到累加器的输入端,以使加法器在下一个时钟的作用下继续与频率控制数据相加。这样,相位累加器在参考时钟的作用下将进行线性相位累加,当相位累加器累加满时,就会产生一次溢出,以完成一个周期性的动作,这个周期就是DDS 合成信号的一个频率周期,相位累加器的溢出频率就是DDS 输出的信号频率。 2、DDS 参数计算 相位寄存器每经过2N/M 个f c 时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,整个DDS 系统输出一个正弦波。 输出正弦波频率: 2 N C out f f M ? = 本设计中,N=10,M 为位宽为32的频率控制字,fc=20Mhz 二、DDS 电路结构设计 1、电路描述 接口信号 名称 位宽 方向 描述 备注 freq 32 输入 输入频率字 reset 1 输入 复位 高电平异步复位 clock 1 输入 时钟 上升沿有效 sinout 8 输出 输出波形 2补码格式 2、电路结构 DDS波形发生器电路组成及功能 、DDS波形发生器电路的组成 本系统以单片机STC89C52为核心,采用了直接数字合成技术(DDS),实现了频 率任意调节的正弦波,方波,三角波以及特定的任意信号,产生的各类波形精度高,稳定性好,采用友好的人机界面,操作方便。系统总框图如下图所示: (1)相位累加地址发生器 使用可编程逻辑器件IC4 GAL16V8编程得到累加相位码,也就是波形的地址码。这里的GAL16V8是100进制计数器,相位累加时,对应一个波形100个数据的地址。 GAL16V8拥有8个输入端和8个输出端,可以单独选择每个输出端的极性,灵活的进行输出端的组合排列、可重复编程、频带范围宽,工作频率很高。使用GAL16V8做相位累加地址发生器使得电路更加简洁,保证在高频率下的稳定工作。 (2)数据存储器 使用外部ROM数据存储器IC5 27C64,已经预先把相关波形的量化数据写入该外部ROM中。 (3)D/A模数转换电路 使用数模转换集成芯片IC6 DAC0832,DAC0832是一个8位的电流式的数模转换器,就是把波形数据转化为波形真实的模拟信号。波形信号为电流信号,因此输出端还要接运算放大器,把电流信号转换为电压信号。 (4)双极性转换电路及滤波电路 可 编 程 .M 来 信 号 信 号 報 动 输 出 DDS波形发生器系统框图 采用反相比例运算放大电路IC7 TL084 中的A,B 运放,将D/A 输出的单极性信号转 换为双极性信号。 为确保产生波形的质量,减少波形失真度,使输出波形光滑,须用低通滤波器把高频分量滤掉。在此采用自动线性跟踪Butterworth 有源滤波器,在此采用二阶有源低通滤波器,即TL084 中的 C 运放及R19,C18,R20,C10 两节低通滤波器组成。 (5)显示及控制电路 本机器需要进行人机对话,根据系统设计要求,采用独立式微动按钮S2?7输入,八只七段LED1?8数码管作为输出显示,清晰可见。使用时可以选择方波、三角波和正弦波三种波形的输出;可调节不同波形的输出频率,并实现了1Hz 的频率步进。 (6)单片机电路 单片机电路是DDS 波形发生器的核心电路,它由微处理器IC12 AT89S52 及外围电路、元器件等组成。它由P0和P1共16个端口与显示电路相连接,把各种的输出波形的相关数据送到八只七段LED i?8数码管显示。 还与可编程逻辑器件IC4 ,外部ROM 数据存储器IC5 相连接,提供可编程基准信号:使用单片机定时器产生固定频率,波形稳定,为相位累加地址发生器提供基准信号。 另外由P2.0?P2.5接键盘的6只微动按钮S2?7,作控制输出信号之用。 微处理器IC12已经按功能要求,把相关的程序写入到芯片中。 (7)电源电路 本系统中,许多集成电路,如单片机、D/A 电路、运算放大器等都需要直流电源进行供电才能工作。单片机、EEPROM等都以5V电源供电,而运算放大器需要±2V供电,因此在电源板的设计过程中,要同时获得+5V、±2V的直流电压。LM7812输出电压为 +12V,LM7912输出电压为-12V,LM7805输出电压为+5V,三者的性能都能满足 设计要求。 在具体电路中,由市电AC220V经变压器降压为双AC12V后,接入到经由二极管VD3 组成的单相全波整流电桥整流,由电容器C8?11滤波后一路电压经过三端稳压器 ?6 LM7912稳压后输出+12V,另一路电压经过三端稳压器LMC7912稳压后输出-12V电压。 ±2V电压作为模拟放大器的电源电压,电容器C12?17是滤波电容。其中+12V电压经三端稳压器LM7805 稳压后输出+5V 电压,作为AT89S51、CAL16V8、27C64、URL2803、DAC0832、74LS244等数字集成电路的电源电压。考虑到D/A转换器在进行数模转换时,需要较稳定、精度较高的参考电压,在电源板设计过程中,将LM7812输出的+12V电 机械原理考试题 一、(10分)单项选择题(从给出的A、B、C、D中选一个答案,每小题1分) 1.由机械原理知识可知,自行车应属于。 A机器B机构C通用零件D专用零件 2.平面运动副按其接触特性,可分成。 A移动副与高副B低副与高副C转动副与高副D转动副与移动副3.铰链四杆机构的压力角是指在不计摩擦情况下作用与上的力与该力作用点速度间所夹的锐角。 A主动件B连架杆C机架D从动件 4.与连杆机构相比,凸轮机构最大的缺点是。 A惯性力难于平衡B点、线接触,易磨损C设计较为复杂D不能实现间歇运动 5.盘形凸轮机构的压力角恒等于常数。 A摆动尖顶推杆B直动滚子推杆C摆动平底推杆D摆动滚子推杆6.对心直动尖顶从动件盘形凸轮机构的推程压力角超过许用值时,可采用措施来解决。 A增大基圆半径B改变凸轮转向C改用滚子从动件D减小基圆半径7.齿数z=42,压力角α=20°的渐开线标准直齿外齿轮,其齿根圆基圆 A大于B等于C小于D小于且等于 8.渐开线直齿圆柱齿轮传动的重合度是实际啮合线段与的比值。 A齿距B基圆齿距C齿厚D齿槽宽 9.渐开线标准齿轮是指m、α、h a*、c*均为标准值,且分度圆齿厚齿槽宽的齿轮。A大于B等于C小于D小于且等于 10.在单向间歇运动机构中,的间歇回转角在较大的范围内可以调节。 A槽轮机构B不完全齿轮机构C棘轮机构D蜗杆凸轮式间歇运动机构 二、(10分)试计算下列运动的自由度数。(若有复合铰链,局部自由度和虚约束,必须明确指出),打箭头的为原动件,判断该运动链是否成为机构。 三、已知一偏置曲柄滑块机构,主动件曲柄AB顺时钟回转,滑块C向左为工作行程,行程速比系数为K=1.1,滑块形成S=40mm,偏距e=10mm。 1.试合理确定其偏置方位,用图解法设计该机构,求曲柄AB、连杆BC,并画出机构草图。2.试用解析法求其非工作形成时机构的最大压力角αmax。 3.当滑块C为主动件时,画出机构的死点位置。 4.当要求偏置曲柄滑块机构尺寸不变的条件下,试串联一个机构,使输出滑块C的行程有所扩大(不必计算尺寸,用草图画出方案即可)。 四、现需设计一偏心直动滚子从动件盘形凸轮机构,设已知凸轮以等角速度ω1=1rad/s沿逆时钟方向回转,从动件向上为工作行程,从动件的行程为h=35mm,偏距e=10mm,滚子半径r r=5mm,凸轮的推程运动角φ1=120°,回程运动角φ2=120°,近停运动角φ3=120°,推程段的许用压力角[α]=30°。 =200mm/s,位移S=20mm的条件下,确定凸轮的基圆1.试根据在推程段从动件最大速度V max 半径r 。 b 2.合理确定从动件的偏置方位,用草图画出所设计的凸轮机构。 3.画出凸轮从最低位置转过φ=90°时,机构的压力角α及其位移S。 五、(22分)(一)采用标准齿条刀具加工渐开线直齿圆柱齿轮,已知刀具齿形角α=20°,齿距为4πmm,加工时刀具移动速度v=60mm/s,轮坯转动角速度为1rad/s。 1.试求被加工齿轮的参数:模数m、压力角α、齿数z,分度圆直径d,基圆直径d b;2.如果刀具中心线与齿轮毛坯轴心的距离L=58mm,问这样加工的齿轮是正变位还是负变位齿轮,变位系数是多少? (二)已知斜 机械原理试卷答案 一、填空及选择(每题1分,共20分) 硬件描述语言课程设计 题目:基于Verilog的DDS设计与显示 学院:自动化工程学院 专业:信号与信息处理 年级:2012级 姓名:黄山 2013年1 月19 日 1.设计要求 设计一个DDS 信号发生器,能够产生三角波,要求频率、相位可调。实现VGA 显示波形和参数。要求用DE2-70开发板完成。 设计要求: 一、DDS 信号发生器设计要求: (1) 频率两档可调; (2) 峰峰值两档可调; 二、VGA 波形和字符显示设计要求: (1) 用红色显示2个周期波形; (2) 在屏幕下方显示字符库。 2.设计原理及分析 一)DDS 原理(以正弦信号为例) 对于正弦信号发生器,它的输出可以用下式来描述: (1) 其中,S OUT 是指该信号发生器的输出信号波形,f OUT 指输出信号对应的频率。上式的表述对于时间t 是连续的,为了用数字逻辑实现该表达式,必须进行离散化处理,用基准时钟clk 进行抽样,令正弦信号的相位θ为 t f out πθ2= (2) 在一个clk 周期Tclk ,相位θ的变化量为 clk out clk out f f T f /22ππθ==? (3) 为了对θ?进行数字量化,把2π切割为2N 由此,每份clk 周期的相位增量θ?用量化值 (4) 且θ?B 为整数。 sin(2)=sin() out out S A f t A πθ=22N B θ θπ ??≈?2N out CLK f B f θ?≈ ? (5) 显然,信号发生器的输出可描述为: (6) 其中θK-1指前一个clk 周期的相位值,同样得出 (7) 由上面的推导可以看出,只要对相位的量化值进行简单的累加运算,就可以 得到正弦信号的当前相位值,为用于累加的相位增量量化值θ?B 决定了信号的输出频率f OUT ,并呈现简单的线性关系。 直接数字合成器DDS 就是根据上述原理而设计的数控频率合成器,主要由相位累加器、相位调制器、正弦ROM 查找表、和DAC 构成。如图1中相位累加器、相位调制器、正弦ROM 查找表是DDS 结构中的数字部分,由于具有数控频率合成的功能,可称为NOC(Numerically Controlled Oscillators)。 BK0 BK1 BK2 BK3 BKI0 BKI1BKI2 BKI3 Q0 MULT A 幅值输入 Q 图1 DDS 信号发生器结构 二)VGA 显示原理 常见的计算机显示器有CRT ( Cathode Ray Tube ,阴极射线管)显示器和液晶显示器,本次设计针对CRT 显示。CRT 中的阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生RGB 三基色,合成一个彩色像素。用逐行扫描的方式显示图像。扫描从屏幕左上方开始,从左到右,从上到下,进行扫描。每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT 对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步, 1sin(+) k outk S A B B θθ-?=N k θπ θ B k 221 1 ?= --机械原理考试试题及答案详解 (1)

基于FPGA的DDS设计

DDS基本原理及技术指南

DDS信号发生器电路设计

dds工作原理

机械原理试题及答案2份

DDS信号发生器原理

机械原理测试题及答案

详细设计方案_DDS

DDS原理及AD9851电路设计、测试

最新机械原理期末考试及答案

DDS的原理及镜像频谱分析

机械原理考试试题及答案3篇

DDS设计实验报告(DOC)

机械原理期末考试试卷(及答案)2017

DDS电路设计

DDS波形发生器电路原理及功能

机械原理考试题及答案

基于Verilog的DDS设计与显示