F题-位同步时钟提取电路

2016年TI 杯大学生电子设计竞赛

参赛注意事项

(1)7月25日8:00 竞赛正式开始。本科组参赛队只能在【本科组】题目中任选一题;高职高专组参

赛队在【高职高专组】题目中任选一题,也可以选择【本科组】题目。

(2)参赛队认真填写《登记表》内容,填写好的《登记表》交赛场巡视员暂时保存。

(3)参赛者必须是有正式学籍的全日制在校本、专科学生,应出示能够证明参赛者学生身份的有效

证件(如学生证)随时备查。

(4)每队严格限制3 人,开赛后不得中途更换队员。

(5)竞赛期间,可使用各种图书资料和网络资源,但不得在学校指定竞赛场地外进行设计制作,不

得以任何方式与他人交流,包括教师在内的非参赛队员必须迴避,对违纪参赛队取消评审资格。 (6)7月28日20:00 竞赛结束,上交设计报告、制作实物及《登记表》,由专人封存。

F 题:位同步时钟提取电路

【本科组】

1.任务

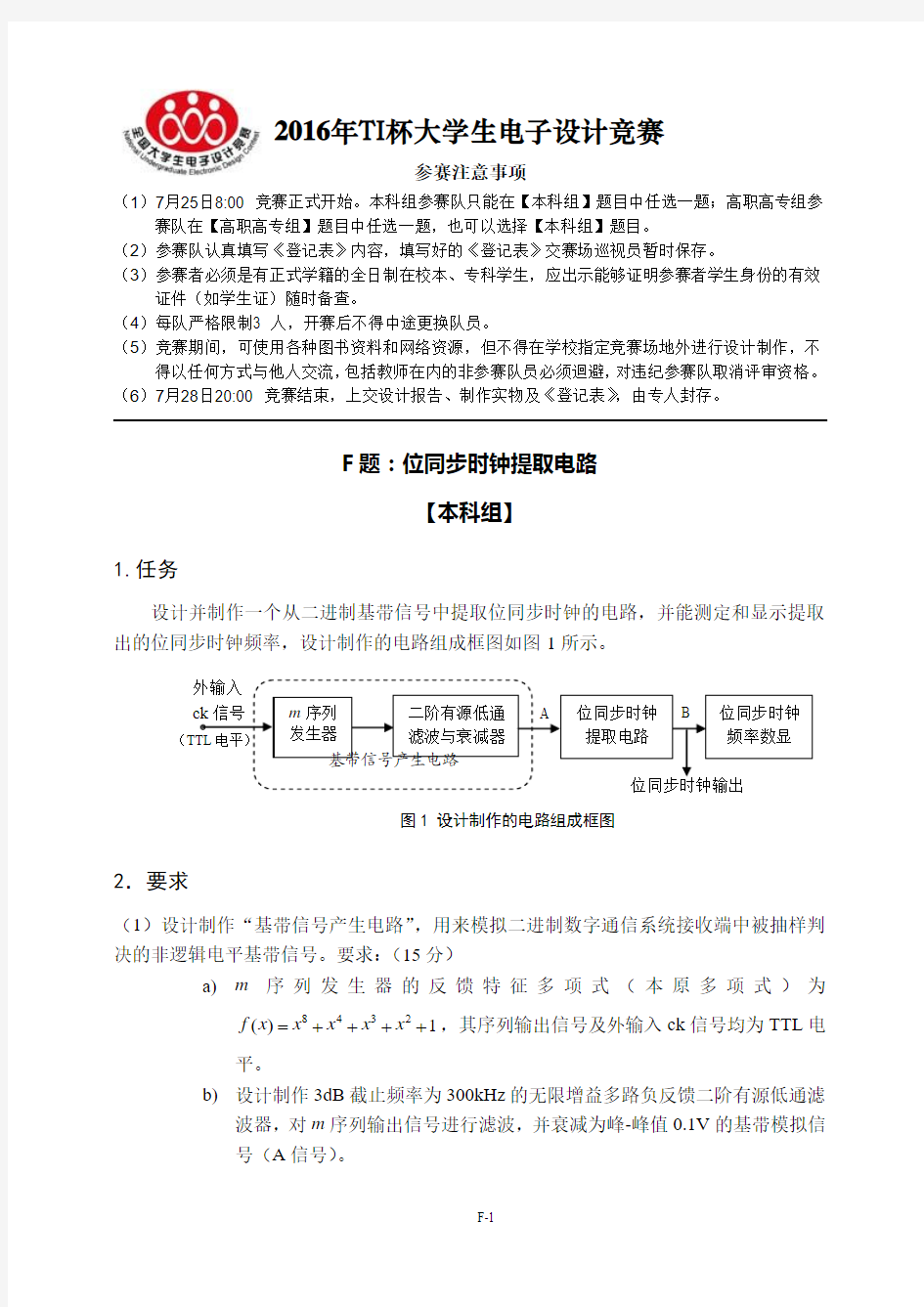

设计并制作一个从二进制基带信号中提取位同步时钟的电路,并能测定和显示提取出的位同步时钟频率,设计制作的电路组成框图如图1所示。

2.要求

(1)设计制作“基带信号产生电路”,用来模拟二进制数字通信系统接收端中被抽样判决的非逻辑电平基带信号。要求:(15分)

a) m 序列发生器的反馈特征多项式(本原多项式)为

1)(2348++++=x x x x x f ,其序列输出信号及外输入ck 信号均为TTL 电平。

b) 设计制作3dB 截止频率为300kHz 的无限增益多路负反馈二阶有源低通滤

波器,对m 序列输出信号进行滤波,并衰减为峰-峰值0.1V 的基带模拟信号(A 信号)。

图1 设计制作的电路组成框图

(

(2)当m序列发生器外输入ck信号频率为200kHz时,设计制作可从A信号中提取出位同步时钟(B信号)的电路,并数字显示同步时钟的频率。(30分)

(3)改进位同步时钟提取电路,当m序列发生器外输入ck信号频率在200kHz~240kHz 之间变化时,能从A信号中自适应提取位同步时钟,并数字显示同步时钟的频率。(30分)

(4)降低位同步时钟(B信号)的脉冲相位抖动量?,要求

?≤1个位同步时钟周期

max

的10%。(15分)

(5)其他。(10分)

(6)设计报告。(20分)

3.说明

(1)位同步是数字同步传输的基础同步技术,是指接收端提取的位同步时钟与发送端位时钟在频率上严格相等、相位差固定的信号同步状态。接收端位时钟需从收到的基带数据序列中提取,并将作为接收端的抽样判决脉冲及进一步实现其他同步使用。数字通信系统中的“位”指的是最基本的码元,发送端位时钟(题目中m序列发生器外输入时钟ck)是数据序列的码元时钟。

(2)要求“基带信号产生电路”必须制成单独的电路板,只能用两条输出信号线(A信号线、地线)与位同步时钟提取电路部分连接。

(3)无限增益多路负反馈二阶有源低通滤波器类型(如切比雪夫型或巴特沃斯型)不限。

电流和电路单元测试题(Word版 含解析)

电流和电路单元测试题(Word版含解析) 一、初三物理电流和电路易错压轴题(难) 1.归纳式探究——研究电子在电场中的偏转: 如图1,给两块等大、正对、靠近的平行金属加上电压,两板之间就有了电场。若将电子沿着平行于两板的中线方向入射到电场中,电子就会发生偏转。若两板间距为d,板长为L,所加的电压为U,电子入射初速度为v0,离开电场时偏移的距离为y,则经研究得到如下数据: 次数d/m L/m U/V v0/(m·s-1)y/m 14×10-20.2401×107 3.6×10-2 28×10-20.2401×107 1.8×10-2 34×10-20.1401×1070.9×10-2 48×10-20.21601×1077.2×10-2 58×10-20.22402×107 2.7×10-2 (1)y=k__________,其中k=_________(填上数值和单位)。本实验在探究影响电子离开电场时偏移的距离时,运用了_________法; (2)相同情况下,电子的入射速度越大,偏移距离越________。它们间的关系可以用图像2中的图线________表示; (3)现有两块平行相对的长度为5cm,间距为1cm的金属板,为了让初始速度为3×107m/s 的电子从一端沿两板间中线方向入射后,刚好能从另一端的金属板边缘处射出,需要加_____V的电压。

【答案】2 2 UL dv () 1022 910m/V s ??控制变量小b 200 【解析】 【分析】 【详解】 (1)[1]分析表中数据可知,1与2相比L、U、0v均相同,而d增大一倍,y减小为原来的1 2 ,可知y与d成反比;同理,1与3相比,y与2L成正比;2与4相比,y与U成正比;将第2次实验电压U增大至6倍,则y增大至6倍,此时 240V U= 2 10.810m y- =? 将此时的数据与第5次实验相比,y与2 v成反比,综上所述可得 2 2 UL y k dv = [2]将表格中第3次数据(其他组数据也可)代入 2 2 UL y k dv =计算可得 () 1022 910m/V s k=?? [3]本实验在探究影响电子离开电场时偏移的距离时,运用了控制变量法。 (2)[4]在其他情况相同时,y与2 v成反比,所以电子入射的初速度越大,偏移距离越小。 [5]它们之间的关系可以用图乙中的图线b来表示。 (3)[6]将已知数据中的y、d、L、0v和前面算出的k分别代入 2 2 UL y k dv =并计算可得 200V U= 2.如图所示是课本上的几个小实验,请根据要求填空. (1)在图甲所示实验中,将烧瓶内的水加热至沸腾后移去火焰,水停止沸腾.迅速塞上瓶塞,把烧瓶倒置并向瓶底浇冷水,此时会观察到________的现象,这是由一于在瓶底浇冷水后,液面上方________,导致液体的沸点降低所致. (2)图乙是小明制作的“浮沉子”.为观察到小瓶在水中的浮沉现象,大瓶瓶盖应该 ________(旋紧/拧开);为使漂浮于水面上的小瓶子下沉,小明应________ (松开/捏紧)手指.

基于FPGA的新型位同步时钟提取方案的设计

一种基于FPGA的新型位同步时钟提取方案及实现 摘要: 关键词:位同步,锁相环,FPGA,异步串行码流 1 引言: 同步技术在数字通信系统中,是非常重要的技术。位同步是最基本的同步。位同步时钟信号不仅用于对输入码元信号的监测保证收发同步,而且在对获取祯同步,群同步及对接收的数字码元进行各种处理过程中也为系统提供了一个基准的同步时钟。 随着现代电子技术的发展,数字系统趋于模块化,小型化,芯片华,因此如何实现同步系统的模块化和芯片化是急需解决的问题。 在数字通信中,通常直接从接收到的数字信号中提取位同步信号,这种直接法按其提取同步信号的方式,大致可分为滤波法和锁相法。锁相法是指利用锁相环来提取位同步信号的方法,本设计方案就是基于锁相环的位同步提取方法,能够比较快速地提取位同步时钟,并且设计简单,方便修改参数。采用Quartus II 设计软件对系统进行了仿真试验,并用Altera的Cyclone II系列FPGA芯片Ep2c5予以实现。 2 位同步时钟提取方案的原理 本文设计的方案可以从异步串行码流中提取位同步时钟信号,设计思想的基本出发点是在外部码流(code_in)的上升沿和本地时钟(clk)上跳沿相比较无非两 种 情 况, 如图1和图2所示: 图1 码流滞后于本地时钟△T示意图图2 码流超前于本地时钟△T示意图 从码流上跳沿的角度来看,若将码流code_in与本地时钟clk进行逻辑相与,若相与结果为“1”则说明码流滞后于本地时钟,若为“0”则说明码流超前于本地时钟。用VHDL语言描述为: if (code_in’event and code_in=’1’) then if (code_in and clk)=’1’ then q<=’1’ else q<=’0’ end if end if 程序中输出信号q可作为控制电路的输入信号。 本设计方案的系统框图如图3所示:

时间同步系统在线监测可行性研究报告

附件4 甘肃电网智能调度技术支持系统 时间同步系统在线监测 技术改造(设备大修)项目 可行性研究报告模板项目名称: 项目单位: 编制: 审核: 批准: 编制单位: 设计、勘测证书号:

年月日

1.总论 时间同步系统在线监测功能,将时钟、被授时设备构成闭环,使对时状态可监测,且监测结果可上送,从而将时间同步系统纳入自动化监控系统管理。时间同步系统在线监测的数据来源分为两大类:设备状态自检数据和对时状态测量数据。设备状态自检主要是被监测设备自身基于可预见故障设置的策略,快速侦测自身的故障点。对时状态测量则是从被监测设备外部对其自身不可预见的故障产生的结果进行侦测,这两种方法较为完整的保证了时间同步系统监测的性能和可靠性。 1.1设计依据 2013年4月,国调中心专门下发了〔2013〕82号文《国调中心关于加强电力系统时间同步运行管理工作的通知》 1.2主要设计原则 通过在原系统上建立一套通讯技术及软件来实现系统级的时间同步状态在线监测功能。采用低建设成本、低管理成本、低技术风险的手段,解决当前自动化系统时间同步体系处于开环状态,缺乏反馈,无法获知工作状态紧迫现状,使时钟和被对时设备形成闭环监测,减少因对时错误引起的事件顺序记录无效,甚至导致设备死机等运行事故,并在此前提下尽可能的提高监测性能,减少复杂度。

1.3设计水平年 系统模块使用年限10年。 1.4设计范围及建设规模 智能调度技术支持系统(主站)针对时钟同步检测功能修改主要涉及前置应用,前置应用以104 或476 规约与变电站自动化系进行过乒乓原理对时,根据对时结果来检测各变电站时钟对时的准确性,从而保证全网时钟同步的准确性。同时,以告警直传方式接收变电站时间同步监测结果,包含设备状态自检数据和对时状态测量数据。 1.5主要技术经济指标 1.6经济分析 2.项目必要性 2.1工程概况 智能电网调度技术支持系统及各变电站都以天文时钟作为自己的时间源,正常情况下实现了全网时间的一致。 2.2存在主要问题 近期,电力系统时间同步装置在运行中发现的时钟异常跳变、时钟源切换策略不合理及电磁干扰环境下性能下降等问题,反映出电力系统时间同步在运行管理、技术性能、检验检测管理、在线监测手段及相关标准等方面仍需进一步完善和加强。

人教版九年级物理电流和电路单元测试题及答案

电流和电路单元测试题 一、单项选择题(每小题3分,共36分) 1、在晴朗的冬日,用塑料梳子梳干燥的头发,头发会越梳越蓬松,主要原因是( ) A.梳头时,空气进入头发 B.头发和梳子摩擦后,头发因带同种电荷而相互排斥 C.梳子对头发有吸引作用 D.头发和梳子摩擦后,头发因带异种电荷而相互吸引 2、依据英国物理学家卢瑟福的原子核式模型理论,在原子中不带电的是 ( ) A .中子 B .质子 C .电子 D .原子核 3、下列四组物体中,都属于绝缘体的一组是 ( ) A.碳棒、人体、大地 B.水银、铜丝、铁块 C.陶瓷、干木、塑料 D.大地、人体、陶瓷 4、如图15-1所示的电路中,哪个电路是正确的( ) 5、电路中能产生持续电流的条件是( ) A .电路中有用电器 B .电路中有电源 C .电路中有开关 D .电路中有电源,还要形成通路 6、关于电流的方向的说法中正确的是( ) A .带电微粒的运动方向就是电流的方向 B .金属中自由电子移动的方向就是电流的方向 C .负电荷定向移动的方向与规定的电流方向相反 D .科学上规定正电荷运动的方向就是电流的方向 7、电路中的电流既看不见,也摸不着,但是它的许多特点和水流、车流类似,人们在研究电 流特点时,多用水流来相比,这种科学思维方法可以叫做( ) A .控制变量法 B .模型法 C .类比法 D .归纳法 8、使用电池的时候,不允许用导线直接把电池的两极连接起来,这是因为( ) A.这样连接电路中没有电流 B.这样连接电路中电流太小,用电器无法工作 C.这样连接有触电危险 D.这样连接会在导线中产生很大的电流,损坏电池 9、日常的生活经验告诉我们,家中的电灯、插座、彩色电视机、电冰箱等电器设备之间的连 接方式是( ) A.一定是并联 B.可以是串联,也可以是并联 C.一定是串联 D.电灯与插座应该串联,彩色电视机与电冰箱应该并联 10、某家用电器正常工作时,通过的电流大约为5 A ,该用电器可能是( ) A .电视机 B .空调 C .白炽灯 D .洗衣机 11、如图15-2所示的电路中,有可能造成电源和电流表都损坏的是( ) 12、居民楼的楼道 里,夜间只是偶尔有人经过,电灯总 是亮着造成很大浪费。科研人员利用“光敏”材料制成“光控开关”,天黑时自动闭合, 天亮时自动断开;利用“声敏”材料制成“声控开关”,当有人走动发出声音时,自动闭 合,无人走动时自动断开。若将这两种开关配合使用,就可以使楼道灯变得“聪明”,则 这种“聪明”的电路是( ) 图15-1 图15-2

同步时序电路的设计步骤

同步时序电路的设计步骤 同步时序电路的设计步骤 同步时序电路的分析是根据给定的时序逻辑电路,求出能反映该电路功能的状态图。状态图清楚地表明了电路在不同的输入、输出原状态时,在时钟作用下次态状态的变化情况。同步时序电路的设计的设计是分析的反过程,其是根据给定的状态图或通过对设计要求的分析得到的状态图,设计出同步时序电路的过程。 这里主要讨论给定状态图的情况下的同步时序电路的设计,对于具体的要求得到状态图的过程一般是一个较复杂的问题,这是暂不讲。根据已知状态图设计同步时序电路的过程一般分为以下几步: 1.确定触发器的个数。首先根据状态的个数来确定所需要触发器的个数,如给定的状态个数为n,由应满足 n≤2K,K为实现这来状态所需要的触发器的个数。(实际使用时可能给定的状态中存在冗余项,这时一般还须对状态进行化简。) 2.列出状态转移真值表。根据状态列出状态转移真值表,也称状态表、状态转移表。 3.触发器选型。选择合适的触发器,通常可选的触发器有:JK-FF,D-FF,T-FF,一般使用较广的为JK-FF。根据状态图和给出的触发器的型号写出其输入方程,通常在写输入方程时须对其进行化简,以使电路更简单。 4.求出输出方程。根据状态表,求出输出逻辑函数Z的输出方程,还过有些电路没有独立的输出,这一步就省了。 5.画出逻辑图。根据输入方程、输出方程画出逻辑电路图。 6.讨论设计的电路能否自启动。在设计的电路中可能出现一些无关的状态,这些状态能否经过若干个时钟脉冲后进行有效的状态。 同步时序电路设计举例 例按下图状态图设计同步时序电路。 1.根据状态数确定触发器的数目:由状态图可以看出,其每个状态由两个状态,故可用两个触发器。其变量可 用Q 1,Q 表示; 2.根据状态图列出状态表:状态表的自变量为输入变量x和触发器当前状态Q 1 n,Q n,而应变量为触发器的次态 Q 1n+1Q n+1、及输出z,列表时将自变量的所有组合全部列出来,其中当Q 1 n Q n=01的状态为不出现,其输出可看作任意 项处理。

TI杯大学生电子设计竞赛题目

2016年T I杯大学生电子设计竞赛 A题:降压型直流开关稳压电源 1.任务 以TI公司的降压控制器LM5117芯片和CSD18532KCSMOS场效应管为核心器件,设计并制作一个降压型直流开关稳压电源。额定输入直流电压为时,额定输出直流电压为,输出电流最大值为。测试电路可参考图1。 图1电源测试连接图 2.要求 (1)额定输入电压下,输出电压偏差:;(10分) (2)额定输入电压下,最大输出电流:;(10分) (3)输出噪声纹波电压峰峰值:;(10分) (4)从满载变到轻载时,负载调整率: ;(10分) (5)变化到17.6V和13.6V,电压调整率: (10分)(6)效率;(15分) (7)具有过流保护功能,动作电流;(10分) (8)电源具有负载识别功能。增加1个2端子端口,端口可外接电阻R(1kΩ-10kΩ)作为负载识别端口,参考图1。电源根据通过测量端口识别电阻R的阻值,确定输出电压,;(10分) (9)尽量减轻电源重量,使电源不含负载的重量。(15分)

(10)设计报告(20分) 3.说明 (1)该开关稳压电源不得采用成品模块制作。 (2)稳压电源若含其它控制、测量电路都只能由端口供电,不得增加其他辅助电源。(3)要求电源输出电压精确稳定,或,作品不参与测试。 2016年TI杯大学生电子设计竞赛题 B题:物品分拣搬送装置 1.任务 在一个以木条(截面不大于3cm×4cm,木质本色)围成的100cm×150cm的A区域内,散落着边长均为4cm的正方体。设计一自动物体搬运系统,能够快速将这些正方体移至指定区域。A区域的颜色为白色,B区域为黑色,C区域为红色。 2.要求 (1)在A区域内任意放置了12只黑色正方体,以最快的速度将这些正方体移送到B区域,完成时间不得超过180秒;(24分) (2)将A区域的12只黑色正方体以最快的速度移送到红色C区域;完成时间不得超过180秒;(26分) (3)A区域12只正方体中有桔黄色与黑色两种颜色,以最快的速度将桔黄色正方

数字钟电路pcb设计

¥ 摘要 本设计针对数字钟PCB板设计较为复杂的问题,利用国内知名度较高、应用最广泛的电路辅助设计软件protel99se进行了电路板的设计。本设计介绍了各部分电路的构成及准确完成了数字钟PCB电路板的设计。本设计数字钟原理图分析入手,说明了在平台中完成原理图设计,电气检测,网络表生成,PCB设计的基本操作程序。数字钟的主要电路是由电源电路、显示电路、校时电路、晶体振荡电路组成。PCB是电子元器件的支撑体,是电子元器件电气连接的提供者。PCB的设计是以电路原理图为根据,实现电路设计者所需要的功能。优秀的版图设计可以节约生产成本,达到良好的电路性能和散热性能。 关键词:数字钟;PCB;原理图;芯片 — 【

目录 前言 (1) 第一章@ 第二章绪论 (2) 数字钟的研究背景和意义 (2) 数字钟的发展和趋势 (2) 第二章系统电路的绘制 (3) 电路组成方框图 (3) 电路原理图制作 (3) 原理图环境设置 (4) 绘制原理图 (5) $ 电气规则检查及网络表输出 (7) 原理图分析 (10) 晶体振荡器 (10) 分频器 (11) 计数器电路 (12) 显示和译码电路 (12) 电源电路 (13) 第三章电路板PCB设计 (14) , PCB设计规范 (14) PCB设计流程 (17) 输出光绘文件 (21) PCB制件作 (23)

心得体会 (25) 参考文献 (26) 附图 (27) 附表 (28) "

前言 PCB(Printed Circuit Board),中文名称为印制线路板,简称印制板,是电子工业的重要部件之一。几乎每种电子设备,小到电子手表、计算器,大到计算机,通讯电子设备,军用武器系统,只要有集成电路等电子元器件,为了它们之间的电气互连,都要使用印制板。在较大型的电子产品研究过程中,最基本的成功因素是该产品的印制板的设计、文件编制和制造。印制板的设计和制造质量直接影响到整个产品的质量和成本,甚至导致商业竞争的成败。 Protel系列电子设计软件是在EDA行业中,特别是在PCB设计领域具有多年发展历史的设计界软件,由于其功能强大,操作简单实用,近年来成为国内发展最快。 Protel 99已不是单纯的PCB(印制电路板)设计工具,而是由多个模块组成的系统工具,分别是SCH(原理图)设计、SCH(原理图)仿真、PCB(印制电路板)设计、Auto Router(自动布线器)和FPGA设计等,覆盖了以PCB为核心的整个物理设计。该软件将项目管理方式、原理图和PCB图的双向同步技术、多通道设计、拓朴自动布线以及电路仿真等技术结合在一起,为电路设计提供了强大的支持。 随着计算机事业的发展,在信息化时代,电路设计中的很多工作都可以用计算机来完成。这样就大大减轻了设计人员的体力劳动强度,并且保证了设计的规范性准确性。而Protel99SE技术已越来越为人们所关注,人们利用protel99SE绘制各种原理图,进而制作出各种各样的科技产品已经成为当今世界的一个不可或缺的组成部分,所以说Protel99SE技术已越来越显得重要。

XP系统时间同步解决方案

XP系统时间同步不成功_Windows time服务无法启动解决 同步时间的服务器是:210.72.145.44 xp自带的时间同步服务器老是会连不上,而且时间还会差一秒。 这里就教大家换成中科院国家授时中心的服务器,同步就方便多了。 1.双击右下角的时间。 2.把服务器改成210.72.145.44 3.按同步就可以了,一般不会出错。即使是高峰时期,三次之内闭成功,比美国的服务器好多了。 另外系统默认的时间同步间隔只是7天,我们无法自由选择,使得这个功能在灵活性方面大打折扣。其实,我们也可以通过修改注册表来手动修改它的自动同步间隔。 1. 在“开始”菜单→“运行”项下输入“Regedit”进入注册表编辑器 2. 展开[HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Services\W32Time\TimeProviders\Nt pClient ] 分支,并双击SpecialPollInterval 键值,将对话框中的“基数栏”选择到“十进制”上 3. 而这时在对话框中显示的数字正是自动对时的间隔(以秒为单位),比如默认的604800就是由7(天)×24(时)×60(分)×60(秒)计算来的,看明白了吧,如果您想让XP以多长时间自动对时,只要按这个公式算出具体的秒数,再填进去就好了。比如我填了3天,就是259200。 Windows time服务用于和Internet同步系统时间,如果时间无法同步有可能是服务没有随系统启动,可以在运行处输入"services.msc"打开服务控制台,找到"windows time"服务设置为自动并启动即可。 如果启动该服务时提示: 错误1058:无法启动服务,原因可能是已被禁用与其相关联的设备没有启动。 原因是windows time服务失效。 修复: 1.运行cmd 进入命令行,然后键入 w32tm /register 正确的响应为:W32Time 成功注册。 如果提示w32tm命令不内部或外部命令……,是因为系统盘下的system32目录不存在w32tm.exe和w32time.dll这两个文件,到网上下载一个或者到其他电脑复制过来放下这个目录下再运行 2.如果上一步正确,在cmd命令行或运行里用net start "windows time" 或net start w32time 启动服务。 如果无法启动Windows Time服务,同时提示:系统提示“错误1083:配置成在该可执行

电流和电路单元测试卷(含答案解析)

电流和电路单元测试卷(含答案解析) 一、初三物理电流和电路易错压轴题(难) 1.在“探究串联电路中电流的特点”实验中,小明连接了如图所示的电路,闭合开关后,发现两个小灯泡都不发光,电流表没示数,检查发现各连线接触良好. (1)于是小明提出用导线两端依次连接ab、ac、ad两点的设计方案,其中用导线连接哪两点间不合适?答:________ (选填“ab”、“ac”或“ad”). (2)当小明用导线连接ab时,两灯泡不发光;连接ac时,小灯泡1L不发光,小灯泡2L 很亮,然后又熄灭.那么,原电路中的故障是________,小灯泡2L又熄灭的原因可能是 _____________. (3)此时,同组的小红提出用电压表检查电路,你认为小红的方案可行吗?答:________(选填“可行”或“不可行”). 【答案】ad L1断路电路中电流太大,灯丝被烧断可行 【解析】 【分析】 【详解】 (1)于是小明提出用导线两端依次连接ab、ac、ad两点的设计方案,连接ab两点可以检查电流表有没有故障,再连接ac两点,就可以检查L1、L2有没有故障,连接ad两点,电路短路,可能会损坏电源,所以连接ad两点不合适; (2)当小明用导线连接ab时,两灯泡不发光,说明电流表完好;连接ac时,小灯泡1L 不发光,小灯泡2L很亮,然后又熄灭.那么,原电路中的故障是L1断路,小灯泡2L又熄灭的原因可能是电路中电流太大,灯丝被烧断. (3)此时,同组的小红提出用电压表检查电路,小红的方案可行,可以分别把电压表接在ab之间、ac之间,看电压表的示数即可. 2.现有两只小灯泡L1、L2,它们的额定电压分别为2.5V和3.8V. (1)如图甲是小明测定灯泡L1额定功率的实物电路图(不完整). ①请用笔画线代替导线将实物电路图连接完整_____. ②闭合开关前,应将滑动变阻器的滑片P移到__端(选填“A”或“B”).闭合开关后发

简易电子时钟的设计

单片机课程设计报告设计题目:简易电子时钟的设计 院别: 专业班级: 学号:

姓名: 指导教师: 摘要 通过一学期单片机的学习,对其已经有了初步的了解,但是随着社会的不断发展,单片机的应用正在不断地走向深入,它特别适合于与控制有关的系统,越来越广泛地应用于自动控制,智能化仪器,仪表,数据采集,军工产品以及家用电器等各个领域,单片机往往是作为一个核心部件来使用,在根据具体硬件结构,以及针对具体应用对象特点的软件结合,以作完善。我们也借此课程设计的机会,对单片机有更深一步的了解与学习。 本次课程课程设计的目的是设计一个简易的电子时钟,通过一个8位共阴极数码管进行时、分、秒的显示,另外设置7个按键,一个用来调整小时,一个用来调整分钟,一个开关控制是否调整时间。 关键词:AT89C51,数码管,按键,DS1303时钟芯片

1.概述 本设计是锻炼我们的自学能力合作能力,依靠团队的力量去完成一项具体的任务系统的训练了所学知识,设计的过程必将是难忘的,这也将是大学向社会工作过度的一个重要阶段。 本阶段过后要去能够熟练的运用单片机中的计数器、定时器、中断、数码管显示等参考教材或者相关资料,采用C语言实现数字时钟功能,在数码管上实时显示,并运用Protues软件绘制电路原理图,并进行仿真验证和误差分析。 2.系统总体方案设计 2.1系统方案的确定 用6位数码管,可以显示出时、分、秒;用P2端口控制位选,由定时器进行时间的控制(秒);当总按键按下时可以进行时间调整; 2.2方案分析 2.3系统总框图 图2.1

3.系统硬件系统设计 3.1复位电路 单片机复位电路就好比电脑的重启部分,当电脑在使用中出现死机,按下重启按钮电脑内部的程序从头开始执行。单片机也一样,当单片机系统在运行中,受到环境干扰出现程跑飞的时候,按下复位按钮内部的程序自动从头开始执行。 复位电路的工作原理: 在单片机系统中,系统上电启动的时候复位一次,当按键按下的时候系统再次复位,如果释放后再按下,系统还会复位。所以可以通过按键的断开和闭合在运行的系统中控制其复位。单片机复位电路如下图 图3.1 3.2时钟电路 单片机运行需要时钟支持——就像计算机的CPU一样,如果没有时钟电路来产生时钟驱动单片机,那单片机就不能执行程序。 单片机可以看成是在时钟驱动下的时序逻辑电路。 以5l单片机为例随明:51单片机为l2个时钟周期执行一条指令。也就是说单片机运行一条指令,必须要用r2个时钟周期。没有这个时钟,单片机就跑不起来了,也没有办法定时和进行和时间有关的操作。 时钟电路是微型计算机的心脏,它控制着计算机的二个节奏。CPU就是通过复杂的时序电路完成不同的指令功能的。51的时钟信号可以由两种方式产生:一种是内部方式,利用芯片内部的振荡电路,产生时钟信号:另一种为外部方式,时钟信号由外部引入。

全厂网络时钟同步方案

全厂网络时钟同步方案 陈银桃,陆卫军,张清,章维 浙江中控技术股份有限公司,浙江杭州,310053 摘要:当前工控领域石化项目如乙烯、炼油日益趋向大型化、一体化和智能化。一个大型石化项目往往集成多套独立系统如DCS、SIS、CCS等,同时要求所有系统使用同一套网络时钟同步系统。本文提供了几种全厂网络时间同步方案,并分析了每个方案的优缺点和适用场合。 关键词:全厂网络时钟同步,SNTP,二级网络时钟同步方案,Private VLAN,ACL,路由,NAT Ways to Implement The Network Time Synchronization In The Plant Chen Yintao Zhejiang SUPCON Co., Ltd., Hangzhou, Zhejiang, 310053 Abstract:The petrochemical projects in the industrial control area run to large, integrative and intelligentized.A large petrochemical project always need to be integrated with many systems like DCS, SIS, CCS and so on .The network of these systems must be independent,while they should use the same network time synchronizer to achieve time synchronization.This article propose several implements of the network time synchronization in the whole plant. Keywords:Network Time Synchronization, NTP, Private VLAN, ACL, Route, NAT. 引言 随着国民经济发展,工控领域也随之蓬勃发展,石化项目如乙烯、炼油等日益趋向大型化、一体化和智能化。大型化体现在项目规模的剧增,典型项目如百万吨乙烯、千万吨炼油。一体化体现在一个大型石化项目往往集成多套系统如DCS、SIS、CCS,这些系统在功能、网络上分别独立,但需要实现全厂统一的时钟同步,以保持全厂所有系统的时钟同步。 普通的网络时钟同步服务器提供的网口较少,一般都在4个以下,同时可支持1-4个网络的系统时钟同步。当需要同步的子系统较多时,则需要配置可同时支持二三十个网络的特殊网络时钟同步服务器。但是在企业建设初期,往往很难准确预计将来的网络发展规模,这就需要事先规划设计

最新轨道交通时钟系统解决方案复习过程

轨道交通时钟系统解决方案 轨道交通时钟系统解决方案 地铁通信系统一般包括: 时钟系统是轨道交通重要的组成部分之一,而其在地铁站的主要作用是为上班族、来往的游客工作人员提供准确的时间信息,同时时

钟系统要为其他监控系统、控制系统等弱电子系统提供统一的时钟信号,使各系统的定时集中同步,在整个地铁系统中使用相同的定时标准。站厅及站台位置的时钟可以为旅客提供准确的时间信息;各车站办公室内及其它停车场内的时钟可以为工作人员提供准确的时间信息;向其它地铁通信子系统提供的时钟信息为地铁运行提供了标准的时间,保证了轻轨系统运行的准时,安全。 时钟子系统能够向地铁全部通信子系统提供准确的时钟信号。时钟信号以卫星自动定位系统所发的格林威治标准世界时间为准辅以铷原子钟或石英钟。时钟系统的控制中心向各分站或车场二级母钟发送时钟信号,再由二级母钟向其对应的子钟发送时钟信号;同时每站的各路时钟信号均需上传至时钟系统的监控中心,使之可以完成对全路各站所有时钟工作状态的监测和控制,并可在相应的管理客户机上完成各种需要的管理及配置功能。

设计区域:换乘大厅、进出口、监控室、控制室控制中心调度大厅和各车站的站厅、站台、车站控制室、公安安全室、票务室、变电所控制室及其它与行车有关的处所,并在车辆段/停车场信号楼运转室、值班员室、停车列检库、联合检修库等有关地点设置子钟。

相关产品 第一章教育和教育学 1 教育的发展 一、教育的概念 考点:教育是培养人的一种社会活动,是传承社会文化、传递生产经验的和社会生活经验的基本途径。 考点广义:凡是增进人们的知识和技能,影响人们思想观念的活动,都具有教育作用。 狭义:主要指学校教育。 学校教育是教育者根据一定的教育要求,有目的、有计划、有组织的通过学校的教育工作,对受教育者的身心施加影响,促使他

九年级电流和电路单元测试卷(解析版)

九年级电流和电路单元测试卷(解析版) 一、初三物理电流和电路易错压轴题(难) 1.现有两只小灯泡L1、L2,它们的额定电压分别为2.5V和3.8V. (1)如图甲是小明测定灯泡L1额定功率的实物电路图(不完整). ①请用笔画线代替导线将实物电路图连接完整_____. ②闭合开关前,应将滑动变阻器的滑片P移到__端(选填“A”或“B”).闭合开关后发现:小灯泡不亮,电流表示数为零,而电压表示数接近电源电压。经检查,电流表是完好的,仅滑动变阻器或小灯泡存在故障,则电路中的故障是__.排除故障后,闭合开关,仍发现小灯泡不亮,电流表指针偏转很小,要使该小灯泡发光只需__。 ③当电压表示数为2.5V时,电流表示数如图乙所示,则灯泡L1的额定功率为__W. (2)小华利用图丙所示的电路测出了灯泡L2的额定功率.图中R为阻值已知的定值电阻,还缺两个开关和一只电表(电流表或电压表),请在虚线框内补上这三个元件的符号,使电路完整,实验操作简单______. 【答案】A灯泡断路移动滑动变阻器0.8 【解析】 (1)①根据图中电表的正、负接线柱,从电源正极连接开关,滑动变阻器的接线柱要求一上一下的串联在电路中,所以将C或D连到电源负极即可,如下图所示:

②电压表有示数,说明电压表与电源连通;电流表示数几乎为零,灯泡不发光,说明电路断路或电路的总电阻很大,导致这一现象的原因可能是小灯泡断路而导致电压表串联在电路中; ③为了保护电路,闭合开关前,滑片P应处在使电路中电阻最大位置A端; 由乙图,电流表使用0-0.6A量程,分度值为0.02A,示数为0.32A,所以灯泡L1的额定功率:; (2)由上面的分析知,右上边的是电压表;左边两虚线框内是开关,如图所示: ①只闭合S和中间的开关,移动滑片使电压表示数为3.8V; ②保持滑片位置不动,断开中间开关,闭合左上边开关,测出灯与R的总电压,根据串联电路的电压特点计算出R两端电压U R; ③由计算出R的电流,即灯泡此时的电流,由P=U额I额计算灯泡L2电功率即可.故答案为:(1). (2). A (3). 灯泡断路 (4). 移动滑动变阻器(5). 0.8 (6). 【点睛】本题是测灯泡额定功率的实验,考查了电路连接、变阻器的使用、电表读数和功率计算以及特殊方法测功率的电路设计.特殊方法测功率时,只给电流表通常会使用并联电路,只给电压表时通常使用并联电路,利用已知阻值的电阻与电表的组合间接测电压或电流达到实验目的。 2.某小组同学通过自学得知:在两种金属组成的回路中,如果使两个接触点的温度不同,便在回路中将会出现电流.为了验证和探究其中规律,该小组利用铁丝和铜丝两种导线组成图(a)所示的闭合回路,并将相连的两个交叉点A、B分别置于烧杯中和酒精灯上方.做了如图(a)、(b)、(c)、(d)所示的四次实验.请仔细观察图中的装置、操作和现象,归纳得出初步结论.

同步时序逻辑电路的习题 数字逻辑

第五章 同步时序逻辑电路的习题 一、基本知识点 1、时序逻辑电路的一般结构 特点:a 、有存储电路(记忆元件);有组合电路(特殊时可没有) b 、包含反馈电路,电路功能与“时序”相关 c 、输出不仅与输入(X )有关,而且与存储状态(Y )有关 分类:(1)Mealy 型 Z =F (X ,Q ) 输出是电路的输入和现态的函数(注意输出与输入有直接关系) (2)Moore 型 Z =F (Q ) 输出仅仅是电路现态的函数(注意输出与输入没有直接关系) 同步时序逻辑电路:各触发器共用同一时钟信号,即电路中各触发器状态的转换时刻在统一时钟信号控制下同步发生。 异步时序逻辑电路:电路没有统一的时钟信号对状态变化进行同步控制,输入信号的变化将直接引起电路状态的变化。 //本课程将较少讨论异步时序逻辑电路 2、同步时序逻辑电路的描述 注意:任一个同步时序逻辑电路的结构和功能可用3组函数表达式完整地描述。 (1)激励函数表达式:存储电路输入Y 与电路输入X 和现态Q 之间的关系 Y =F (X ,Q ) //现态Q 就是上图存储电路原始的输出y k (2)次态函数表达式:电路的次态Q n+1与激励函数Y 和现态Q 之间关系 Q n+1=F (Y ,Q ) //次态Q n+1就是上图存储电路再次触发后的输出y k n+1 (3)输出函数表达式:电路的输出Z 和输入X 和当前现态Q 的关系 Mealy 型 Z =F (X ,Q ) Moore 型 Z =F (Q ) 输入信号 输出信号 X 1 X 2 X n Z 1 Z 2 Z m y s 过去输入 现态 现在输入 } 输出 输出 所有输入 现态

2016---TI杯大学生电子设计竞赛题目

2016年TI杯大学生电子设计竞赛 A题:降压型直流开关稳压电源 1.任务 以TI公司的降压控制器LM5117芯片和CSD18532KCS MOS场效应管为核心器件,设计并制作一个降压型直流开关稳压电源。额定输入直流电压为时,额定输出直流电压为,输出电流最大值为。测试电路可参考图1。 L R 图1 电源测试连接图 2.要求 (1)额定输入电压下,输出电压偏差:;(10分) (2)额定输入电压下,最大输出电流:;(10分) (3)输出噪声纹波电压峰峰值:;(10分) (4)从满载变到轻载时,负载调整率: ;(10分) (5)变化到17.6V和13.6V,电压调整率: (10分)(6)效率;(15分) (7)具有过流保护功能,动作电流;(10分) (8)电源具有负载识别功能。增加1个2端子端口,端口可外接电阻R(1kΩ-10kΩ)作为负载识别端口,参考图1。电源根据通过测量端口识别电阻R的阻值,确定输出电压,;(10分) (9)尽量减轻电源重量,使电源不含负载的重量。(15分) (10)设计报告(20分)

3.说明 (1) 该开关稳压电源不得采用成品模块制作。 (2) 稳压电源若含其它控制、测量电路都只能由端口供电,不得增加其他辅助电源。 (3) 要求电源输出电压精确稳定,或,作品不参与测试。 2016年TI 杯大学生电子设计竞赛题 B 题:物品分拣搬送装置 1.任务 在一个以木条(截面不大于 3cm×4cm,木质本色)围成的100cm×150cm 的A 区域内,散落着 边长均为4cm 的正方体。设计一自动物体搬运系统,能够快速将 这些 正方体移至指定区域。A 区域的颜色为白色,B 区域为黑色,C 区域 为红色。 2.要求 (1) 在A 区域内任意放置

电子时钟程序设计

1.设计目的 电子时钟是采用数字电路实现对日期、时、分、秒,数字显示的计时装置,由于数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度,远远超过老式钟表,钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表的报时功能。电子时钟已成为人们日常生活中的必需品,广泛应用于家庭、车站、码头、剧院、办公室等场所,给人们的生活、学习、工作带来极大的方便。不仅如此,在现代化的进程中,也离不开电子钟的相关功能和原理,比如机械手的控制、家务的自动化、定时自动报警、按时自动打铃、时间程序自动控制、定时广播、自动起闭路灯、定时开关烘箱、通断动力设备、甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。而且是控制的核心部分。因此,研究电子时钟及扩大其应用,有着非常现实的意义。 2.设计内容 设计思想 针对要实现的功能,拟采用AT89C51单片机进行设计,AT89C51 单片机是一款低功耗,高性能CMOS8位单片机,片内含4KB在线可编程(ISP)的可反复擦写1000次的Flash只读程序存储器,器件采用高密度、非易失性存储技术制造,兼容标准MCS- 51指令系统及80C51引脚

结构。这样,既能做到经济合理又能实现预期的功能。 在程序方面,采用分块设计的方法,这样既减小了编程难度、使程序易于理解,又能便于添加各项功能。程序可分为闹钟的声音程序、显示程序、闹钟显示程序、调时显示、定时程序。运用这种方法,关键在于各模块的兼容和配合,若各模块不匹配会出现意想不到的错误。

设计元件 元件 规格 数量 单片机 AT89C51 1 晶振 12MHz 1 晶振电容 30pF 2 按键 4 准备器件、搭接电 路 熟悉硬件 了解各引脚功 能 分块设计各部分电 路 将分块的电路组合 认真学习单片机汇编 语言 完成整体电路图 确定变成结构和思 路 综合各程序完成整体 程序 编辑各个程序模块 用Proteus 画出电路图 调试程序,进行修改 对仿真中出现的问题 进行改正 画出仿真图进行仿 真 仿真成功 软硬件结合,完成任务 书要求 验证硬件电路 成功 进行扩展

跨时钟域信同步方法种

跨时钟域信号同步方法6种 ASIC中心 1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟域带来的亚稳态、采样丢失、潜在逻辑错误等等一系列问题处理不当,将导致系统无法运行。本文总结出了几种同步策略来解决跨时钟域问题。 2 异步设计中的亚稳态 触发器是FPGA设计中最常用的基本器件。触发器工作过程中存在数据的建立(setup)和保持(hold)时间。对于使用上升沿触发的触发器来说,建立时间就是在时钟上升沿到来之前,触发器数据端数据保持稳定的最小时间。而保持时间是时钟上升沿到来之后,触发器数据端数据还应该继续保持稳定的最小时间。我们把这段时间成为setup-hold时间(如图1所示)。在这个时间参数内,输入信号在时钟的上升沿是不允许发生变化的。如果输入信号在这段时间内发生了变化,输出结果将是不可知的,即亚稳态 (Metastability) 图1 一个信号在过渡到另一个时钟域时,如果仅仅用一个触发器将其锁存,那么采样的结果将可能是亚稳态。这也就是信号在跨时钟域时应该注意的问题。如图2所示。 信号dat经过一个锁存器的输出数据为a_dat。用时钟b_clk进行采样的时候,如果a_dat正好在b_clk的setup-hold时间内发生变化,此时b_ dat就既不是逻辑"1",也不是逻辑"0",而是处于中间状态。经过一段时间之后,有可能回升到高电平,也有可能降低到低电平。输出信号处于中间状态到恢复为逻辑"1"或逻辑"0"的这段时间,我们

15.2 电流和电路同步练习及答案

第二节电流和电路 [基础知识] 1. 电流:电荷的形成电流。 2. 物理学规定:定向移动的方向为电流的方向。金属中电流的方向与内部自由电子的移动方向。 3. 得到持续电流的条件:和。 4. 电源是提供的装置。电源外部的电流方向是从极流向极。 5. 把电源、、用导线连接起来组成的电流的路径叫电路。 6. 开关控制电路的,起着控制的作用。 7. 用规定的符号表示电路连接情况的图叫。 8. 用符号表示:两节干电池:;开关:;灯泡:。 9. 电路的三种状态:通路、和断路;其中短路又分为短路和 短路两种。 [基础训练] 一、填空题 1. 一个完整的电路是由提供电能的、消耗电能的、控制电路通断的和提供电的流动路径的四部分组成。 2.电路中的电流是由电子的形成的,电流是有方向的,其方向就是沿着“电源的正极过到电源的负极”的方向。 3.同学们在连接实物电路时,开关应。 4.任何情况下都绝对不允许不经过而直接将电源两极连接在一起。5.我们平常所说的“把灯开开”,实际是将电路中的开关______,使电路形成______。 6.如图所示,要使灯EL A发光,EL B不发光,则应闭合电键__________,断开电键_______;若要使EL A不发光,EL B发光,则应闭合电键__________,断开电键_______;如果电键SA1和SA3闭合,SA2断开,则灯EL A_______、灯EL B_______。(填“亮”或“不亮”)

7.如图所示,A、B两处分别接有电铃和电池组,要求:电键闭合时,电灯亮,电铃同时响;电键断开时,电灯不亮,电铃不响,则电铃应接在______处,电池组应接在处。 8.干电池的锌筒是_____极,中央碳棒是_____极。用导线把灯泡连接到干电池的两极间时,导线中电流方向是从干电池的____ 极流向____ 极。 9.使用干电池的时候,决不允许用导线直接把_______连接起来,因为那样做_______太大,会损坏干电池。这种情况叫做__________。 10.如图所示的电路中,通过小灯泡中的电流方向是_______,通过小灯泡的自由电子定向移动方向是_______(选填“向左”或“向右“)。 二、选择题 11.在图中,要使电灯EL2、EL3亮,必须闭合的电键是( ) A.SA3 B.SA2、SA3 C. SA1、SA3 D.SA l、SA2、SA3

基于FPGA位同步时钟提取方案的设计

一种基于FPGA的新型位同步时钟提取方案及实现2 位同步时钟提取方案的原理 本文设计的方案可以从异步串行码流中提取位同步时钟信号,设计思想的基本出发点是在外部码流(code_in)的上升沿和本地时钟(clk)上跳沿相比较无非两 种 情 况, 如图1和图2所示: 图1 码流滞后于本地时钟△T示意图图2 码流超前于本地时钟△T示意图 从码流上跳沿的角度来看,若将码流code_in与本地时钟clk进行逻辑相与,若相与结果为“1”则说明码流滞后于本地时钟,若为“0”则说明码流超前于本地时钟。用VHDL语言描述为: if (code_in’event and code_in=’1’) then if (code_in and clk)=’1’ then q<=’1’ else q<=’0’ end if end if 程序中输出信号q可作为控制电路的输入信号。 本设计方案的系统框图如图3所示: 框图中,鉴相器作用是鉴别出码流和本地时钟的相位超前滞后关系,控制计数器采用双向计数器,鉴相器输出q作为控制计数器的计数方向输入,q为1则向上计数,q为0则向下计数。控制计数器的计数输出用来控制相位调整选择模块的选择端。相位调整选择模块由相位调整和相位选择功能。 图3 系统功能框图 3 设计实现

依据图3系统功能框图,利用Altera 公司的Quartus II 设计软件,采用自顶向下的模块化设计方法,用VHDL 语言和电路原理图混合输入设计对位同步时钟提取电路的各个部件分别进行设计。 本设计方案的鉴相器原理相对简单,不需要用VHDL语言设计,仅用两个 与门和一个D触发器就可以实 现,如图4 所示。图中的 的第二个与门(inst23)是为了实现D 触发器的时钟输入端与数据输入端 同步。 控制计数器设计使用Quartus II的MegaWizard Plug_In Manager工具来实现一个简单 的双向 数器,计数方向由鉴相器输出q控 制,q为1则计数器向上计数,q为0则计数器向下计数,计数系数由Count Modulus设定,设定的数值要求等于分频器的分频系数N。在原理图输入时可以任意改变分频器的分频系数和计数器的计数系数。 分频器设计输出时钟信号的占空比为50%,且分频系数N可调,用VHDL 语言实现并由软件自动生成元件符号供原理图调用,如图5所示。 下面给出分频器的VHDL语言关键描述语句 if(clk'event and clk='1') then if(count=N-1)then --计数周期 count<=0; else count<=count+1; if count<(integer(N/2)) then --产生分频脉冲 outclk<='0'; else outclk<='1'; end if; end if; end if; 相位调整选择模块的相位调整功能可以用延迟方式实现。在FPGA中要产生延时,信号必须经过一定的物理资源。在硬件描述语言中有关键词Wait for xx ns,需要说明的是该语法是仅仅用于仿真而不能用于综合的,可综合的延时方法有: (1)使信号经过逻辑门得到延时(如非门); (2) 使用器件提供的延时单元(如Altera公司的LCELL); (3)使用移位寄存器。 由于当使用多级非门的时候综合器往往会将其优化掉,因为综合器会认为一个信号非两次还是它自己,而且门延迟时间相对于具体器件是不固定的,LCELL延时单元也可以用来产生一定的延时,但这样形成的延时在FPGA芯片中并