全集成低相位噪声LC压控振荡器设计

全集成低相位噪声LC压控振荡器设计

刘颖异;王志功;钱照华

【期刊名称】《中国集成电路》

【年(卷),期】2008(017)003

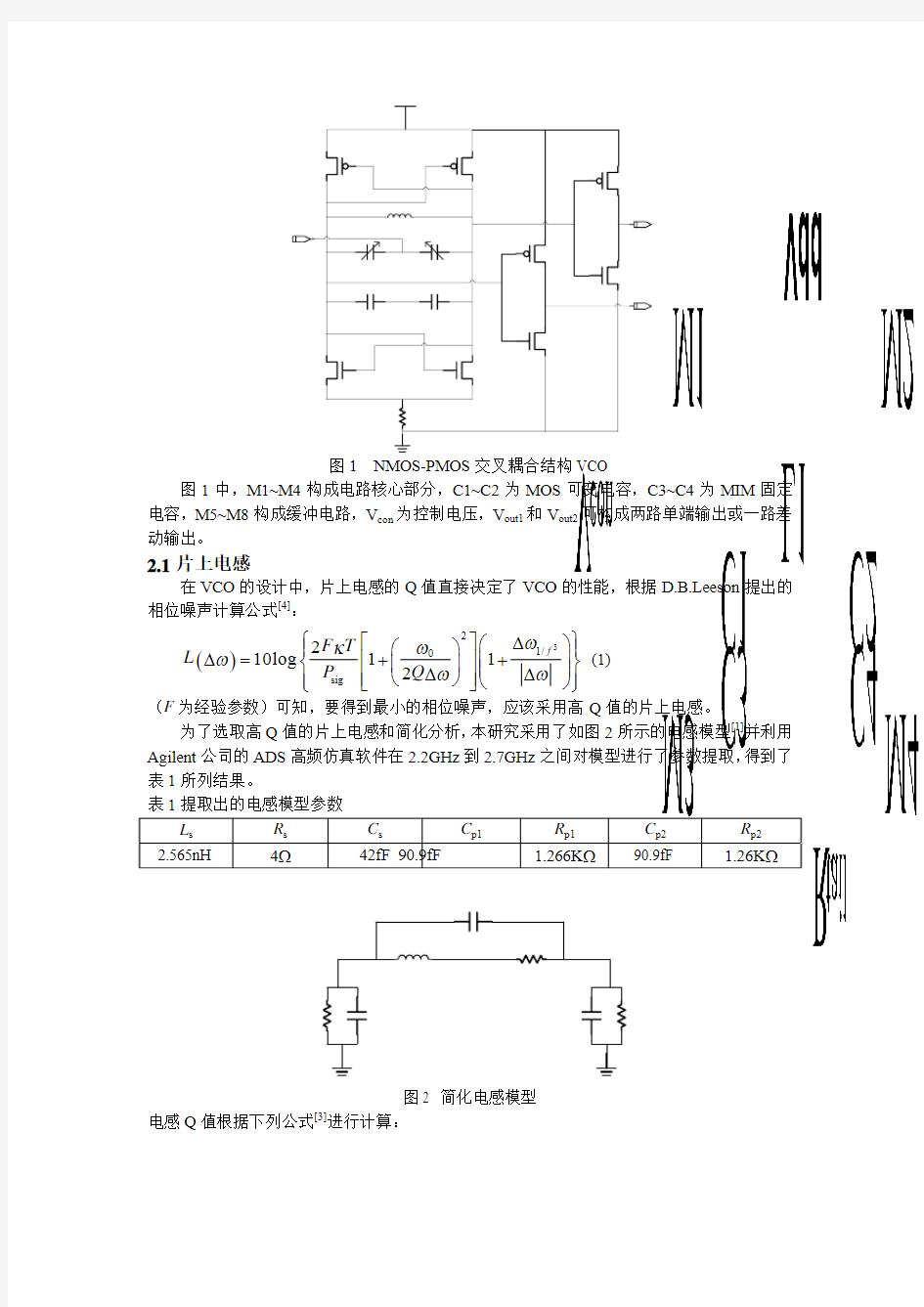

【摘要】提出了一种应用于ISM频段的低相位噪声LC VCO.电路采用TSMC 0.18μm 1P6M混合信号CMOS工艺进行设计,芯片版图面积740μm×700μm.在电源电压为1.8V时,后仿真结果表明,电路工作频率为2.4GHz时,调谐范围为23%.在偏离中心频率1MHz处,相位噪声为-124.2dBc/Hz.核心部分功耗约为7.56mW.

【总页数】5页(45-48,52)

【关键词】压控振荡器;片上电感;Q值;相位噪声;CMOS工艺

【作者】刘颖异;王志功;钱照华

【作者单位】东南大学射频集成电路与系统教育部工程研究中心,江苏南京,210096;东南大学射频集成电路与系统教育部工程研究中心,江苏南京,210096;东南大学射频集成电路与系统教育部工程研究中心,江苏南京,210096

【正文语种】中文

【中图分类】TN4

【相关文献】

1.全集成低功耗低相位噪声差分LC压控振荡器设计 [J], 姚志健; 马成炎; 叶甜春; 乐建连

2.LC低相位噪声压控振荡器设计与仿真 [J], 王欢

相关主题