运放差分

差分放大电路

一. 实验目的:

1. 掌握差分放大电路的基本概念;

2. 了解零漂差生的原理与抑制零漂的方法; 3. 掌握差分放大电路的基本测试方法。 二. 实验原理:

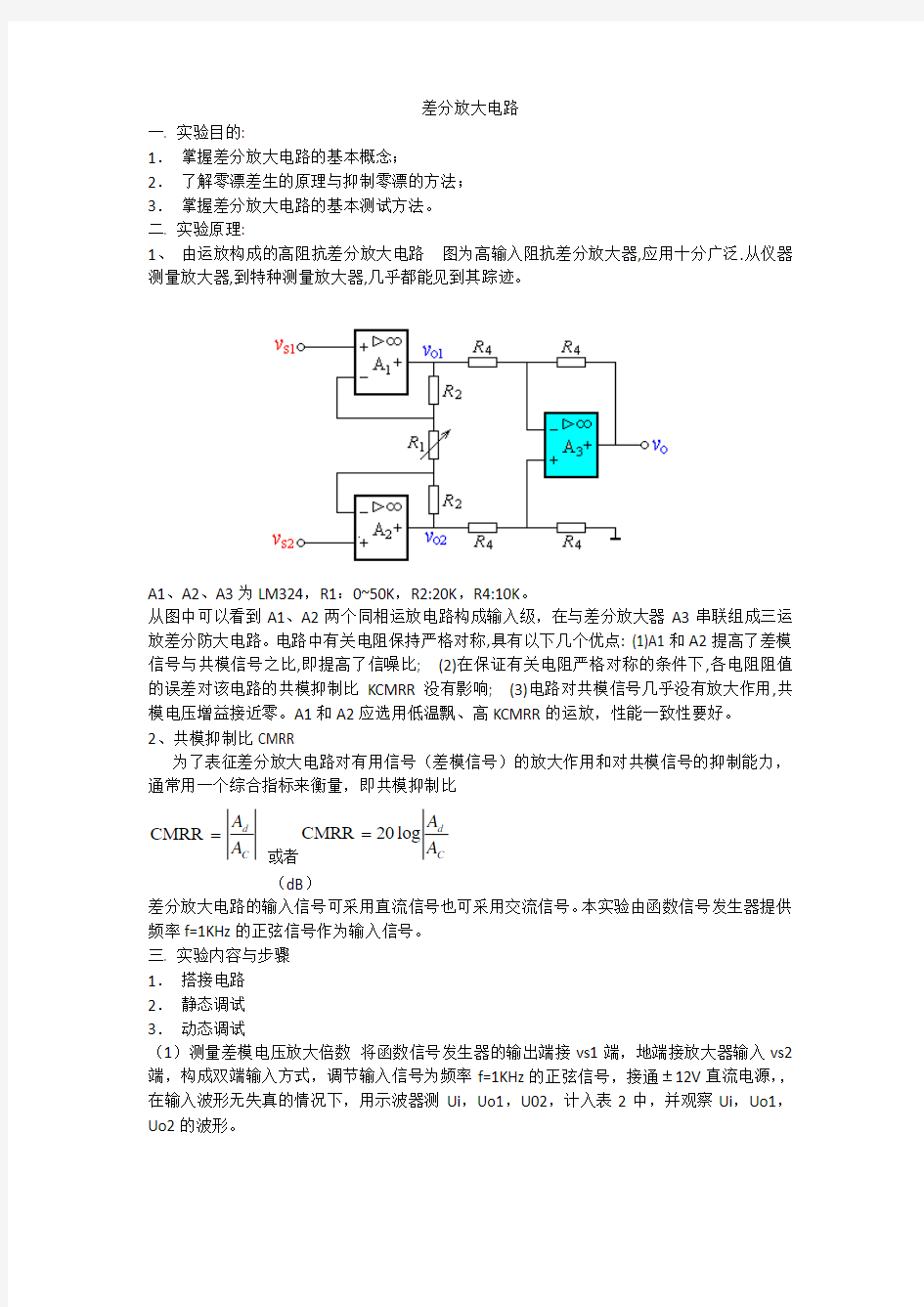

1、 由运放构成的高阻抗差分放大电路 图为高输入阻抗差分放大器,应用十分广泛.从仪器测量放大器,到特种测量放大器,几乎都能见到其踪迹。

A1、A2、A3为LM324,R1:0~50K ,R2:20K ,R4:10K 。

从图中可以看到A1、A2两个同相运放电路构成输入级,在与差分放大器A3串联组成三运放差分防大电路。电路中有关电阻保持严格对称,具有以下几个优点: (1)A1和A2提高了差模信号与共模信号之比,即提高了信噪比; (2)在保证有关电阻严格对称的条件下,各电阻阻值的误差对该电路的共模抑制比KCMRR 没有影响; (3)电路对共模信号几乎没有放大作用,共模电压增益接近零。A1和A2应选用低温飘、高KCMRR 的运放,性能一致性要好。 2、共模抑制比CMRR

为了表征差分放大电路对有用信号(差模信号)的放大作用和对共模信号的抑制能力,通常用一个综合指标来衡量,即共模抑制比

C d

A A =

CMRR 或者

C d

A A log 20CMRR = (d

B )

差分放大电路的输入信号可采用直流信号也可采用交流信号。本实验由函数信号发生器提供频率f=1KHz 的正弦信号作为输入信号。 三. 实验内容与步骤 1. 搭接电路 2. 静态调试 3. 动态调试

(1)测量差模电压放大倍数 将函数信号发生器的输出端接vs1端,地端接放大器输入vs2端,构成双端输入方式,调节输入信号为频率f=1KHz 的正弦信号,接通±12V 直流电源,,在输入波形无失真的情况下,用示波器测Ui ,Uo1,U02,计入表2中,并观察Ui ,Uo1,Uo2的波形。

表1

输入方式,调节输入信号在输出电压无失真的情况下,,用示波器测Ui,Uo1,U02,计入表2中,并观察Ui,Uo1,Uo2的波形。

运放差分放大电路

差分放大电路 一. 实验目的: 1. 掌握差分放大电路的基本概念; 2. 了解零漂差生的原理与抑制零漂的方法; 3. 掌握差分放大电路的基本测试方法。 二. 实验原理: 1. 由运放构成的高阻抗差分放大电路 图为高输入阻抗差分放大器,应用十分广泛.从仪器测量放大器,到特种测量放大器,几乎都能见到其踪迹。 从图中可以看到A1、A2两个同相运放电路构成输入级,在与差分放大器A3串联组成三运放差分防大电路。电路中有关电阻保持严格对称,具有以下几个优点: (1)A1和A2提高了差模信号与共模信号之比,即提高了信噪比; (2)在保证有关电阻严格对称的条件下,各电阻阻值的误差对该电路的共模抑制比K CMRR 没有影响; (3)电路对共模信号几乎没有放大作用,共模电压增益接近零。 因为电路中R1=R2、 R3=R4、 R5=R6 ,故可导出两级差模总增益为: 3 5P 1p i2i1o vd R R R 2R R u u u A ???? ??+-=-= 通常,第一级增益要尽量高,第二级增益一般为1~2倍,这里第一级选择100倍,第二级为1倍。则取R3=R4=R5=R6=10K Ω,要求匹配性好,一般用金属膜精密电阻,阻值可在10K Ω~几百K Ω间选择。则 A vd =(R P +2R 1)/R P 先定R P ,通常在1K Ω~10K Ω内,这里取R P =1K Ω,则可由上式求得R 1=99R P /2=49.5K Ω 取标称值51K Ω。通常R S1和R S2不要超过R P /2,这里选R S1= R S2=510,用于保护运放输入级。 A1和A2应选用低温飘、高K CMRR 的运放,性能一致性要好。 三. 实验内容 1. 搭接电路 2. 静态调试

差分-运放-运算放大器

差分接法:差分放大电路(图3.8a.4)的输入信号是从集成运放的反相和同相输入端引入,如果反馈电阻RF等于输入端电阻R1 ,输出电压为同相输入电压减反相输入电压,这种电路也称作减法电路。 图3.8a.4 差分放大电路 差分放大器 如图所示,通过采用两个输入,该差分放大器产生的输出等于U1和U2之差乘以增益系数

运算放大器的单电源供电方法 大部分运算放大器要求双电源(正负电源)供电,只有少部分运算放大器可以在单电源供电状态下工作,如LM358(双运放)、LM324(四运放)、CA3140(单运放)等。需要说明的是,单电源供电的运算放大器不仅可以在单电源条件下工作,也可在双电源供电状态下工作。例如,LM324可以在、+5~+12V单电源供电状态下工作,也可以在+5~±12V双电源供电状态下工作。 在一些交流信号放大电路中,也可以采用电源偏置电路,将静态直流输出电压降为电源电压的一半,采用单电源工作,但输入和输出信号都需要加交流耦合电容,利用单电源供电的反相放大器如图1(a)所示,其运放输出波形如图1(b)所示。 该电路的增益Avf=-RF/R1。R2=R3时,静态直流电压Vo(DC)=1/2Vcc。耦合电容Cl和C2的值由所需的低频响应和电路的输入阻抗(对于C1)或负载(对于C2)来确定。Cl及C2可由下式来确定:C1=1000/2πfoRl(μF);C2=1000/2πfoRL(μF),式中,fo是所要求最低输入频率。若R1、RL单位用kΩ,fO用Hz,则求得的C1、C2单位为μF。一般来说,R2=R3≈2RF。 图2是一种单电源加法运算放大器。该电路输出电压Vo=一RF(V1/Rl十V2/R2十V3/R3),若R1=R2=R3=RF,则Vo=一(V1十V2十V3)。需要说明的是,采用单电源供电是要付出一定代价的。它是个甲类放大器,在无信号输入时,损耗较大。

采用折叠式结构的两级全差分运算放大器的设计

目录 1. 设计指标 (1) 2. 运算放大器主体结构的选择 (1) 3. 共模反馈电路(CMFB)的选择 (1) 4. 运算放大器设计策略 (2) 5. 手工设计过程 (2) 5.1 运算放大器参数的确定 (2) 5.1.1 补偿电容Cc和调零电阻的确定 (2) 5.1.2 确定输入级尾电流I0的大小和M0的宽长比 (3) 5.1.3 确定M1和M2的宽长比 (3) 5.1.4确定M5、M6的宽长比 (3) 5.1.5 确定M7、M8、M9和M10宽长比 (3) 5.1.6 确定M3和M4宽长比 (3) 5.1.7 确定M11、M12、M13和M14的宽长比 (4) 5.1.8 确定偏置电压 (4) 5.2 CMFB参数的确定 (4) 6. HSPICE仿真 (5) 6.1 直流参数仿真 (5) 6.1.1共模输入电压范围(ICMR) (5) 6.1.2 输出电压范围测试 (6) 6.2 交流参数仿真 (6) 6.2.1 开环增益、增益带宽积、相位裕度、增益裕度的仿真 (6) 6.2.2 共模抑制比(CMRR)的仿真 (7) 6.2.3电源抑制比(PSRR)的仿真 (8) 6.2.4输出阻抗仿真 (9) 6.3瞬态参数仿真 (10) 6.3.1 转换速率(SR) (10) 6.3.2 输入正弦信号的仿真 (11) 7. 设计总结 (11) 附录(整体电路的网表文件) (12)

采用折叠式结构的两级全差分运算放大器的设计 1. 设计指标 5000/ 2.5 2.551010/21~22v DD SS L out dias A V V V V V V GB MHz C pF SR V s V V ICMR V P mW μ>==?== >=±=?≤的范围 2. 运算放大器主体结构的选择 图1 折叠式共源共栅两级运算放大器 运算放大器有很多种结构,按照不同的标准有不同的分类。从电路结构来看, 有套筒 式共源共栅、折叠式共源共栅、增益提高式和一般的两级运算放大器等。本设计采用的是如图1所示的折叠式共源共栅两级运算放大器,采用折叠式结构可以获得很高的共模输入电压范围,与套筒式的结构相比,可以获得更大的输出电压摆幅。 由于折叠式共源共栅放大器输出电压增益没有套筒式结构电压增益那么高,因此为了得到更高的增益,本设计采用了两级运放结构,第一级由M0-M10构成折叠式共源共栅结构,第二级由M11-M14构成共源级结构,既可以提高电压的增益,又可以获得比第一级更高的输出电压摆幅。 为了保证运放在闭环状态下能稳定的工作,本设计通过米勒补偿电容Cc 和调零电阻Rz 对运放进行补偿,提高相位裕量! 另外,本文设计的是全差分运算放大器,与单端输出的运算放大器相比较,可以获得更高的共模抑制比,避免镜像极点及输出电压摆幅。 3. 共模反馈电路(CMFB )的选择 由于采用的是高增益的全差分结构,输出共模电平对器件的特性和失配相当敏感,而且不能通过差动反馈来达到稳定,因此,必须增加共模反馈电路(CMFB )来检测两个输出端

集成运算放大器及其应用

第九章集成运算放大器及其应用(易映萍) 9.1 差分放大电路 9.2互补功率放大电路 9.3 集成运算放大电路 9.4 理想集成运放的线性运用电路 9.5 理想集成运放的非线性运用电路 习题 第九章集成运算放大器及其应用 9.1 差分放大电路 9.1.1 直接耦合多级放大电路的零点漂移现象 工业控制中的很多物理量均为模拟量,如温度、流量、压力、液面和长度等,它们通过不同的传感器转化成的电量也均为变化缓慢的非周期性连续信号,这些信号具有以下两个特点: 1.信号比较微弱,只有通过多级放大才能驱动负载; 2.信号变化缓慢,一般采用直接耦合多级放大电路将其放大。 u=0)时,人们在试验中发现,在直接耦合的多级放大电路中,即使将输入端短路(即 i u≠0),这种现象称为零点漂移(简称为零漂),如图输出端还会产生缓慢变化的电压(即 o 9.1所示。 (a)测试电路(b)输出电压u o的漂移 图9.1 零点漂移现象 9.1.2 零漂产生的主要原因 在放大电路中,任何参数的变化,如电源电压的波动、元件的老化以及半导体元器件参数随温度变化而产生的变化,都将产生输出电压的漂移,在阻容耦合放大电路中,耦合电容对这种缓慢变化的漂移电压相当于开路,所以漂移电压将不会传递到下一级电路进一步放

大。但是,在直接耦合的多级放大电路中,前一级产生的漂移电压会和有用的信号(即要求放大的输入信号)一起被送到下一级进一步放大,当漂移电压的大小可以和有用信号相当时,在负载上就无法分辨是有效信号电压还是漂移电压,严重时漂移电压甚至把有效信号电压淹没了,使放大电路无法正常工作。 采用高质量的稳压电源和使用经过老化实验的元件就可以大大减小由此而产生的漂移,所以由温度变化所引起的半导体器件参数的变化是产生零点漂移现象的主要原因,因而也称零点漂移为温度漂移,简称温漂,从某种意义上讲零点漂移就是静态工作点Q点随温度的漂移。 9.1.3抑制温漂的方法 对于直接耦合多级放大电路,如果不采取措施来抑制温度漂移,其它方面的性能再优良,也不能成为实用电路。抑制温漂的方法主要由以下几种: (1)采用稳定静态工作的分压式偏置放大电路中Re的负反馈作用; (2)采用温度补偿的方法,利用热敏元件来抵消放大管的变化; (3)采用特性完全相同的三极管构成“差分放大电路”; 9.1.4 差分放大电路 差分放大电路是构成多级直接耦合放大电路的基本单元电路。直接耦合的多级放大电路的组成框图如图9.2所示。 图9.2 多级放大的组成框图 A倍后传送到负载上,对电路造从上图可知输入级一旦产生了温漂,会经中间级放大 u2 A≈1,对电路造成的成严重的影响,而中间级产生的温漂,由于直接到达功放级而功放的 u 影响跟输入级相比少得多,所以,我们主要应设法抑制输入级产生的温漂,故在直接耦合的多级放大电路中只有输入级常采用差分放大电路的形式来抑制温漂。 9.1.4.1 差分放大电路的组成及结构特点 一.电路组成 差分放大电路如图9.3所示。

差分运算放大器基本知识

一.差分信号的特点: 图1 差分信号 1.差分信号是一对幅度相同,相位相反的信号。差分信号会以一个共模信号 V ocm 为中心,如图1所示。差分信号包含差模信号和公模信号两个部分, 差模与公模的定义分别为:Vdiff=(V out+-V out- )/2,Vocm=(V out+ +V out- )/2。 2.差分信号的摆幅是单端信号的两倍。如图1,绿色表示的是单端信号的摆 幅,而蓝色表示的是差分信号的摆幅。所以在同样电源电压供电条件下,使用差分信号增大了系统的动态范围。 3.差分信号可以抑制共模噪声,提高系统的信噪比。In a differential system, keeping the transport wires as close as possible to one another makes the noise coupled into the conductors appear as a common-mode voltage. Noise that is common to the power supplies will also appear as a common-mode voltage. Since the differential amplifier rejects common-mode voltages, the system is more immune to external noise. 4.差分信号可以抑制偶次谐波,提高系统的总谐波失真性能。 Differential systems provide increased immunity to external noise, reduced even-order harmonics, and twice the dynamic range when compared to signal-ended system. 二.分析差分放大器电路 图2.差分放大器电路分析图

全差分运算放大器设计

全差分运算放大器设计 岳生生(200403020126) 一、设计指标 以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下: ?直流增益:>80dB ?单位增益带宽:>50MHz ?负载电容:=5pF ?相位裕量:>60度 ?增益裕量:>12dB ?差分压摆率:>200V/us ?共模电压:2.5V (VDD=5V) ?差分输入摆幅:>±4V 二、运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT N V 之和小于0.5V ,输出端的所有PMOS 管的,DSAT P V 之和也必须小于0.5V 。对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该 要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 三、性能指标分析 1、 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 11 1357 113 51 3 57 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=-+ 第二级增益 9 2 2 9112 9 9 11 ()m o o o m m o o g g G A R r r g g =-=-=- + 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r = = ≥++ 2、 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR :

实验课7 全差分运放的仿真方法

CMOS模拟集成电路 实验报告

实验课7 全差分运放的仿真方法 目标: 1、了解全差分运放的各项指标 2、掌握全差分运放各项指标的仿真方法,对全差分运放的各指标进行仿真,给出各指标的 仿真结果。 本次实验课使用的全差分运放 首先分析此电路图,全差分运算放大器是一种具有差分输入,差分输出结构的运算放大器。其相对于单端输出的放大器具有一些优势:因为当前的工艺尺寸在减少,所以供电的电源电压越来越小,所以在供电电压很小的情况下,单端输出很难理想工作,为了电路有很大的信号摆幅,采用类似上图的全差分运算放大器,其主要由主放大器和共模反馈环路组成。 1、开环增益的仿真 得到的仿真图为

1.开环增益:首先开环增益计算方法是低频工作时(<200Hz) ,运放开环放大倍数;通过仿真图截点可知增益为73.3db。 2.增益带宽积:随着频率的增大,A0会开始下降,A0下降至0dB 时的频率即为GBW,所以截取其对应增益为0的点即可得到其增益带宽积为1.03GB。 3.相位裕度:其计算方法为增益为0的时候对应的VP的纵坐标,如图即为-118,则其相位裕度为-118+180=62,而为保证运放工作的稳定性,当增益下降到0dB 时,相位的移动应小于180 度,一般取余量应大于60度,即相位的移动应小于120 度;所以得到的符合要求。 在做以上仿真的时候,关键步骤 在于设定VCMFB,为了得到大的增益,并且使相位裕度符合要求,一直在不停地改变VCMFB,最初只是0.93,0.94,0.95的变化,后来发现增益还是远远不能满足要求,只有精确到小数点后4为到5位才能得到大增益。 2.CMRR 的仿真 分析此题可得共模抑制比定义为差分增益和共模增益的比值,它反映了一个放大器对于共模信号和共模噪声的抑制能力。因此需要仿真共模增益和差分增益。可以利用两个放大器,一 个连成共模放大,一个连成差模放大,

全差分套筒式运算放大器设计

全差分套筒式运算放大器设计 1、设计内容 本设计基于经典的全差分套筒式结构设计了一个高增益运算放大器,采用镜像电流源作为偏置。为了获得更大的输出摆幅及差模增益,电路采用了共模反馈及二级放大电路。 本设计所用到的器件均采用SMIC 0.18μm的工艺库。 2、设计要求及工艺参数 本设计要实现的各项指标和相关的工艺参数如表1和表2所示:

3、放大器设计 3.1 全差分套筒式放大器拓扑结构与实际电路 图1 全差分套筒式放大器拓扑结构 图2 最终电路图

3.2 设计过程 在图1中,Mb1和M9组成的恒流源为差放提供恒流源偏置,且M1,M2完全一样,即两管子所有参数均相同。Mb2、M7和M8构成了镜像电流源,M5、M6和M7、M8构成了共源共栅电流源,M1、M2、M3、M4构成了共源共栅结构,可以显著提高输出阻抗,提高放大倍数(把M3的输出阻抗提高至原来的(gm3 + gmb3)ro2倍。但同时降低了输出电压摆幅。为了提高摆幅,控制增益,在套筒式差分放大器输出端增加二级放大。 本设计中功率上限为10mW,可以给一级放大电路分配3mA的电流。设计要求摆幅为3V,所以图1中M1、M3、M5、M9的过驱动电压之和不大于1.8-3/2=0.3V。我们可以平均分配每个管子的过驱动电压。根据漏电计算流公式(1)(考虑沟道长度调制效应),可以计算出每个管子的宽长比。 I D=1 2μn C ox W L (V GS?V TH)2(1+λV DS)(1) 其中,C ox等于ε/t ox,μn和t ox可以从工艺库中查找。 4、仿真结果 经过调试优化之后的仿真结果如以下各图所示: 图3 增益及相位裕度 从图中可以看出,本设计的低频增益达到了74.25dB,达到了预期要求。3dB 带宽为35kHz左右,比较小,可见设计还有改进的余地。 当CL为2pF时,相位裕度: PM=180°+∠βH(ω)=180°?125.5°=54.5° 电源电压为1.8V时,输出摆幅如下图所示,达到了3V。

运放差分放大电路原理知识介绍

差分放大电路 (1)对共模信号的抑制作用 差分放大电路如图所示。 特点:左右电路完全对称。 原理:温度变化时,两集电极电流增量相等,即C2C1I I ?=?,使集电极电压变化量相等,CQ2CQ1V V ?=?,则输出电压变化量0C2C1O =?-?=?V V V ,电路有效地抑制了零点漂移。若电源电压升高时,仍有0C2C1O =?-?=?V V V ,因此,该电路能有效抑制零漂。 共模信号:大小相等,极性相同的输入信号称为共模信号。 共模输入:输入共模信号的输入方式称为共模输入。 (2)对差模信号的放大作用 基本差分放大电路如图。 差模信号:大小相等,极性相反的信号称为差模信号。 差模输入:输入差模信号的输入方式称为差模输入。 在图中, I 2I 1I 2 1 v v v = -=, 放大器双端输出电压 差分放大电路的电压放大倍数为 可见它的放大倍数与单级放大电路相同。 (3)共模抑制比 共模抑制比CMR K :差模放大倍数d v A 与共模放大倍数c v A 的比值称为共模抑制比。 缺点:第一,要做到电路完全对称是十分困难的。第二,若需要单端输出,输出端的零点漂移仍能存在,因而该电路抑制零漂的优点就荡然无存了。 改进电路如图(b )所示。在两管发射极接入稳流电阻e R 。使其即有高的差模放大 倍数,又保持了对共模信号或零漂强抑制能力的优点。 在实际电路中,一般都采用正负两个电源供电,如图所示(c )所示。 差分放大电路 一. 实验目的: 1. 掌握差分放大电路的基本概念; 2. 了解零漂差生的原理与抑制零漂的方法; 3. 掌握差分放大电路的基本测试方法。 二. 实验原理: 1. 由运放构成的高阻抗差分放大电路 图为高输入阻抗差分放大器,应用十分广泛.从仪器测量放大器,到特种测量放大器,几乎都能见到其踪迹。

全差分运算放大器设计

全差分运算放大器设计 岳生生(0126) 一、设计指标 以上华CMOS 工艺设计一个全差分运算放大器,设计指标如下: 直流增益:>80dB 单位增益带宽:>50MHz 负载电容:=5pF 相位裕量:>60度 增益裕量:>12dB 差分压摆率:>200V/us 共模电压:(VDD=5V) 差分输入摆幅:>±4V 运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的 ,DSAT N V 之和小于,输出端的所有PMOS 管的 ,DSAT P V 之和也必须小于。对于单 级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 性能指标分析 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 1 1 1 3 5 7 1 1 3 5 1 3 5 7 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=- +P 第二级增益9 2 2 9 11 2 9 9 11 ()m o o o m m o o g g G A R r r g g =-=-=-+P 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r == ≥++ 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR : 1)、输入级: max 1max |2| Cc out DS C C d SR dt I v I C C = = = 单位增益带宽1m u C g C ω= ,可以得到 1m C u g C ω =

差分运放运算放大器

图3.8a.4 差分放大电路 差分放大器 如图所示,通过采用两个输入,该差分放大器产生的输出等于U1和U2之差乘以增益系数 运算放大器的单电源供电方法 大部分运算放大器要求双电源(正负电源)供电,只有少部分运算放大器可以在单电源供电状态下工作,如LM358(双运放)、LM324(四运放)、CA3140(单运放)等。需要说明的是,单电源供电的运算放大器不仅可以在单电源条件下工作,也可在双电源供电状态下工作。例如,LM324可以在、+5~+12V单电源供电状态下工作,也可以在+5~±12V双电源供电状态下工作。 在一些交流信号放大电路中,也可以采用电源偏置电路,将静态直流输出电压降为电源电压的一半,采用单电源工作,但输入和输出信号都需要加交流耦合电容,利用单电源供电的反相放大器如图1(a)所示,其运放输出波形如图1(b)所示。 该电路的增益Avf=-RF/R1。R2=R3时,静态直流电压Vo(DC)=1/2Vcc。耦合电容Cl和C2的值由所需的低频响应和电路的输入阻抗(对于C1)或负载(对于C2)来确定。Cl及C2可由下式来确定:C1=1000/2πfoRl(μF);C2=1000/2πfoRL(μF),式中,fo是所要求最低输入频率。若R1、RL单位用kΩ,fO用Hz,则求得的C1、C2单位为μF。一般来说,R2=R3≈2RF。 图2是一种单电源加法运算放大器。该电路输出电压Vo=一RF(V1/Rl十V2/R2十V3/R3),若R1=R2=R3=RF,则Vo=一(V1十V2十V3)。需要说明的是,采用单电源供电是要付出一定代价的。它是个甲类放大器,在无信号输入时,损耗较大。 思考题(1)图3是一种增益为10、输入阻抗为10kΩ、低频响应近似为30Hz、驱动负载为1kΩ的单电源反相放大器电路。该电路的不失真输入电压的峰—峰值是多少呢?(提示:一般运算放大器的典型输入、输

全差分运算放大器设计说明

全差分运算放大器设计 岳生生(6) 一、设计指标 以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下: ?直流增益:>80dB ?单位增益带宽:>50MHz ?负载电容:=5pF ?相位裕量:>60度 ?增益裕量:>12dB ?差分压摆率:>200V/us ?共模电压:2.5V (VDD=5V) ?差分输入摆幅:>±4V 二、运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT N V 之和小于0.5V ,输出端的所有PMOS 管的 ,DSAT P V 之和也必须小于0.5V 。对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该 要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 三、性能指标分析 1、 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 11135711 3 5 1 3 5 7 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=- +P 第二级增益 9 2 291129 9 11 ()m o o o m m o o g g G A R r r g g =-=-=- +P 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r == ≥++ 2、 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR :

三运放差分放大电路

三运放仪表放大线路设计(2010-5-12更新) 最近看到许多朋友在做一些小信号的放大,例如感应器的信号采集 这里仅仅提供一个设计方法和思路,在实际应用当考虑电源的杂讯以及一些Bypass的电容例如在LM324电源接一些100uF ,0.01uF 的电容,这些电容尽量靠近LM324 当然如果不是局限LM324的应用,市面上有许多这样兜售的零件例如TI的INA122,INA154 ADI的AD620,AD628等等,而且频带宽和噪声系数都很好 这些运放在放大的时候单级尽量不要超过40dB(100倍),避免噪声过大 这里设计的是理论值而已 举例设计: 设计一个仪表放大器其增益可以在1V/V

LM324 采用双电源,单信号输入,放大100倍 采用OP07之双电源,单信号输入,100倍

采用Lm324之单电源,单输入信号设计参考(输入信号切不可为零) #运算放大器

全差分两级放大电路

综合课程设计研究报告 课题名称:全差分两级运放 研究人员: 指导教师:王向展宁宁 201 年1月1日 微电子与固体电子学院

目录 一、绪论 (1) (一)研究工作的背景与意义 (1) (二)国内外现状分析 (1) 二、研究目标、研究内容与技术指标 (1) (一)研究目标 (2) (二)研究内容 (2) (三)关键技术 (2) (四)技术指标 (3) 三、电路工作原理 (3) (一)电路结构理论 (4) (二)关键电路模块 (4) (三)非理想效应 (5) 四、电路设计与仿真 (6) (一)电路设计方案 (6) (二)电路设计结构 (9) (三)电路仿真及结果 (10) 五、全文总结与展望 (12) 参考文献 (13)

一、绪论 (一)研究工作的背景与意义 随着模拟集成电路技术的发展,高速、高精度运算放大器得到广泛应用。全差分运算放大器在输入动态范围、抑制共模信号和噪声的能力等方面,较单端输出运放有很大优势,成为应用很广的电路单元。另外,全差分输出时的输出电压信号幅度比单端输出时增大一倍,这对低电源电压供电的现代CMOS电路尤为重要,因为这可以扩大输出信号的动态范围。因此,本文讨论并设计了满足一定要求的全差分运算放大器。 (二)国内外现状分析 从第一颗运算放大器IC问世到现在,运算放大器技术已经在半导体制造工艺和电路设计两方面取得了巨大进展。在大约40年的发展过程中,IC制造商们利用上述先进技术设计出了近乎“完美”的放大器。虽然什么是理想放大器很难有一个精确定义,但它却为模拟设计工程师提供了一个目标。理想放大器应该无噪声、具有无穷大增益、无穷大输入阻抗、零偏置电流以及零失调电压,它还应该不受封装尺寸限制,不占用空间。上述这些,都是许多教科书为了得到简单的传递函数而做出的种种假设。 未来放大器市场增长的驱动力主要有三方面:其一,便携式应用的低功耗要求将推动具有低操作电源电压/电流的放大器增长;其二,高分辨率应用需要能降低噪声和失真度的放大器;其三,由于性能和价格压力持续上扬,因此能够集成其他功能的放大器前景乐观。测试和测量、通信、医疗影像等领域的先进应用是提升放大器性能的主要驱动力;DSL和消费类视频应用是最大的市场,而且未来将继续此趋势。其中,DSL运放的增长点主要在于线路驱动器。而整合了滤波、多路技术以及DC恢复等功能的消费类视频放大器也被看好。从应用的角度讲,不同的系统对运放有不同要求,选择合适的运放对于系统设计至关重要。对于通信、高速测量仪表及超声波设备等高速应用,交流特性极为重要。但对于低速的高精度系统,直流方面的特性则通常更为重要。衡量系统在交流特性方面的参数有信号带宽、失真率、噪声等;而衡量系统在直流特性方面的参数有输入补偿电压、开环增益、输入偏置电流及共模抑制比等。

全差分CMOS运算放大器的设计毕业设计

CMOS运算放大器的设计

毕业设计(论文)原创性声明和使用授权说明 原创性声明 本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得及其它教育机构的学位或学历而使用过的材料。对本研究提供过帮助和做出过贡献的个人或集体,均已在文中作了明确的说明并表示了谢意。 作者签名:日期: 指导教师签名:日期: 使用授权说明 本人完全了解大学关于收集、保存、使用毕业设计(论文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在不以赢利为目的前提下,学校可以公布论文的部分或全部内容。 作者签名:日期:

学位论文原创性声明 本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。除了文中特别加以标注引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写的成果作品。对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。本人完全意识到本声明的法律后果由本人承担。 作者签名:日期:年月日 学位论文版权使用授权书 本学位论文作者完全了解学校有关保留、使用学位论文的规定,同意学校保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。本人授权大学可以将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。 涉密论文按学校规定处理。 作者签名:日期:年月日 导师签名:日期:年月日

5运算放大器(8版)

运算放大器 运放(operational amplifier)能对信号进行数学运算的放大电路。它曾是模拟计算机的基础部件,因而得名。采用集成电路工艺制做的运算放大器,除保持了原有的很高的增益和输入阻抗的特点之外,还具有精巧、廉价和可灵活使用等优点,因而在有源滤波器、开关电容电路、数-模和模-数转换器、直流信号放大、波形的产生和变换,以及信号处理等方面得到十分广泛的应用。 直流放大电路在工业技术领域中,特别是在一些测量仪器和自动化控制系统中应用非常广泛。如在一些自动控制系统中,首先要把被控制的非电量(如温度、转速、压力、流量、照度等)用传感器转换为电信号,再与给定量比较,得到一个微弱的偏差信号。因为这个微弱的偏差信号的幅度和功率均不足以推动显示或者执行机构,所以需要把这个偏差信号放大到需要的程度,再去推动执行机构或送到仪表中去显示,从而达到自动控制和测量的目的。因为被放大的信号多数变化比较缓慢的直流信号,分析交流信号放大的放大器由于存在电容器这样的元件,不能有效地耦合这样的信号,所以也就不能实现对这样信号的放大。能够有效地放大缓慢变化的直流信号的最常用的器件是运算放大器。运算放大器最早被发明作为模拟信号的运算(实现加减乘除比例微分积分等)单元,是模拟电子计算机的基本组成部件,由真空电子管组成。所用的运算放大器,是把多个晶体管组成的直接耦合的具有高放大倍数的电路,集成在一块微小的硅片上。

一、发展历史 第一个使用真空管设计的放大器大约在1930年前后完成,这个放大器可以执行加与减的工作。 1941年:由真空管组成的第一个运算放大器,由贝尔实验室的 Karl D. Swartzel Jr. 取得,名为“Summing Amplifier”(加算放大器),在二次大战时,该设计大量用于军用火炮导向装置中。 1947年:第一个具有非反向输入端的运算放大器由哥伦比亚大学的 John R. Ragazzini 教授在论文中提出,并提及他的学生随后会实际设计出具有重大改进的运算放大器 1949年:第一个使用截波稳定式(Chopper-stabilized)电路的运算放大器问世。 1961年:第一个由个别晶体管组成的运算电子放大器板组件 1962年:第一个胶封模组形式的运算放大器 1963年:第一个以集成电路单一芯片形式制成的运算放大器是快捷半导体Fairchild公司 Bob Widlar 所设计的μA702,一开始但还不算很成功,直到1965年经修改后推出μA709 1963年:首次作为商业产品贩售的运算放大器是 George A. Philbrick Researches (GAP/R) 公司的真空管运算放大器,型号 K2-W 1966年:第一个使用变容二极管桥(Varactor Bridge)电路的运算放大器诞生 1967年:美国国家半导体公司推出 LM101,改善了许多重要问题,使集成电路运算放大器开始流行 1968年:飞兆半导体公司推出μA741,与 LM101 相比,μA741内部增加了30pF的频率补偿电容。该产品第二来源众多,迄今仍然在生产使用,它是有史以来最成功的运算放大器,也是极少数最长寿的IC型号之一。 1970年:开始出现输入端使用FET的高速、低输入电流(高输入阻抗)运算放大器。 1972年:第一个可使用单电源供应的运算放大器 LM324 推出。 LM324 内含四个运算放大器,它的接脚排列方式也被随后的同类型运算放大器延用,成为业界标准。

全差分运放实验

两级CMOS全差分运算放大器的设计和仿真 (2) 1、软件的安装 (2) 1.1 Cadence orcad的安装 (2) 1.2 Hspice的安装 (2) 1.3Cosmos Scope的安装 (2) 2、实验要求 (2) 3、电路图手工计算 (3) 3.1 运放主结构计算 (3) 3.2 偏置电路 (5) 3.3 共模反馈电路 (7) 4、使用Orcad绘制电路图 (7) 5、电路仿真 (11) 6、仿真结果查看 (13) 7、其他性能参数的仿真 (15)

两级CMOS全差分运算放大器的设计和仿真 1、软件的安装 在该试验中要用到三个软件,分别为Cadence orcad(绘制电路图与网表提取工具),Hspice (电路仿真工具)和Cosmos Scope(仿真结果查看工具)。所有用到的软件安装程序均放在D盘EDA文件夹中。 1.1 Cadence orcad的安装 打开D盘中的\eda\OrCad9.23,点击Setup.exe,点击下一步,到输入Install Code步骤,打开Crack文件夹中的Install.tex文件,将Orcad Capture后面的码复制到Install Code里,然后点击下一步。直至安装完毕。 1.2 Hspice的安装 打开D盘eda\hspice_vA-2008.03,点击Hspice的安装程序进行安装,均点击下一步,直至安装结束。然后将该文件夹中的hspice2008.lic文件拷贝到C:\synopsys\Hspice_A-2008.03下。 右键点击电脑桌面我的电脑/属性/高级/环境变量/系统变量(如果只想让管理员用,则是administrator的用户变量)/新建/变量名lm_license_file 变量值就是license文件的路径,/hspice2008.lic,也就是变量值为C:\synopsys\Hspice_A-2008.03\hspice2008.lic 然后确定。 1.3Cosmos Scope的安装 打开D盘eda\cosmos2007\HSpice_CosmosScope_Z-2007.03-SP1_win,点击安装程序进行安装。 然后将eda\cosmos2007\hspice-license文件夹中的cosmos2007.dat文件拷贝到C:\synopsys\Z-2007.03-SP1文件加下。 右键点击电脑桌面我的电脑/属性/高级/环境变量/系统变量,点击刚才新建的变量,也就是lm_license_file,在先前输入的变量值后面,输入分号,然后输入C:\synopsys\Z-2007.03-SP1\cosmos2007.dat,也就是Hspice和Cosmos两者的变量值用分号隔开。 2、实验要求 在本实验中,要求所设计的运算放大器采用5V电源电压,负载电容为5pF,满足直流增益>80dB,单位增益带宽>20MHz,相位欲度大于60度,差分压摆率(slew rate)>100V/us。

阅读运算放大器电路图的方法

阅读运算放大器电路图的方法 时间:2010-04-17 23:13:09 来源:作者: 集成运算放大电路的一般组成及其单元结构,如恒流源电路、差分放大电路、CC-CE、CC-CB电路和互补输出电路等。 运算放大器主要由输入级、中间放大级、输出级和偏置电路等四部分组成,如图1所示。 图1 运算放大器的偏置电路与分立放大电路的偏置电路设计有很大不同,主要由各种形式的恒流源电路实现,熟悉各种形式的恒流源电路是阅读运放电路的基础。 运算放大器的输入级通常是差分放大电路,其主要功能是抑制共模干扰和温漂,双极型运放中差分管通常采用CC-CB复合管,以便拓展通频带; 运算放大器的中间级采用共射或共源电路,并采用恒流源负载和复合管以增加电压放大倍数。 双极型运算放大器的输出级采用互补输出形式,其主要功能是提高负载能力并增大输出电压和电流的动态范围。二只输出管轮流导通,每管工作在乙类状态。为消除交越失真,通常会给输出管提供适当的偏置电流,让其工作在甲乙类状态。 由于集成电路工艺的限制,各级之间采用直接耦合。为保证输入短路时,输出直流电平为零,有时还需要在级间加入电平移动电路。 运算放大器的读图过程如下: (1)运放电路结构分解 根据运放结构特点,将运放分解成输入级、中间级和输出级、基准电流源等四个基本部分。 (2)基准电流分析 运放电路中均有一个供偏置用的基准电流源,由它产生基准参考电流。 (3)静态偏置分析 在基准电流基础上,通过镜像直流电流或微镜像直流电流源,产生各种大小的直流恒流源或直流微恒流源,这些直流恒流源提供放大用晶体管的静态偏置。 将镜像直流源电路用等效恒流源代替,可以得到等效直流通路,用于分析各级直流偏置。 (4)交流分析

10种运算放大器

各种不同类型的运算放大器介绍 董婷 076112班一.uA741M,uA741I,uA741C(单运放)高增益运算放大器用于军事,工业和商业应用.这类单片硅集成电路器件提供输出短路保护和闭锁自由运作。这些类型还具有广泛的共同模式,差模信号范围和低失调电压调零能力与使用适当的电位。目前价格1元/个。 温度等级 uA741主要参数 ABSOLUTE MAXIMUM RATINGS最大额定值

ELECTRICAL CHARACTERISTICS VCC = ±15V, Tamb = +25°C (unless otherwise specified) 电气特性 虚拟通道连接= ±15V ,Tamb = 25 ℃(除非另有说明)

二.CA3140 高输入阻抗运算放大器 CA3140高输入阻抗运算放大器,是美国无线电公司研制开发的一种BiMOS高电压的运算放大器在一片集成芯片上,该CA3140A和CA3140 BiMOS运算放大器功能保护MOSFET的栅极(PMOS上)中的晶体管输入电路提供非常高的输入阻抗,极低输入电流和高速性能。操作电源电压从4V至36V(无论单或双电源),它结合了压电PMOS晶体管工艺和高电压双授晶体管的优点.(互补对称金属氧化物半导体)卓越性能的运放。主要运用于单电源放大器在汽车和便携式仪表,有源滤波器,比较器,采样保持放大器,长期定时器,光电仪表,探测器,TTL 接口,入侵报警系统,函数发生器,音调控制,电源,便携式仪器。工作范围为-55 oC—125 oC。目前生产厂家主要是INTERSIL公司和HARRIS公司,报价为:2.7—3元/个。 引脚图