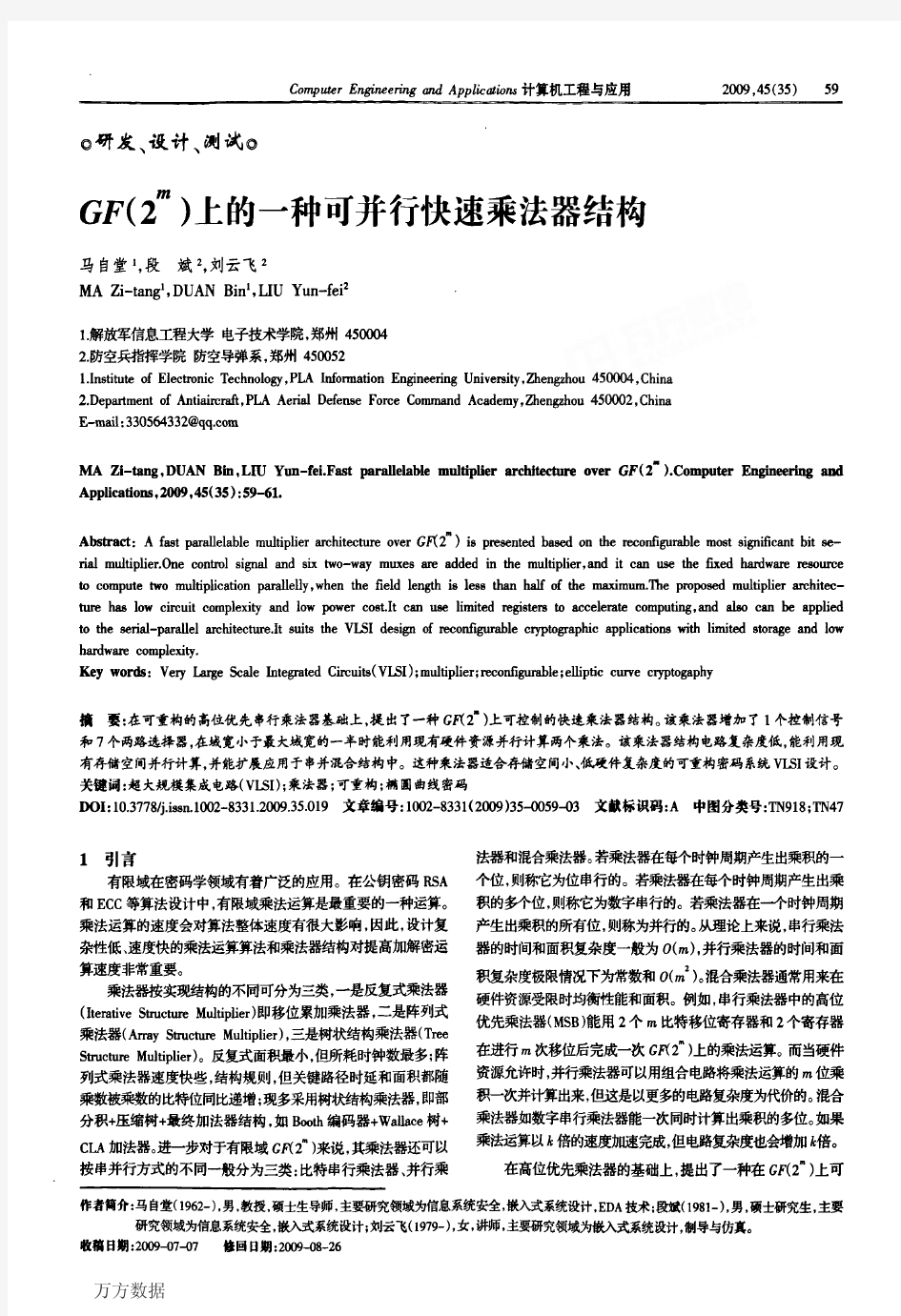

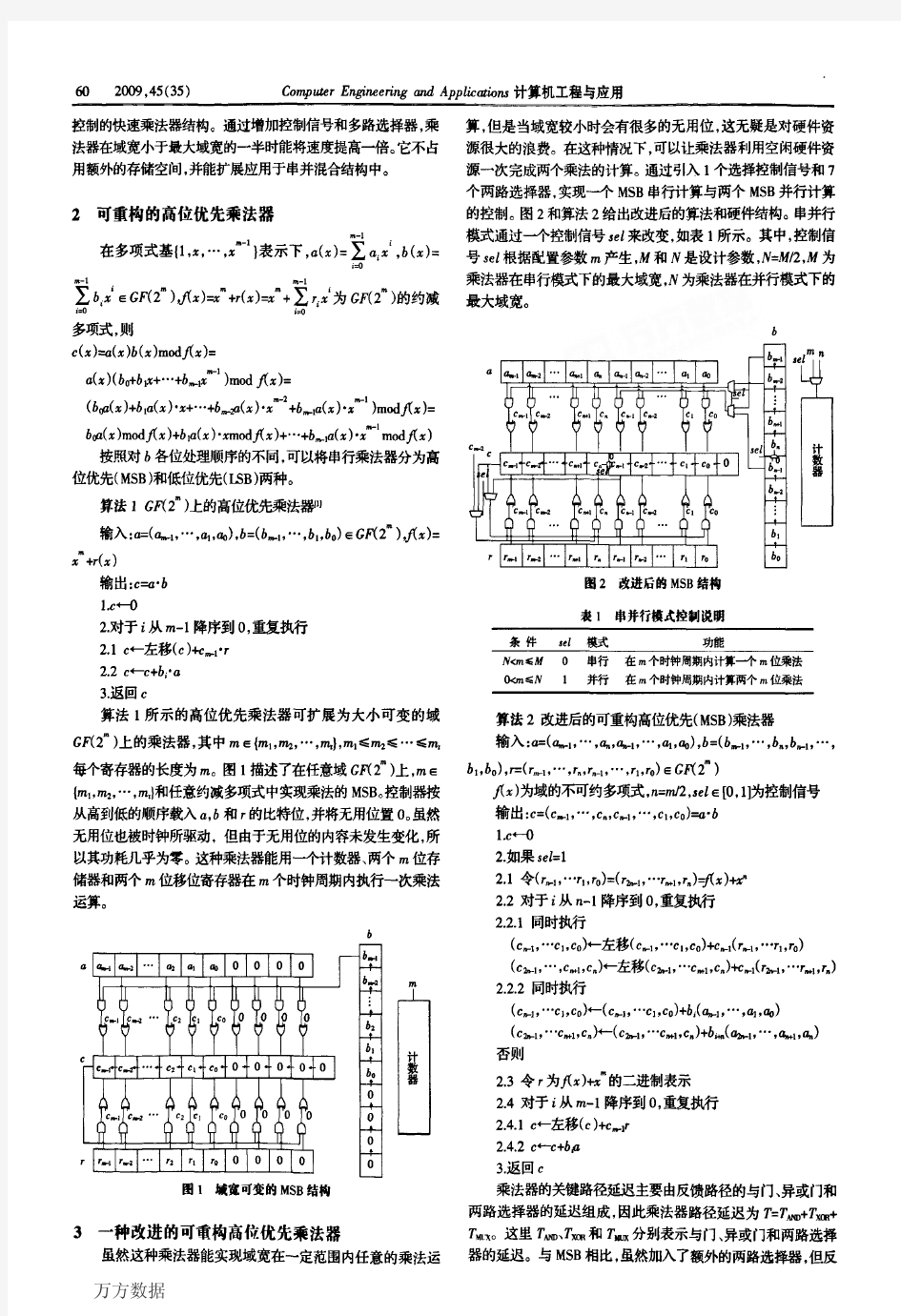

GF2m上的一种可并行快速乘法器结构

各种乘法器比较

各种乘法器比较 韦其敏08321050 引言:乘法器频繁地使用在数字信号处理和数字通信的各种算法中,并往往影响着整个系统的运行速度。如何实现快速高效的乘法器关系着整个系统的运算速度和资源效率。本位用如下算法实现乘法运算:并行运算、移位相加、查找表、加法树。并行运算是纯组合逻辑实现乘法器,完全由逻辑门实现;移位相加乘法器将乘法变为加法,通过逐步移位相加实现;查找表乘法器将乘积结果存储于存储器中,将操作数作为地址访问存储器,得到的输出数据就是乘法运算结果;加法树乘法器结合移位相加乘法器和查找表乘法器的优点,增加了芯片耗用,提高运算速度。 注:笔者使用综合软件为Quartus II 9.1,选用器件为EP2C70,选用ModelSim SE 6.1b进行仿真,对于其他的软硬件环境,需视具体情况做对应修改。 汇总的比较: 详细实现过程: 1.并行乘法器 源代码: module Mult1(outcome,a,b); parameter MSB=8; input [MSB:1] a,b; output [2*MSB:1] outcome; assign outcome=a*b; endmodule

资源耗用情况: ModelSim测试激励文件源代码:`timescale 10ns/1ns module Mult1_test(); reg [8:1] a,b; wire [16:1] outcome; Mult1 u1(outcome,a,b); parameter delay=2; initial begin a=1; b=0; end initial forever begin #delay a=a+1; b=b+1; if(outcome>=16'h0FFF) $stop;

乘法器

课程设计任务书 题目基于FPGA的6*6串行乘法器设计起讫日期 学生姓名专业班级通信工程 所在院系电气信息学院 指导教师职称 所在单位通信工程教研室

任务及要求: 1.设计内容和要求(包括设计内容、主要指标与技术参数) 设计内容:设计一个6*6串行乘法器 设计要求: (1)设计语言为Verilog,仿真软件为ISE自带仿真软件iSIM; (2)该设计不要求下载到硬件开发板上,只需给出仿真波形图,但要求能够从波形图 中看出实现了乘法运算 2.原始依据 本设计要求学生应用Xilinx FPGA设计一个6*6串行乘法器,通过设计能够让学生进一步掌握FPGA的基本开发流程,同时提高时序设计能力,学生已学习过EDA课程,掌握硬件描述语言基本知识,通过本次设计可进一步提高学生的动手能力,加强理论联系实际的能力。 3.进度计划 3.4-3.8 查阅相关资料,掌握FPGA基本知识。 3.11-3.15 应用Verilog语言进行程序开发,设计调试。 3.18-3.22 调试验收,撰写专业课程实践训练报告。 4.参考文献 [1] 夏宇闻. Verilog数字系统设计教程[M]. 北京:北京航空航天大学出版社,2008. [2] Snair Palnitkar(美). VerilogHDL数字设计与综合. 夏宇闻等译.(第二版)[M]. 北京:电子工业出版社,2009. [3] Xilinx. UG230 [Z/OL]. https://www.360docs.net/doc/9f18936422.html, 指导教师签字: 教研室主任签字:

目录 摘要: (4) 关键词 (4) 一:FPGA (4) 1.1名称 (4) 1.2背景 (4) 1.3工作原理 (4) 1.4芯片结构 (5) 二:Verilog HDL (5) 2.1verilog hdl名称 (5) 2.2verilog hdl用途 (5) 2.3 Ve r i l o g硬件描述语言的主要能力 (6) 三:Spartan3E (7) 四:乘法器 (8) 4.1什么是乘法器 (8) 4.2实现乘法器的方法 (8) 4.3 6*6串行乘法器的设计思路 (9) 4.4 6*6乘法器程序代码 (9) 4.5 6*6乘法器设计仿真图 (11) 4.6结果分析 (12) 四:总结 (12) 参考文献 (12)

计算机组成原理阵列乘法器课程设计报告

. 课程设计

. 教学院计算机学院 课程名称计算机组成原理题目4位乘法整列设计专业计算机科学与技术班级2014级计本非师班姓名唐健峰 同组人员黄亚军 指导教师 2016 年10 月 5 日

1 课程设计概述 1.1 课设目的 计算机组成原理是计算机专业的核心专业基础课。课程设计属于设计型实验,不仅锻炼学生简单计算机系统的设计能力,而且通过进行设计及实现,进一步提高分析和解决问题的能力。 同时也巩固了我们对课本知识的掌握,加深了对知识的理解。在设计中我们发现问题,分析问题,到最终的解决问题。凝聚了我们对问题的思考,充分的锻炼了我们的动手能力、团队合作能力、分析解决问题的能力。 1.2 设计任务 设计一个4位的二进制乘法器: 输入信号:4位被乘数A(A1,A2,A3,A4), 4位乘数B(B1,B2,B3,B4), 输出信号:8位乘积q(q1,q2,q3,q4,q5,q6,q7,q8). 1.3 设计要求 根据理论课程所学的至少设计出简单计算机系统的总体方案,结合各单元实验积累和课堂上所学知识,选择适当芯片,设计简单的计算机系统。 (1)制定设计方案: 我们小组做的是4位阵列乘法器,4位阵列乘法器主要由求补器和阵列全加器组成。 (2)客观要求 要掌握电子逻辑学的基本内容能在设计时运用到本课程中,其次是要思维灵活遇到问题能找到合理的解决方案。小组成员要积极配合共同达到目的。

2 实验原理与环境 2.1 1.实验原理 计算机组成原理,数字逻辑,maxplus2是现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 用乘数的每一位去乘被乘数,然后将每一位权值直接去乘被乘数得到部分积,并按位列为一行每一行部分积末位与对应的乘数数位对齐,体现对应数位的权值,将各次部分积求和得到最终的对应数位的权值。 2.2 2.实验环境 2.2.1双击maxplu2II软件图标,启动软件 (1).新建工程,flie->new project ....,出现存储路径的选项框,指定项目保存路径并且为工程命名,第三行设置实体名,保持与工程名一致。点击OK

乘法器课程设计

摘要:基于VHDL的数字系统设计具有设计技术齐全、方法灵活、支持广泛等优点,同时也是EDA技术的重要组成部分.文章用VHDL语言设计了左移法和进位节省法实现的两种组合乘法器,通过功能仿真,对两种乘法器的性能进行了比较,从而得知后者的传输延迟时间小,即速度较快.通过设计实例,介绍了利用VHDL语言进行数字系统设计的方法. 关键词:VHDL语言左移法进位节省法 Abstract:Digital system design based on VHDL has complete design techniques, methods, the advantages of flexible and wide support, at the same time also is the important component of the EDA technology. The article using VHDL language to design the left shift method and carry save method to realize the combination of two kinds of multiplier, through the function simulation, compares the performance of the two kinds of multiplier, which the latter's small transmission delay time, namely fast. Through the design example, introduced the method of using VHDL language to design digital system. Keywords:VHDL language ,left shift method ,carry save method

基于乘法器复用技术的FFT处理器的设计与实现

基于乘法器复用技术的FFT 处理器的设计与实现 龙海南,耿双利,郑晓昆,李彩霞 摘要:提出了一种基于乘法器复用技术的FFT 优化算法,该算法主要利用了旋转因子关于y 轴和y=x 的对称性,使用两个实数乘法器即可分时共享完成4个复数旋转因子的计算,从而减少硬件资源消耗;采用该算法采用流水线结构,设计了基2的16点IFFT 处理器,使用7个实数乘法器即可完成,进一步优化可仅使用5个。 通过ALTERA Cyclone Ⅱ系列的EP2C70F896C6器件进行下载验证。 F PGA 输出结果与MATLAB 计算结果比较,单点最大相对误差约*** 。 关键字:FFT, 乘法器复用,FPGA Abstract: This paper proposes an optimized FFT algorithm based on multiplier multiplexing technology, it reduces the hardware resource consumption by taking the advantage of the rotation factor symmetry on the y-axis and y=x; Only use 7 real multiplier to design a pipelined radix-2, 16-point IFFT processor, further optimization can only use 5. The verification is carried out through the downloaded ALTERA Cyclone Ⅱ series EP2C70F896C6 device .whose result is less than ***difference compared with the result from the MATLAB calculation Key Words :FFT ;multiplier multiplexing ;FPGA 1 引言 FFT(快速傅里叶变换)是数字信号处理中的重要模块,作为时域和频域转换的基本运算.是数字谱分析的必要前提,在信号处理、图像处理、生物信息学、计算物理、应用数学等方面都有着广泛的应用。在高速数字信号处理中,FFT 的处理速度往往是整个系统设计性能的关键所在[1]。 对于FFT 的硬件实现,大致可以分为3种方案:通过数字信号处理器(DSP)实现;通过专用FFT 芯片实现;通过FPGA 实现[2]。用DSP 完成FFT 运算需要占用大量DSP 的运算时间,使整个系统的吞吐量降低;专用的FFT 处理芯片,虽然速度较快,但其可扩展性差,且成本昂贵。FPGA 不仅有大量的片内资源,而且易于组织流水和并行结构,可以大大提高FFT 的处理速度。将FFT 的实时性要求与FPGA 的灵活性相结合,不仅可以提高处理速度,而且可以方便的移植到ASIC 中。 2 FFT 算法基本原理 对于N 点序列()x n ,其离散傅立叶变换(DFT)变换可写为: ()()()1 0N nk N n X k DFT x n x n W -===???? ∑ 01k N ≤≤-,(2-1) 其中:2j nk nk N N W e π -?=。 由式(2-1)分析可知,若直接计算DFT ,乘法和加法次数都和N 2成正比,当N 很大时,运算量是很可观的。FFT 算法的基本思想:可以将一个长度为N 的序列的离散傅里叶变换逐次分解为较短的离散傅里叶变换来计算,这些短序列的DFT 可重新组合成原序列的DFT ,而总的运算次数却比直接的DFT 运算少得

模拟乘法器AD834的原理与应用

模拟乘法器AD834的原理与应用 1.AD834的主要特性 AD834是美国ADI公司推出的宽频带、四象限、高性能乘法器,其主要特性如下: ●带符号差分输入方式,输出按四象限乘法结果表示;输出端为集电极开路差分电流结构,可以保证宽频率响应特性;当两输入X=Y=±1V时,输出电流为±4mA; ●频率响应范围为DC~500MHz; ●乘方计算误差小于0.5%; ●工作稳定,受温度、电源电压波动的影响小; ●低失真,在输入为0dB时,失真小于0.05%; ●低功耗,在±5V供电条件下,功耗为280mW; ●对直通信号的衰减大于65dB; ●采用8脚DIP和SOIC封装形式。 2.AD834的工作原理 AD834的引脚排列如图1所示。它有三个差分信号端口:电压输入端口X=X1-X2和Y=Y1-Y2,电流输出端口W=W1-W2;W1、W2的静态电流均为8.5mA。在芯片内部,输入电压先转换为差分电流(V-I转换电阻约为280Ω),目的是降低噪声和漂移;然而,输入电压较低时将导致V-I转换线性度变差,为此芯片内含失真校正电路,以改善小信号V-I转换时的线性特性。电流放大器用于对乘法运算电路输出的电流进行放大,然后以差分电流形式输出。 AD834的传递函数为: W=4XY (X、Y的单位为伏特,W的单位为mA) 3.应用考虑 3.1 输入端连接

尽管AD834的输入电阻较高(20kΩ),但输入端仍有45μA的偏置电流。当输入采用单端方式时,假如信号源的内阻为50Ω,就会在输入端产生1.125mV的失调电压。为消除该失调电压,可在另一输入端到地之间接一个与信号源内阻等值的电阻,或加一个大小、极性可调的直流电压,以使差分输入端的静态电压相等;此外,在单端输入方式下,最好使用远离输出端的X2、Y1作为输入端,以减小输入直接耦合到输出的直通分量。 应当注意的是,当输入差分电压超过AD834的限幅电平(±1.3V)时,系统将会出现较大的失真。 3.2 输出端连接 采用差分输出,可有效地抑制输入直接耦合到输出的直通分量。差分输出端的耦合方式,可用RC耦合到下一级运算放大器,进而转换为单端输出,也可用初级带中心抽头的变压器将差分信号转换为单端输出。 3.3 电源的连接 AD834的电源电压允许范围为±4V~±9V,一般采用±5V。要求VW1和VW2的静态电压略高于引脚+VS上的电压,也就是+VS引脚上的电去耦电阻RS应大于W1和W2上的集电极负载电阻RW1、RW2。例如,RS为62Ω,RW1和RW2可选为49.9Ω,而+V=4.4V,VW1=VW2=4.6V,乘法器的满量程输出为±400mV。 引脚-VS到负电源之间应串接一个小电阻,以消除引脚电感以及去耦电容可能产生的寄生振荡;较大的电阻对抑制寄生振荡有利,但也会使VW1和VW2的静态工作电压降低;该电阻也可用高频电感来代替。 4.应用实例 AD834主要用于高频信号的运算与处理,如宽带调制、功率测量、真有效值测量、倍频等。在某航空通信设备扩频终端机(如图2所示)的研制中,笔者应用AD834设计了扩频信号调制器和扩频信号接收AGC电路。

基于标准单元库扩展的快速乘法器设计

收稿日期:2011-09-20;修回日期:2011-11-04 基金项目:国家科技重大专项基金资助项目(2009ZX01030-001-002). 作者简介:曾宪恺(1987-),男,湖北孝感人,硕士,主要研究方向为超大规模集成电路设计自动化(zengxk@vlsi.zju.edu.cn );郑丹丹(1981-),女,博士,主要研究方向为超深亚微米集成电路SOC 设计;严晓浪(1947-),男,教授,主要研究方向为超大规模集成电路设计、VLSI 设计自动化;吕冬明(1981-),男,博士,主要研究方向为集成电路CAD 研究;葛海通(1972-),男,博士,主要研究方向为嵌入式系统设计. 基于标准单元库扩展的快速乘法器设计 * 曾宪恺,郑丹丹,严晓浪,吕冬明,葛海通 (浙江大学超大规模集成电路设计研究所,杭州310027) 摘 要:设计并实现17?17bit 带符号数字乘法器。为了提高乘法器的性能,采用改进的Booth 编码算法、 Wal-lace 树型结构以及基于标准单元库扩展的设计方法。该方法使用逻辑功效模型分析乘法器的关键路径,通过构造驱动能力更为完备的单元以实现关键路径中每一级门功效相等,从而得到最短路径延时。将TSMC 90nm 标准单元库扩展得到扩展单元库, 使用两个单元库版图分别实现数字乘法器,基于扩展单元库实现的乘法器速度提升10.87%。实验结果表明,基于标准单元库扩展的半定制设计方法可以有效提升电路的性能,这种方法尤其适用于电路负载过大的情况。 关键词:乘法器;标准单元库扩展;改进的Booth 编码算法;Wallace 树;逻辑功效中图分类号:TN47 文献标志码:A 文章编号:1001-3695(2012)05-1778-03 doi :10.3969/j.issn.1001-3695.2012.05.047 Design of high-speed multiplier based on standard cell library extension ZENG Xian-kai ,ZHENG Dan-dan ,YAN Xiao-lang ,LV Dong-ming ,GE Hai-tong (Institute of VLSI Design ,Zhejiang University ,Hangzhou 310027,China ) Abstract :This paper proposed a 17?17bit signed digital multiplier.To improve the performance ,the multiplier used modi-fied Booth ’s recoding algorithm ,a Wallace tree structure and design method based on standard cell library extension.It ana-lyzed critical path using logical effort model ,and by constructing cells with different driving capabilities , it implemented equal logical effort in each stage to achieve minimum path delay.Based on TSMC 90nm standard cell library , generated an extended cell library ,and implemented the layouts of multiplier respectively.Compared to standard cell library ,the multiplier imple-mented with extended cell library achieved a performance improvement of 10.87%.Experimental results show that the semi-custom design methodology based on standard cell library extension can improve circuit performance effectively ,which is espe-cially appropriate for designs with large loads. Key words :multiplier ;standard cell library extension ;modified Booth ’s recoding algorithm ;Wallace tree ;logical effort 0引言 乘法器是嵌入式CPU 的重要部件,其运算速度决定了逻 辑运算单元的工作频率,因此高性能乘法器的设计仍然被关注 [1,2] 。同时,市场的需求加速了产品的上市进程,从而要求 设计者尽量缩短设计时间。为了兼顾乘法器的性能和设计时间, 通常使用基于标准单元库的半定制设计方法。但该方法受限于库中标准单元有限的驱动能力,无法实现最短路径延时。为此,本文提出基于标准单元库扩展的乘法器设计方法,消除了传统方法因关键路径优化不足对乘法器性能的影响。基于TSMC 90nm 工艺标准单元库扩展,设计并实现了17?17bit 乘法器模块。该乘法器支持带符号二进制乘法运算, 最差情况下(工作电压0.9V ,温度125℃)工作频率为346MHz 。设计过程中,使用EDA 工具进行了速度优先的逻辑综合以及布局布线;在关键路径的处理中,采用了基于逻辑功效的优化方法。 1乘法器 二进制乘法器实现了二进制数的乘法运算,它将两个二进 制数X 和Y 作为输入,将乘法运算的积Z 作为输出。设被乘数为m 位,记为X m -1X m -2…X 0,乘数为n 位,记为Y n -1Y n -2…Y 0,则积为m +n 位,记为Z m +n -1Z m +n -2…Z 0。将m 位被乘数X 与n 位乘数Y 的每一位进行与运算,可以得到n 项位数为m 的部分积, 用加法器阵列将n 项部分积相加,得到积Z 。乘法器的具体实现分为部分积生成、部分积压缩、最终加法三个步骤。通常,使用与门来产生部分积,用加法器阵列对部分积压缩来构成阵列乘法器。这种架构算法简单,易于实现,并且能够实现规则的版图结构,但是由于部分积个数较多,压缩时间较长,无法得到快速的乘法器。使用改进的Booth 编码算法[3,4] 有效地减少了部分积的个数,使用Wallace 树型结 构 [5] 缩短部分积压缩的时间,其算法较复杂,并且版图结构不 规则, 但可以有效地提升乘法器的性能。第29卷第5期2012年5月计算机应用研究 Application Research of Computers Vol.29No.5May 2012

八位乘法器VHDL及功能模块说明

EDA课程设计报告 实验名称:八位乘法器

目录 一.引言 1.1 EDA技术的概念?? 1.2 EDA技术的特点?? 1.3 EDA设计流程?? 1.4 VHDL介绍?? 二.八位乘法器的设计要求与设计思路??2.1 设计目的?? 2.2 设计要求?? 三.八位乘法器的综合设计?? 3.1 八位乘法器功能?? 3.2 八位乘法器设计方案?? 3.3 八位乘法器实体设计?? 3.4 八位乘法器VHDL设计?? 3. 5八位乘法器仿真图形?? 心得体会?? 参考文献??

一、引言 1.1 EDA技术的概念 EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。 1.2 EDA技术的特点 利用EDA技术进行电子系统的设计,具有以下几个特点:①用软件的方式设计硬件;②用软件方式设计的系统到硬件系统的转换是由有关的开发软件自动完成的;③设计过程中可用有关软件进行各种仿真;④系统可现场编程,在线升级;⑤整个系统可集成在一个芯片上,体积小、功耗低、可靠性高。因此,EDA技术是现代电子设计的发展趋势。 1.3 EDA设计流程 典型的EDA设计流程如下: 1、文本/原理图编辑与修改。首先利用EDA工具的文本或图形编辑器将设计者的设计意图用文本或图形方式表达出来。 2、编译。完成设计描述后即可通过编译器进行排错编译,变成特定的文本格式,为下一步的综合做准备。 3、综合。将软件设计与硬件的可实现性挂钩,是将软件转化为硬件电路的关键步骤。 4、行为仿真和功能仿真。利用产生的网表文件进行功能仿真,以便了解设计描述与设计意图的一致性。 5、适配。利用FPGA/CPLD布局布线适配器将综合后的网表文件针对某一具体的目标器件进行逻辑映射操作,其中包括底层器件配臵、逻辑分割、逻辑优化、布局布线。适配报告指明了芯片内资源的分配与利用、引脚锁定、设计的布尔方程描述情况。

计算机组成原理_阵列乘法器设计

沈阳航空航天大学 课程设计报告 课程设计名称:计算机组成原理课程设计课程设计题目:阵列乘法器的设计与实现 院(系):计算机学院 专业:计算机科学与技术 班级: 学号: 姓名: 指导教师: 完成日期:2014年1月10日

沈阳航空航天大学课程设计报告 _______________________________________________________________________________ 目录 第1章总体设计方案 (1) 1.1设计原理 (1) 1.2设计思路 (2) 1.3设计环境 (3) 第2章详细设计方案 (3) 2.1总体方案的设计与实现 (4) 2.1.1总体方案的逻辑图 (4) 2.1.2器件的选择与引脚锁定 (4) 2.1.3编译、综合、适配 (5) 2.2功能模块的设计与实现 (5) 2.2.1一位全加器的设计与实现 (6) 2.2.2 4位输入端加法器的设计与实现 (7) 2.2.3 阵列乘法器的设计与实现 (10) 第3章硬件测试 (13) 3.1编程下载 (13) 3.2 硬件测试及结果分析 (13) 参考文献 (15) 附录(电路原理图) (16)

第1章总体设计方案 1.1 设计原理 阵列乘法器采用类似人工计算的方法进行乘法运算。人工计算方法是用乘数的每一位去乘被乘数,然后将每一位权值对应相加得出每一位的最终结果。如图1.1所示,用乘数的每一位直接去乘被乘数得到部分积并按位列为一行,每一行部分积末位与对应的乘数数位对齐,体现对应数位的权值。将各次部分积求和,即将各次部分积的对应数位求和即得到最终乘积的对应数位的权值。 为了进一步提高乘法的运算速度,可采用大规模的阵列乘法器来实现,阵列乘法器的乘数与被乘数都是二进制数。可以通过乘数从最后一位起一个一个和被乘数相与,自第二位起要依次向左移一位,形成一个阵列的形式。这就可将其看成一个全加的过程,将乘数某位与被乘数某位与完的结果加上乘数某位的下一位与被乘数某位的下一位与完的结果再加上前一列的进位进而得出每一位的结果,假设被乘数与乘数的位数均为4位二进制数,即m=n=4,A×B可用如下竖式算出,如图1.1所示。 X 4 X 3 X 2 X 1 =A × Y 4 Y 3 Y 2 Y 1 =B X 4Y 1 X 3 Y 1 X 2 Y 1 X 1 Y 1 X 4Y 2 X 3 Y 2 X 2 Y 2 X 1 Y 2 X 4Y 3 X 3 Y 3 X 2 Y 3 X 1 Y 3 (进位) X4Y4 X3Y4 X2Y4 X1Y4 Z 8 Z 7 Z 6 Z 5 Z 4 Z 3 Z 2 Z 1 图1.1 A×B计算竖式 X 4 ,X 3 ,X 2 ,X 1 ,Y 4 ,Y 3 ,Y 2 ,Y 1 为阵列乘法器的输入端,Z 1 -Z 8 为阵列乘法器 的输出端,该逻辑框图所要完成的功能是实现两个四位二进制既A(X)*B(Y)的 乘法运算,其计算结果为C(Z) (其中A(X)=X 4X 3 X 2 X 1 ,B(Y)=Y 4 Y 3 Y 2 Y 1 , C(Z)=Z 8Z 7 Z 6 Z 5 Z 4 Z 3 Z 2 Z 1 而且输入和输出结果均用二进制表示 )。阵列乘法器的总原 理如图1.2所示。

模拟乘法器及其应用

模拟乘法器及其应用

摘要 模拟乘法器是一种普遍应用的非线性模拟集成电路。模拟乘法器能实现两个互不相关的模拟信号间的相乘功能。它不仅应用于模拟运算方面,而且广泛地应用于无线电广播、电视、通信、测量仪表、医疗仪器以及控制系统,进行模拟信号的变换及处理。在高频电子线路中,振幅调制、同步检波、混频、倍频、鉴频、鉴相等调制与解调的过程,均可视为两个信号相乘或包含相乘的过程。采用集成模拟乘法器实现上述功能比采用分立器件如二极管和三极管要简单的多,而且性能优越。 Analog multiplier is a kind of widely used nonlinear analog integrated multiplier can be achieved between two unrelated analog multiplication is not only applied in the simulation operation aspect, and widely used in radio, television, communications, measuring instruments, medical equipment and control system, the analog signal conversion and the high frequency electronic circuit, amplitude modulation, synchronous detection, mixing, frequency doubling, frequency, modulation and demodulation process, the same as can be seen as two signal multiplication or contain multiplication function is realized by using integrated analog multiplier than using discrete components such as diodes and transistors are much more simple, and superior performance.

流水线乘法器

流水线乘法器 一般的快速乘法器通常采用逐位并行的迭代阵列结构,将每个操作数的N位都并行地提交给乘法器。但是一般对于FPGA来讲,进位的速度快于加法的速度,这种阵列结构并不是最优的。所以可以采用多级流水线的形式,将相邻的两个部分乘积结果再加到最终的输出乘积上,即排成一个二叉树形式的结构,这样对于N位乘法器需要log2(N)级来实现。一个8位乘法器,如图所示。 module mux_4(mul_a,mul_b,mul_out,clk,rst_n); parameter MUL_WIDTH = 4; parameter MUL_RESULT = 8; input [MUL_WIDTH-1:0] mul_a; input [MUL_WIDTH-1:0] mul_b; input clk; input rst_n; output [MUL_RESULT-1:0] mul_out; reg [MUL_RESULT-1:0] mul_out; reg [MUL_RESULT-1:0] stored0; reg [MUL_RESULT-1:0] stored1; reg [MUL_RESULT-1:0] stored2; reg [MUL_RESULT-1:0] stored3; reg [MUL_RESULT-1:0] add01; reg [MUL_RESULT-1:0] add23; always @(posedge clk or negedge rst_n) begin if(!rst_n) begin mul_out <= 8'b0000_0000;

stored0 <= 8'b0000_0000; stored1 <= 8'b0000_0000; stored2 <= 8'b0000_0000; stored3 <= 8'b0000_0000; add01 <= 8'b0000_0000; add23 <= 8'b0000_0000;; end else begin stored3 <= mul_b[3] ? {1'b0,mul_a,3'b0} : 8'b0; stored2 <= mul_b[2] ? {2'b0,mul_a,2'b0} : 8'b0; stored1 <= mul_b[1] ? {3'b0,mul_a,1'b0} : 8'b0; stored0 <= mul_b[0] ? {4'b0,mul_a} : 8'b0; add01 <= stored1 + stored0; add23 <= stored3 + stored2; mul_out <= add01 + add23; end end endmodule

并行前缀加法器优化并行阵列乘法器的设计(IJEM-V3-N2-3)

I.J. Engineering and Manufacturing, 2013, 2, 40-50 Published Online September 2013 in MECS (https://www.360docs.net/doc/9f18936422.html,) DOI: 10.5815/ijem.2013.02.03 Available online at https://www.360docs.net/doc/9f18936422.html,/ijem Design Of A Optimized Parallel Array Multiplier Using Parallel Prefix Adder K.KalaiKaviya a, D.P.Balasubramanian b, S.Tamilselvan c a,b PG Student,S.M.K Fomra Institute of technology, Chennai c Asst Professor,S.M.K Fomra Institute of technology, Chennai Abstract Multiplication is the basic building block for several DSP processors, Image processing and many other. Over the years the computational complexities of algorithms used in Digital Signal Processors (DSPs) have gradually increased. This requires a parallel array multiplier to achieve high execution speed or to meet the performance demands. A typical implementation of such an array multiplier is Braun design. Braun multiplier is a type of parallel array multiplier. The architecture of Braun multiplier mainly consists of some Carry Save Adders, array of AND gates and one Ripple Carry Adder. In this research work, a new design of Braun Multiplier is proposed and this proposed design of multiplier uses a very fast parallel prefix adder (Brent kung Adder) in place of Ripple Carry Adder. The architecture of standard Braun Multiplier is modified in this work for reducing the area and delay due to Ripple Carry Adder and performing faster multiplication of two binary numbers. The design is implemented using Microwind1, digital schematics (DSCH) Index Terms: Array multiplier, carry save adder (CSA), Kogge stone Adder, parallel prefix adder ripple carry adder, Microwind, DSCH. ? 2013 Published by MECS Publisher. Selection and/or peer review under responsibility of the Research Association of Modern Education and Computer Science. 1.Introduction For scientific computations, Multiplication is an important and predominance in all digital signal processing (DSP) applications and its subfields. Application Specific Integrated Circuits (ASICs) utilizes as special purpose processor for DSP algorithms [1]. Multiplication is a Repeated addition of n bits will give the solution for the multiplication. i.e.Multioperand addition process. The multioperand addition process needs two n – bit operands. It can be realized in n- cycles of shifting and adding. If the multiplicand is given be. * Corresponding author. Tel.: 00966; 533273146 E-mail address: salem_farh@https://www.360docs.net/doc/9f18936422.html,

乘法器的设计

物理与电子工程学院集成电路设计课程论文题目:乘法器的研究 学生姓名:XXX 指导教师:XXX 201X年XX月XX日

乘法器 摘要:乘法器,其基础就是加法器结构,它已经是现代计算机中必不可少的一部分。 乘法器的模型就是基于“移位和相加”的算法。本文讨论基本的阵列乘法器,以及产生部分 积和最终求和。 关键词:全加器,半加器,阵列。 引言: 乘法运算非常耗费硬件面积并且速度很慢,许多计算问题解决的快慢受乘法器电 路工作速度的约束,因此在现代高级的数字信号处理器和微处理器中都集成了硬件乘法单 元。并且乘法器在当今数字信号处理以及其他诸多应用领域中起着十分重要的作用。随着科 学技术的发展,许多研究人员已经开始试图设计一类拥有更高速率和低功耗,布局规律占用 面积小,集成度高的乘法器。这样,就能让它们更加适用于高速率,低功耗的大规模集成电 路的应用当中。通常的乘法计算方法是添加和位移的算法。在并行乘法器当中,相加的部分乘积的数量是主要的参数。它决定了乘法器的性能。为了减少相加的部分乘积的数量,修正 的Booth 算法是最常用的一类算法。但是,随着并行化的增多,大量的部分乘积和中间求和 的增加,会导致运行速度的下降。不规则的结构会增加硅板的面积,并且由于路由复杂而导 致中间连接过程的增多继而导致功耗的增大。另一方面串并行乘法器牺牲了运行速度来获得 更好的性能和功耗。因此,选择一款并行或串行乘法器实际上取决于它的应用性质。 主体 1.1.1二进制乘法定义 考虑两个无符号二进制数X 和Y ,X 为M 位宽,Y 为N 位宽,将它们用下列二进制数形 式表达 i 1 -M 0i i 2X X ∑== (1.1) j 1 -N 0j j 2Y Y ∑== (1.2) 其中i X 和j Y 为0或者1,那么X 和Y 的乘法运算定义如下 Z=X ×Y= k 1 -N M 0k k 2Z ∑+= =(i M i i X 210∑-=)(j 1-N 0j j 2Y ∑=)=∑∑=-=+???? ??1-M 0i 10j 2N j i j i Y X (1.3) 我们先来看一下手工是如何进行二进制乘法运算的。如图1-1所示,被乘数与乘数的第一个 位相乘(实际为“与”操作)产生积,并且根据乘数相应位的位置对部分积进行左移(例如, 被乘数与乘数的第0位相乘,则不移位;与第一位相乘,部分积左移1位,以此类推),最 终将所有的部分积相加得到乘法运算的结果。M 位被乘数与N 位乘数相乘得到的乘积是 M+N 位的。 1.1.2部分积生成

三种高速乘法器的FPGA实现及性能比较

三种高速乘法器的FPGA实现及性能比较 摘要:乘法是数字信号处理中重要的基本运算,在很大程度上影响着系统的性能。本文将介绍三种高速乘法器实现原理:阵列乘法器、华莱士(WT)乘法器、布斯华莱士树超前进位乘法器。而且通过FPGA技术实现了这三种乘法器,并对基于以上三种架构的乘法器性能进行了分析比较。 关键字:阵列乘法器,华莱士乘法器,超前进位乘法器,FPGA 1、引言 随着3G技术的发展,关于图像、语音、加密等数字信号处理技术随处可见,而且信号处理的实时性也要求越高。实时性即是要求对信号处理的速度要快,而乘法器是数字信号处理中重要的基本运算,在很大程度上影响着系统的性能。人们开始开发高速的乘法器。 以下将对三种乘法器:阵列乘法器、华莱士(WT)乘法器、布斯华莱士树超前进位乘法器进行原理分析,并用FPGA技术实现了这三种乘法器,对其结果进行了仿真,得出相应的性能比较。 2、阵列乘法器 2.1 阵列乘法器原理 硬件乘法器的常规设计是适用“串行移位”和“并行加法”相结合的方法,这种方法并不需要很多器件。然而串行方法毕竟太慢,执行一次乘法的时间至少是执行一次加法时间的n倍,不能满足科学技术对高速乘法所提出的要求。自从大规模集成电路问世以来,高速的单元阵列乘法器应运而生,出现了各种形式的流水线阵列乘法器,它们属于并行乘法器,提供了极快的速度。阵列乘法器的运算过程如下: 第一:当乘数的位数字为1 时,我们可以将被乘数的值直接放置适当的位置。而适当的位置是依乘数的第几个位和被乘数做运算之后所放的位置。 第二:当乘数的位数字为0 时,我们可以将0 放置适当的位置, 以作为部分乘积。 第三:我们利用笔和纸计算的乘法,在硬件中使用与门来实现。例如:1000 ×1中,乘数1 和每一个被乘数的位都个别做与运算,其结果为1000 正是我们所要的结果。由此可知我们只需用与门就可以完成我们所要的乘法。 第四:当部分乘积都运算完成后,使用加法来完成最终的乘法结果运算。 根据以上四点的说明,我们可以运用最简单、最直观的方式来描述固定点乘法器的电路描述。我们使用与门来做部分积运算,使用全加器(Full adder)来运算部分积的最终结果。图1所示为有符号位的6×6固定点乘法器的架构图。