基于DSP的三相软件锁相环设计

软件详细设计模板示例汇总

项目案例名称:《软件系统》 项目案例文档:《软件系统概要设计说明书》 1. 导言 1.1 目的 本文档的目的是描述《软件系统》项目的详细设计,其主要内容包括: -系统功能简介 -系统详细设计简述 -各个模块的三层划分 -最小模块组件的伪代码 本文档的预期的读者是: ●设计人员 ●开发人员 ●项目管理人员 ●测试人员 1.2 范围 该文档定义了系统的各个模块和模块接口,但未确定单元的具体实现,这部分内容将在实现中确定。 1.3引用标准 [1] 《企业文档格式标准》 V1.1 北京长江软件有限公司 [2] 《软件详细设计报告格式标准》 V1.1 北京长江软件有限公司软件工程过程化组织 1.4 参考资料 [1] 《实战struct》〔美〕TedHusted 机械工业出版社 1.5 版本更新信息 本文档版本更新记录如表C-1: 表C-1:版本更新记录 2 系统设计概述 根据《软件系统》的概要设计,系统分为用户登录管理、帐号管理、帐号组权限管理、角色管理、日志查询、统计报表、平台管理、业务信息系统维护、个人信息维护等模块,他

们的关系如图C-1,以下将分小节对各个部分分别进行详细设计。 图C-1:模块设计图 3 详细设计概述 由于本系统采用了基于Struts体系结构的设计,即采用MVC的三层设计模式,采用面向对象的JAVA语言以及JSP的脚本语言。所以,基本采用面向对象的设计方法。在整个的开发过程中,尽可能采用复用的原则,例如采用标签库,统一数据库的基本操作,统一结果显示等。 本文档的详细设计主要是按照Struts的MVC的三个层次分别描述视图层、控制层和模型层模块的伪代码。为下一步的编码提供基础。 4登录管理模块 登录管理模块负责用户的登录。系统框架可以分成三层结构,即视图层、控制层和模型层,具体如表C-2所示。 表C-2:登录管理的三层模块 4.1视图层 根据上述的功能介绍,视图页面设计如表C-3所示。 表C-3:登录管理模块页面设计

锁相环电路设计

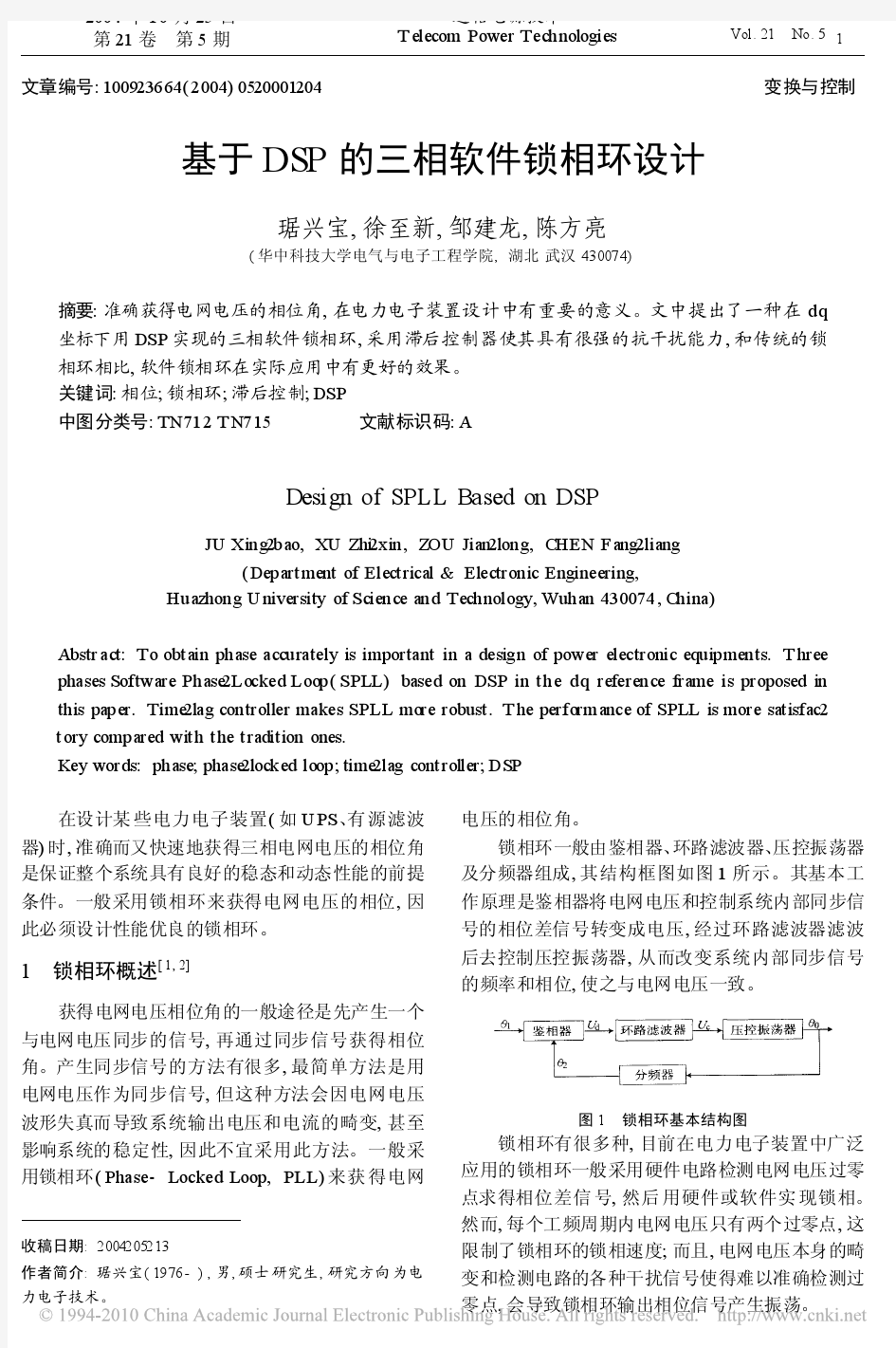

锁相环的原理 2007-01-23 00:24 1.锁相环的基本组成 许多电子设备要正常工作,通常需要外部的 输入信号与部的振荡信号同步,利用锁相环 路就可以实现这个目的。 锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路部振荡信号的频率和相位。 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。 锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。 锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。 2.锁相环的工作原理 锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为: (8-4-1) (8-4-2) 式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。则模拟乘法器的输出电压u D为: 用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C (t)。即u C(t)为: (8-4-3) 式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:

锁相环的基本原理和模型

1.锁相环的基本原理和模型 在并网逆变器系统中,控制器的信号需要与电网电压的信号同步,锁相环通过检测电网电压相位与输出信号相位之差,并形成反馈控制系统来消除误差,达到跟踪电网电压相位和频率的目的。一个基本的锁相环结构如图1-1所示,主要包括鉴相器,环路滤波器,压控振荡器三个部分。 图1-1 基本锁相环结构 鉴相器的主要功能是实现锁相环输出与输入的相位差检测;环路滤波器的主要作用应该是建立输入与输出的动态响应特性,滤波作用是其次;压控振荡器所产生的所需要频率和相位信息。 PLL 的每个部分都是非线性的,但是这样不便于分析设计。因此可以用近似的线性特性来表示PLL 的控制模型。 鉴相器传递函数为:)(Xo Xi Kd Vd -= 压控振荡器可以等效为一个积分环节,因此其传递函数为:S Ko 由于可以采用各种类型不同的滤波器(下文将会讲述),这里仅用)(s F 来表示滤波器的传递函数。 综合以上各个传递函数,我们可以得到,PLL 的开环传递函数,闭环传递函数和误差传递函数分别如下: S s F K K s G d o op )()(=,)()()(s F K K S s F K K s G d o d o cl +=,) ()(s F K K S S s H d o += 上述基本的传递函数就是PLL 设计和分析的基础。 2.鉴相器的实现方法 鉴相器的目的是要尽可能的得到准确的相位误差信息。可以使用线电压的过零检测实现,但是由于在电压畸变的情况下,相位信息可能受到严重影响,因此需要进行额外的信号处理,同时要检测出相位信息,至少需要一个周波的时间,动态响应性能可能受到影响。 一般也可以使用乘法鉴相器。通过将压控振荡器的输出与输入相乘,并经过一定的处理得到相位误差信息。 在实际的并网逆变器应用中还可以在在同步旋转坐标系下进行设计,其基本的目的也是要得的相差的数值。同步旋转坐标系下的控制框图和上图类似,在实际使用中,由于pq 理论在电网电压不平衡或者发生畸变使得性能较差,因而较多的使用dq 变换,将采样得到的三相交流电压信号进行变化后与给定的直流参考电压进行比较。上述两种方法都使用了近似,利用在小角度时正弦函数值约等于其角度,因而会带来误差,这个误差是人为近似导致的误差,与我们要得到的相位误差不是一个概念,最终的我们得到相位误差是要形成压控振荡器的输入信号,在次激励下获得我们所需要的频率和相位信息。 2.1乘法鉴相器

基于DSP的软件锁相环

一种基于DSP的软件锁相环模型与实现 随着大规模集成电路及高速数字信号处理器的发展,通信领域的信号处理越来越多地在数字域付诸实现。软件锁相技术是随着软件无线电的发展和高速DSP的出现而开展起来的一个研究课题。在软件无线电接收机中采用的锁相技术是基于数字信号处理技术在DSP等通用可编程器件上的实现形式,由于这一类型锁相环的功能主要通过软件编程实现,因此可将其称为软件锁相环(software PLL)[1]。 尽管软件锁相环采用的基本算法思想与模拟锁相环和数字锁相环相比并没有太大变化,然而其实现方式却完全不同。本文将建立软件锁相环的Z 域模型,分析软件锁相环中的延时估计、捕获速度及多速率条件下的软件锁相环模型问题[1]。 1软件锁相环的基本模型 在模拟锁相环的基础上,利用数字、模拟系统彼此之间的联系,以二阶二型锁相环为例建立软件锁相环的Z 域模型。文献[2]详细给出了锁相环的基本模型和原理。 如果将锁相环的基本部件采用软件编程的形式实现,就可以得到软件锁相环的基本组成,如图1所示。 首先从模拟锁相环的S域模型出发得到软件锁相环的Z 域模型(二阶二型模拟锁相环的S 域模型请参阅文献[2])。由于双线性变换是联系模拟系统与数字系统的一个重要方法,具有转换简单且表达式清晰明了的特点[3],因此本文选择双线性变换法作为模拟锁相环与软件锁相环之间的转换基础。 式(1)是双线性变换法的复频域表达式: 其中:T是联系数字系统与模拟系统的采样时间间隔,1/T表示采样频率。根据该转换关系,对S域模型各部分对应的数字复频域表达式进行转换,可以得到如图2所示的复频域模型。 在实际应用中,二阶线性系统常采用阻尼因子ξ、无阻尼振荡频率ωn描述。在二阶二型锁相环中,τ1,τ2 ,K 与ξ,ωn之间的对应关系如下: 在式(1)和式(2)的基础上对图2进行等效变换,可以得到软件锁相环的另一个线性相位Z域模型,如图3所示。

软件开发成功的例子

软件开发成功的例子 软件开发成功的例子1: 一、项目实施进度评估。ERP项目是复杂项目,其涉及的部门、 人员、资金、资源等对于任何一个企业来说都是空前的,而在上一 节中我们通过项目三角形分析出来,项目的进度是否能够按照设计 规划的进行是影响项目效果的关键因素,所以评估项目的成功与否,首先必须评估项目的进度是否按照预期的进度进行,如果每一步或 者每一阶段,都能够严格的按照进度进行,相信项目会成功的,否 则就是项目设计出现了问题。一般来说现在评估项目实施进度的方 法可以使用目前最为常用的项目管理工具,其中Microsoft的 Project就是不错的工具之一。其实很多项目的实施失败原因是虎 头蛇尾,开始的时候大家心气十足,进度基本可以按照计划进行, 而到了后来,每个人的工作都是交叉的,往往会受到其他工作的影 响而忽视了项目的进度,致使项目进行不下去。所以除了有相应的 制度保障之外,一定要有工具,再者说了搞IT的人不用IT工具, 那不是“卖盐的喝淡汤”吗?当然现在的IT行业非常普遍。 四、项目效果评估。功能具备只是基本的要求,关键还要看效果,这一点可能有人不容易理解,其实在ERP管理软件中有很多功能从 表面上看功能和效果是有很大的区别的,比如MRP计划,可能大多 数的ERP软件现在都能实现这个功能,但是是否准确,是否可以通 过MRP计划直接指导生产,甚至直接根据计划产生的结果安排采购,这并不是任何一家软件都可以做到的,这里面涉及到计算方法是否 科学,是否符合行业的规范,考虑的因素是否完整,预置的参数是 否科学,比如提前期设计的是否合理,安全库存设计的是否合理等 等都会直接影响计划的结果,其实真正的软件公司的功底就在这里 区别。 软件开发成功的例子2:

锁相环应用电路仿真

高频电子线路实训报告锁相环路仿真设计 专业 学生姓名 学号 2015 年 6 月24日

锁相环应用电路仿真 锁相环是一种自动相位控制系统,广泛应用于通信、雷达、导航以及各种测量仪器中。锁相环及其应用电路是“通信电子电路”课程教学中的重点容,但比较抽象,还涉及到新的概念和复杂的数学分析。因此无论是教师授课还是学生理解都比较困难。为此,我们将基于Multisim的锁相环应用仿真电路引入课堂教学和课后实验。实践证明,这些仿真电路可以帮助学生对相关容的理解,并为进行系统设计工作打下良好的基础。锁相环的应用电路很多,这里介绍锁相环调频、鉴频及锁相接收机的Multisim仿真电路。 1.锁相环的仿真模型 首先在Multisim软件中构造锁相环的仿真模型(图1)。基本的锁相环由鉴相器(PD)、环路滤波器(I P)和压控振荡器(VCO)三个部分组成。图中,鉴相器由模拟乘法器A 实现,压控振荡器为V3,环路滤波器由R1、C1构成。环路滤波器的输出通过R2、R3串联分压后加到 压控振荡器的输入端,直流电源V2用来调整压控振荡器的中心频率。仿真模型中,增加R2、R3及的目的就是为了便于调整压控振荡器的中心频率。 图1 锁相环的仿真模型 2.锁相接收机的仿真电路 直接调频电路的振荡器中心频率稳定度较低,而采用晶体振荡器的调频电路,其调频围又太窄。采用锁相环的调频器可以解决这个矛盾。其结构原理如图2所示。

图2 锁相环调频电路的原理框图 实现锁相调频的条件是调制信号的频谱要处于低通滤波器通带之外,也就是说,锁相环路只对慢变化的频率偏移有响应,使压控振荡器的中心频率锁定在稳定度很高的晶振频率上。而随着输人调制信号的变化,振荡频率可以发生很大偏移。 图3 锁相环调频的仿真电路 根据图2建立的仿真电路如图3所示。图中,设置压控振荡器V1在控制电压为0时,输出频率为0;控制电压为5V时,输出频率为50kHz。这样,实际上就选定了压控振荡器的中心频率为25kHz,为此设定直流电压V3为2.5V。调制电压V4通过电阻Rs接到VCO的输人端,R实际上是作为调制信号源V4的阻,这样可以保证加到VCO输人端的电压是低通滤波器的输出电压和调制电压之和,从而满足了原理图的要求。本电路中,相加功能也可以通过一个加法器来完成,但电路要变得相对复杂一些。 VCO输出波形和输人调制电压的关系如图4所示。由图可见,输出信号频率随着输人信号的变化而变化,从而实现了调频功能。

锁相环电路

手机射频部分的关键电路----锁相环电路 锁相坏电路是一种用来消除频率误差为目的反馈控制电路,目前市场销售的手机基本上都是采用这种电路来控制射频电路中的压控振荡器。使其输出准确稳定的振荡频率。如锁相坏(PLL)电路出现故障将导致本振的频率输出不准确,则导致手机无信号。 目前通信终端设备中对频率的稳定采用的是频率合成CSYN技术。频率合成的基本方法有三种:第一种直接频率合成;第二种锁相频率合成(PLL);第三种直接数字频率合成(DDS)。由于锁相频率合成技术在电路设计方面(简单),成本方面控制灵敏度方面,频谱纯净度方面等。都要胜于直接频率合成,与直接数字频率合成。所以被移动通信终端设备广范采用。它在手机电路中的作用是控制压控振荡器输出的频率,相位与基准信号的频率,相位保持同步。 锁相坏电路的构成与工作原理: 1、构成:它是由鉴相器(PD)低通滤波器(LPF) 压控振荡器(VCO)三部分组成。 鉴相器:它是一个相位比较器。基准频率信号和压控振荡器输出的取样频率在其内部 进行相位比较,输出误差电压。 低通滤波器:是将鉴相器输出的锁相电压进行滤波,滤除电流中的干扰和高频成分。得到一个纯净的直流控制电压。 压控振荡器:产生手机所要的某一高频频率。 (注:SYNEN、SYNCLK、SYNDATA来自CPU控制分频器,对本振信号进行N次分频)。 当VCO产生手机所须的某一高频频率。一路去混频管,另一路反馈给锁相环,中的分频器进行N次分频。在这里为什么要进行N次分频呢?首先要说明一下基准频率与VCO振荡取样频率在鉴相要满足3个条件。 ①频率相同。②幅度相同。③相位不同。为了满足鉴相条件,所以在电路中设置了分 频器。VCO振荡频率取样信号送入分频器完成N次分频后,得到一个与基准频率相位不同,但频率

软件项目详细设计 示例模版

XXX软件/项目/系统 详细设计说明书拟制日期 评审人日期 批准日期 编写单位或个人 修订历史

目录 XXX软件详细设计说明书 (1) Revision Record 修订记录 (1) 1 引言 (1) 1.1 编写目的 (1) 1.2 背景 (1) 1.3 参考资料 (1) 1.4 术语定义及说明 (1) 2 设计概述 (2) 2.1 任务和目标 (2) 2.1.1 需求概述 (2)

2.1.2 运行环境概述 (2) 2.1.3 条件与限制 (2) 2.1.4 详细设计方法和工具 (2) 3 系统详细需求分析 (3) 3.1 详细需求分析 (3) 3.2 详细系统运行环境及限制条件分析接口需求分析 (3) 4 总体方案确认 (4) 4.1 系统总体结构确认 (4) 4.2 系统详细界面划分 (5) 4.2.1 应用系统与支撑系统的详细界面划分 (5) 4.2.2 系统内部详细界面划分 (5) 5 系统详细设计 (5)

5.1 系统结构设计及子系统划分 (5) 5.2 系统功能模块详细设计 (6) 5.3 系统界面详细设计 (7) 5.3.1 外部界面设计 (8) 5.3.2 内部界面设计 (8) 5.3.3 用户界面设计 (8) 6、数据库系统设计 (8) 6.1设计要求 (8) 6.2 信息模型设计 (8) 6.3 数据库设计 (9) 6.3.1 设计依据 (9) 6.3.2 数据库种类及特点 (9)

6.3.3 数据库逻辑结构 (9) 6.3.4 物理结构设计 (10) 6.3.5 数据库安全 (10) 6.3.6 数据字典 (10) 7 非功能性设计 (10) 8 ...................................................... 错误!未定义书签。 9 环境配置 (11)

【原创】锁相环PLL制作与调试要点.

基于MC145152+MC12022+MC1648L+LM358 的锁相环电路 一、MC145152(鉴相器) MC145152-2 芯片是摩托罗拉公司生产的锁相环频率合成器专用芯片。它是MC145152-1 芯片的改进型。主要具有下列主要特征: (1)它与双模(P/(P+1))分频器同时使用,有一路双模分频控制输出MC。当MC 为低电平时,双模分频器用(P+1)去除;当MC 为高电平时,双模分频器用模数P 去除。 (2)它有 A 计数器和N 计数器两个计数器。它们与双模(P/(P+1))分频器提供了总分频值(NP+A)。其中,A、N 计数器可预置。N 的取值范围为3~1023,A 的取值范围为0~63。A 计数器计数期间,MC 为低电平;N 计数器计数(N-A)期间,MC 为高电平。 (3)它有一个参考振荡器,可外接晶体振荡器。 (4)它有一个R计数器,用来给参考振荡器分频,R计数器可预置,R的取值范围:8,64,128,256,512,1024,1160,2048。设置方法通过改变RA0、RA1、RA2的不同电平,接下来会讲到。 (5)它有两路鉴相信号输出,其中,ФR、ФV 用来输出鉴相误差信号,LD 用来输出相位锁定信号。 MC145152-2 的供电电压为3.0 V~9.0 V,采用28 脚双列封装形式。MC145152-2的原理框图如图1 所示 MC145152-2 的工作原理:参考振荡器信号经R 分频 器分频后形成fR 信号。压控振荡器信号经双模P/(P+ 1)分频器分频,再经A、N 计数器分频器后形成fV 信 号,fV=fVCO/(NP+A)。fR 信号和fV 信号在鉴相器中 鉴相,输出的误差信号(φR、φV)经低通滤波器形成 直流信号,直流信号再去控制压控振荡器的频率。 当整个环路锁定后,fV=fR 且同相,fVCO=(NP+A) fV=(NP+A)fR,便可产生和基准频率同样稳定度和 准确度的任意频率。原理框图如右图:

飞思卡尔锁相环

备战飞思卡尔智能车大赛.开始模块总结. 锁相环设置. 公式: PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1), fbus=PLLCLK/2 void INIT_PLL(void) { CLKSEL &= 0x7f; //选用外部时钟.准备设置锁相环 PLLCTL &= 0x8F; //禁止锁相环 SYNR = 0xc9; //设置SYNR REFDV = 0x81; //设置REFDV PLLCTL |=0x70; //锁相环使能 asm NOP; asm NOP; //两个机器周期缓冲时间 while(!(CRGFLG&0x08)); //等待锁相环锁定 CLKSEL |= 0x80; //设置锁相环为时钟源 } 飞思卡尔XS128的PLL锁相环详细设置说明——关于如何提高总线工作频率PLL锁相环就相当于超频 单片机超频的原因和PC机是个一道理。分频的主要原因是外设需要的工作频率往往远低于CPU/MEMORY 这也和PC机南北桥的原理类似。总线频率设置过程 1、禁止总中断 2、寄存器CLKSEL(时钟选择寄存器)的第七位置0 即CLKSEL_PLLSEL=0。选择时钟源为外部晶振OSCCLK(外接晶振频率) 在PLL(锁相环)程序执行前 内部总线频率为OSCCLK/2 3. PLLCTL_PLLON=1 打开PLL 4.设置SYNR 时钟合成寄存器 、REFDV 时钟分频寄存器 、POSTDIV三个寄存器的参数 5、_asm(nop) _asm(nop);加入两条空指令 使锁相环稳定 6、while(!(CRGFLG_LOCK==1));//时钟校正同步 7、CLKSEL_PLLSEL=1; 下面详细说一下频率的计算一、时钟合成寄存器SYNR寄存器结构 VCOFRQ[1:0]控制压控振动器VCO的增益 默认值为00 VCO的频率与VCOFRQ[1:0]对应表

软件设计方案(案例)

软件设计方案 用户界面设计规范 用户界面:又称人机界面,实现用户与计算机之间的通信,以控制计算机或进行用户与计算机之间的数据传送的系统部件。 GUI:即图形用户界面,一种可视化的用户界面,它使用图形界面代替正文界面。 本系统坚持图形用户界面(GUI)设计原则,界面直观、对用户透明。用户接触软件后对界面上对应的功能一目了然、不需要多少培训就可以方便地使用本应用系统。 1、界面设计介绍 界面设计是为了满足软件专业化标准化的需求而产生的对软件的使用界面进行美化优化规范化的设计分支。 1)软件启动封面设计 应使软件启动封面最终为高清晰度的图像,选用的色彩不宜超过256色,大小多为主流显示器分辨率的1/6大。启动封面上应该醒目地标注制作或支持的公司标志、产品商标、软件名称、版本号、网址、版权声明、序列号等信息,以树立软件形象,方便使用者或购买者在软件启动的时候得到提示。插图宜使用具有独立版权的、象征性强的、识别性高的、视觉传达效果好的图形,若使用摄影也应该进行数位处理,以形成该软件的个性化特征。如果是系列软件还将考虑整体设计的统一和延续性。 2)软件框架设计 软件的框架设计要复杂得多。软件框架设计应该简洁明快,尽量少用无谓的装饰,应该考虑节省屏幕空间,各种分辨率的大小,缩放时的状态和原则,并且为将来设计的按钮、菜单、标签、滚动条及状态栏预留位置。设计中将整体色彩组合进行合理搭配,将软件商标放在显著位置,主菜单应放在左边或上边,滚动条放在右边,状态栏放在下边,以符合视觉流程和用户使用心理。 3)软件按钮设计 软件按钮设计应该具有交互性,即应该有3到6种状态效果:点击前鼠标未放在上面时的状态;鼠标放在上面但未点击的状态;点击时状态;点击后鼠标未放在上面时的状态;不能点击时状态;独立自动变化的状态。按钮应具备简洁的图示效果,名称易懂,用词准确,能望文知意最好,让使用者产生功能关联反应,群组内按钮应该风格统一,功能差异大的按钮应该有所区别。 4)软件面板设计 软件面板设计应该具有缩放功能,面板应该对功能区间划分清晰,应该和对话框、弹出框等风格匹配,尽量节省空间,切换方便。 5)菜单设计

集成电路锁相环设计报告

锁相环CD4046设计频率合成器 ------集成电路考试实验设计报告 学校:福州大学 学院:物理与信息工程学院 班级:09级信息工程类2班 姓名:吴志强学号:110900636 姓名:吴鑫学号:110900635

目录 一、设计和制作任务 (3) 二、主要技术指标 (3) 三、确定电路组成方案 (3) 四、设计方法 (3) (一)、振荡源的设计 (3) (二)、N分频的设计 (3) (三)、10HZ标准信号源设计(即M分频的设计) (5) 五、锁相环参数设计 (6) 六、调试步骤 (6) 七、参考文献 (7) 附录:各芯片的管脚图 (7)

锁相环CD4046设计频率合成器 一、设计和制作任务 1.确定电路形式,画出电路图。 2.计算电路元件参数并选取元件。 3.组装焊接电路。 4.调试并测量电路性能。 5.写出课程设计报告书 二、主要技术指标 1.频率步进 10Hz 2.频率范围:1kHz—10kHz 3.电源电压 Vcc=5V 三、确定电路组成方案 原理框图如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N,从而就得到N倍参考频率的稳定输出。 晶体振荡器输出的信号频率f1, 经固定分频后(M分频)得到 基准频率f1’,输入锁相环的相 位比较器(PC)。锁相环的VCO 输出信号经可编程分频器(N分频) 后输入到PC的另一端,这两个信号进行相位比较,当锁相环路锁定后得到:f1/M=f1’=f2/N 故f2=Nf’1 (f’1为基准频率) 当N变化时,或者N/M变化时,就可以得到一系列的输出频率f2。 四、设计方法 (一)、振荡源的设计 用CMOS与非门和1M晶体组成 1MHz振荡器,如图14。图中Rf 使 F1工作于线性放大区。晶体的等效 电感,C1、C2构成谐振回路。C1、 C2可利用器件的分布电容不另接。 F1、F2、F3使用CD4049。 (二)、N分频的设计 用三片4522组成1——10kHZ频率合成器 CD1522的二一十进制1/N减计数器。其引脚见附录。其中D1-D4是预置端,Q1

锁相环的组成和工作原理

锁相环的组成和工作原理 时间:2011-11-23 来源:作者: 关键字:锁相环工作原理 1.锁相环的基本组成 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。 锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。 锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。 2.锁相环的工作原理 锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。 鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为: 式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。则模拟乘法器的输出电压uD为: 用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压uC(t)。即uC(t)为:

式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为: 上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,uc(t)为恒定值。当上式不等于零时,说明锁相环的相位还未锁定,输入信号和输出信号的频率不等,uc(t)随时间而变。 因压控振荡器的压控特性如图8-4-3所示,该特性说明压控振荡器的振荡频率ωu以ω0为中心,随输入信号电压uc(t)的变化而变化。该特性的表达式 上式说明当uc(t)随时间而变时,压控振荡器的振荡频率ωu也随时间而变,锁相环进入“频率牵引”,自动跟踪捕捉输入信号的频率,使锁相环进入锁定的状态,并保持ω0=ωi的状态不变。 8.4.2锁相环的应用 1.锁相环在调制和解调中的应用 (1)调制和解调的概念 为了实现信息的远距离传输,在发信端通常采用调制的方法对信号进行调制,收信端接收到信号后必须进行解调才能恢复原信号。 所谓的调制就是用携带信息的输入信号ui来控制载波信号uC的参数,使载波信号的某一个参数随输入信号的变化而变化。载波信号的参数有幅度、频率和位相,所以,调制有调幅(AM)、调频(FM)和调相(PM)三种。 调幅波的特点是频率与载波信号的频率相等,幅度随输入信号幅度的变化而变化;调频波的特点是幅度与载波信号的幅度相等,频率随输入信号幅度的变化而变化;调相波的特点是幅度与载波信号的幅度相等,相位随输入信号幅度的变化而变化。调幅波和调频波的示意图如图8-4-4所示。

DSPc55x锁相环初始化程序的理解

锁相环初始化程序的理解 1、ioport关键字用于对I/O空间进行寻址 2、dsp_lk=12 3、phase locked的意思是相位同步的意思;锁相技术:对于接收到的信号,仿制一个时钟信 号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。 4、PLL init()函数的理解 #include "5509.h" #include "util.h" DSPCLK dspclk; void PLL_Init(int freq) { int i; DSPCLK dspclk; //这是一个结构体类型,在#include "util.h"文件中有DSPCLK的定义 ioport unsigned int *clkmd; ioport unsigned int *sysr; clkmd=(unsigned int *)0x1c00; //时钟产生寄存器CLKMD的地址是0x1C00 sysr=(unsigned int *)0x07fd; //这个寄存器用于控制某些特定设备的功能,它的地址为0x7fd // Calculate PLL multiplier values (only integral multiples now) dspclk.clkin = DSP_CLKIN; //dspclk_clkin=12 dspclk.pllmult = (freq *2)/ dspclk.clkin; //pllmult=freq*2/12关于这个问题 //因此freq=pllmult*12/2,此时我们可以对照发现PLL DIV 默认值为1,而input frequency在util.h文件中给出值为12,但为什么一开始PLL DIV=1呢?下面这张图是spru317g的关于Reset Values of CLKMD Bits and The Effects,我们看到PLL DIV初始值是00,难道是和sysr寄存器中的CLK DIV有关?可sprs205文档中并未说明CLK DIV究竟复位后值为几。 但看下面的代码可知,PLL DIV是被置1的。刚刚所看的文件是DSP被复位后的初始值,而PLL DIV=1是此函数PLL_Init(int freq)的设置值,所以PLL DIV被认为是1 if(dspclk.pllmult>= 32)dspclk.pllmult=31; //如果倍频值超过最大的31,则将其视为31倍频 // Turn the PLL off使PLL处于旁路模式 *clkmd &= ~0x10; //pll enable = 0;旁路模式,就是PLL通过BYPASS DIV对输入信号进行分频 for(i=*clkmd&1; i!= 0 ;i=*clkmd&1); //查询clkmd的LOCK位,如果为1,PLL 工作于锁定模式,则继续等待,直到LOCK=0,PLL被旁路, // 初始化锁相环的一些标识位

锁相环常见问题解答要点

ADI官网下载了个资料,对于PLL学习和设计来说都非常实用的好资料,转发过来,希望对大家有帮助(原文链接 https://www.360docs.net/doc/b7523850.html,/zh/content/cast_faq_PLL/fca.html#faq_pll_01) ?参考晶振有哪些要求?我该如何选择参考源? ?请详细解释一下控制时序,电平及要求? ?控制多片PLL芯片时,串行控制线是否可以复用? ?请简要介绍一下环路滤波器参数的设置? ?环路滤波器采用有源滤波器还是无源滤波器? ?PLL对于VCO有什么要求?以及如何设计VCO输出功率分配器? ?如何设置电荷泵的极性? ?锁定指示电路如何设计? ?PLL对射频输入信号有什么要求? ?PLL芯片对电源的要求有哪些? ?内部集成了VCO的ADF4360-x,其VCO中心频率如何设定? ?锁相环输出的谐波? ?锁相环系统的相位噪声来源有哪些?减小相位噪声的措施有哪些? ?为何我测出的相位噪声性能低于ADISimPLL仿真预期值? ?锁相环锁定时间取决于哪些因素?如何加速锁定? ?为何我的锁相环在做高低温试验的时候,出现频率失锁? ?非跳频(单频)应用中,最高的鉴相频率有什么限制? ?频繁地开关锁相环芯片的电源会对锁相环有何影响? ?您能控制PLL芯片了么?,R分频和N分频配置好了么?

?您的晶振输出功率有多大?VCO的输出功率有多大? ?您的PFD鉴相极性是正还是负? ?您的VCO输出频率是在哪一点?最低频率?最高频率?还是中间的某一点?VCO 的控制电压有多大? ?您的PLL环路带宽和相位裕度有多大? ?评价PLL频率合成器噪声性能的依据是什么? ?小数分频的锁相环杂散的分布规律是什么? ?到底用小数分频好还是整数分频好? ?ADI提供的锁相环仿真工具ADISimPLL支持哪些芯片,有什么优点? ?分频–获得高精度时钟参考源? ?PLL,VCO闭环调制,短程无线发射芯片? ?PLL,VCO开环调制? ?时钟净化----时钟抖动(jitter)更小? ?时钟恢复(Clock Recovery)? 问题:参考晶振有哪些要求?我该如何选择参考源? 答案:波形:可以使正弦波,也可以为方波。 功率:满足参考输入灵敏度的要求。

PLL锁相环程序

飞思卡尔XS128系列(一)PLL锁相环 通俗点说,设置PLL锁相环就相当于超频,单片机超频的原因和PC机是一个道理。分频的主要原因是外设需要的工作频率往往远低于CPU/MEMORY,这也和PC机南北桥的原理类似。 相对来说,PLL锁相环的设置还是比较简单的,因为东西很死,完全可以照搬。只是大家也不要太贪,设置太高相对来说不够稳定,进行过PC机超频的应该很有体会,一般我们现在用的XS128我觉得设置在80MHz是比较合适的,相比前几届比赛用的DG128,这个频率已经蛮高的了。还有就是SYNR,REFDV只有在CLKSEL_PLLSEL=0的情况下才能写入,不过这是系统默认状态。 多半大家可能还会有以下几点疑问: 1.PLL锁相环怎么设置? 答:通过写REFDV(CRG参考分频寄存器)和SYNR(CRG合成器寄存器)进行设置 2.代码里while(!CRGFLG_LOCK);这句是干什么的? 答:时钟校正同步 3.为什么代码中会有多多少少的几句空语句? 答:锁相环从设定到最后稳定还是需要一点点时间的,所以需要加几条空指令 /*************************************************************************** ***********

------------------------------------ Code Warrior 5.0 Target : MC9S12XS128 Crystal: 16.000Mhz ============================================ 本程序主要包括以下功能: 设定系统工作在xxMHZ bus clock时钟下; by:庞辉 **************************************************************************** *************/ #include

PLL(锁相环)电路原理及设计 [收藏]

PLL(锁相环)电路原理及设计[收藏] PLL(锁相环)电路原理及设计 在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。 一PLL(锁相环)电路的基本构成 PLL(锁相环)电路的概要 图1所示的为PLL(锁相环)电路的基本方块图。此所使用的基准信号为稳定度很高的晶体振荡电路信号。 此一电路的中心为相位此较器。相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。 (将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。) 利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。 PLL(锁相环)可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。 只要是基准频率的整数倍,便可以得到各种频率的输出。 从图1的PLL(锁相环)基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。在此,假设基准振荡器的频率为fr,VCO的频率为fo。 在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。此时的相位比较器的输出PD 会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。相反地,如果frlt;fo时,会产生负脉波信号。

一个软件工程设计示例3.详细设计说明书

密级: 文档编号:第版 分册名称: 第册/共册 校级(公共课)学生成绩管理系统 详细设计说明书 1.00版 中南大学(某专业某年级某人)

详细设计说明书 1.引言 (3) 1.1编写目的 (3) 1.2项目背景 (3) 1.3定义 (3) 1.4参考资料 (3) 2.总体设计 (4) 2.1需求概述 (4) 2.2软件结构 (4) 3.程序描述 (4) 3.1数据库模块 (9) 3.2成绩录入模块 (14) 3.3统计打印模块 (20) 4. 接口设计 (22) 4.1外部接口 (22) 4.2内部接口 (23) 5. 数据库设计 (23)

1.引言 1.1编写目的 为明确软件需求、安排项目规划与进度、组织软件开发与测试,撰写本文档。 本文档供项目经理、设计人员、开发人员参考。 1.2项目背景 a.项目的委托单位:中南大学 开发单位:李明 主管部门:中南大学信息学院 b.该软件系统与其他 1. 本软件系统的名称:校级(公共课)学生成绩管理系统 2. 该软件系统同其他系统或其他机构的基本的相互来往关系:该系统基于IE浏览器,版本为6.0及以上,支持windows系列平台。 1.3定义 定义关键词如下: HTTP —— Hyper Text Transfer Protocol.(超文本传输协议) IIS —— Internet 信息服务. HTML —— Hyper Text Markup Language(超文本标记语言). ASP ——Active Server Pages ODBC ——开放数据库连接 ADO ――活动存储对象 IPO —— input & process & output(输入、处理、输出) CGI―― Common GateWay interface (公用网关接口技术)

集成电路课程设计——锁相环

集 成 电 路 实 验 报 告 学号:110800316 姓名:苏毅坚指导老师:罗国新 2011年1月

锁相环CD4046设计频率合成器 实验目的:设计一个基于锁相环CD4046设计频率合成器 范围是10k~100K,步进为1K 设计和制作步骤: 确定电路形式,画出电路图。 计算电路元件参数并选取元件。 组装焊接电路。 调试并测量电路性能。 确定电路组成方案 原理框图如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N,从而就得到N倍参考频率的稳定输出。 晶体振荡器输出的信号频率f1, 经固定分频后(M分频)得到 基准频率f1’,输入锁相环的相 位比较器(PC)。锁相环的VCO 输出信号经可编程分频器(N分频) 后输入到PC的另一端,这两个信号进行相位比较,当锁相环路锁定后得到:f1/M=f1’=f2/N 故f2=Nf’1 (f’1为基准频率) 当N变化时,就可以得到一系列的输出频率f2。 设计方法 (一)、振荡源的设计 用CMOS与非门和1M晶体组成 1MHz振荡器,如图14。图中Rf 使 F1工作于线性放大区。晶体的等效 电感,C1、C2构成谐振回路。C1、 C2可利用器件的分布电容不另接。 F1、F2、F3使用CD4049。 (二)、N分频的设计 N分频采用CD40103进行分频。CD40103是BCD码8位分频器。采用8位拨码开关控制分频大小。输入的二进制大小即为分频器N分频。图中RP1为1K排阻

(三)、1KHZ标准信号源设计(即M分频的设计) 根据4518的输出波形图,可以看出4518包含二分频、四分频、十分频,用二片CD4518(共4个计数器)组成一个1000分频器,也就是三个十分频器,这样信号变为2Khz.再经过双D触发器,这样就可把2MHz的晶振信号变成500hz 的标准信号。如下图所示: (四) 4046锁相环的设计锁相环4046为主芯片。电路图如下:500Hz 信号从14脚输入。3 脚4脚接N分频电路,即40103分频电路。13脚接低通滤波器。 本设计中,M固定,N可变。基准频率f’1 定为1KHz,改变N值,使N=1~999,则可产生 f2=1KHz—999KHz的频率范围。 锁相环锁存范围: fmax=100KHz fmin=1KHz