FPGA设计中有关时钟分析的相关总结

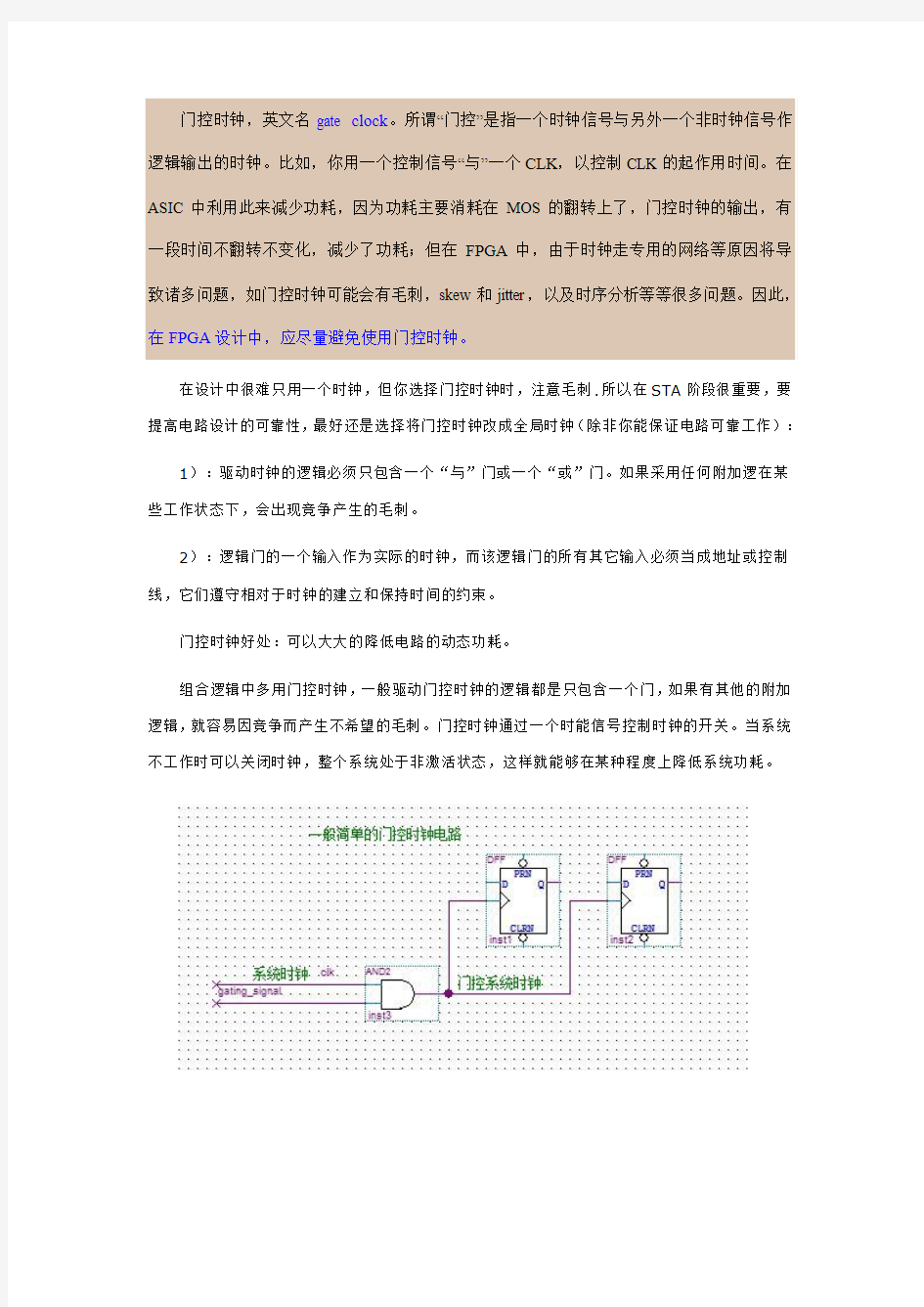

门控时钟,英文名gate clock。所谓“门控”是指一个时钟信号与另外一个非时钟信号作逻辑输出的时钟。比如,你用一个控制信号“与”一个CLK,以控制CLK的起作用时间。在ASIC中利用此来减少功耗,因为功耗主要消耗在MOS的翻转上了,门控时钟的输出,有一段时间不翻转不变化,减少了功耗;但在FPGA中,由于时钟走专用的网络等原因将导致诸多问题,如门控时钟可能会有毛刺,skew和jitter,以及时序分析等等很多问题。因此,在FPGA设计中,应尽量避免使用门控时钟。

在设计中很难只用一个时钟,但你选择门控时钟时,注意毛刺.所以在STA阶段很重要,要提高电路设计的可靠性,最好还是选择将门控时钟改成全局时钟(除非你能保证电路可靠工作):1):驱动时钟的逻辑必须只包含一个“与”门或一个“或”门。如果采用任何附加逻在某些工作状态下,会出现竞争产生的毛刺。

2):逻辑门的一个输入作为实际的时钟,而该逻辑门的所有其它输入必须当成地址或控制线,它们遵守相对于时钟的建立和保持时间的约束。

门控时钟好处:可以大大的降低电路的动态功耗。

组合逻辑中多用门控时钟,一般驱动门控时钟的逻辑都是只包含一个门,如果有其他的附加逻辑,就容易因竞争而产生不希望的毛刺。门控时钟通过一个时能信号控制时钟的开关。当系统不工作时可以关闭时钟,整个系统处于非激活状态,这样就能够在某种程度上降低系统功耗。

然而,使用门控时钟并不符合同步设计的思想,它可能会影响设计的实现和验证。单纯从功能上看,使用使能时钟替代门控时钟是一个不错的选择;但是使能时钟在使能信号关闭时,时钟信号仍然在工作,它无法像门控时钟那样降低系统的功耗。

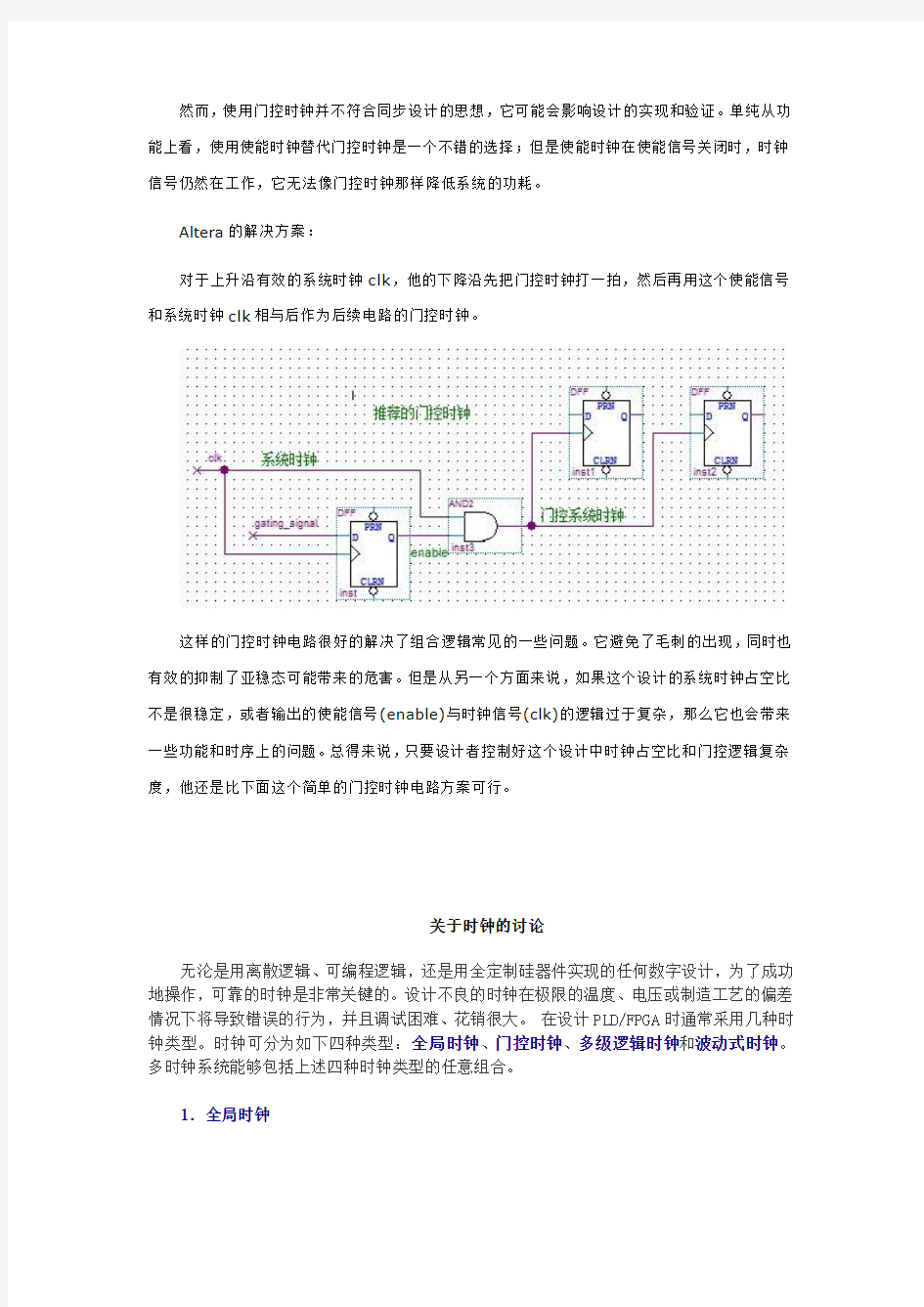

Altera的解决方案:

对于上升沿有效的系统时钟clk,他的下降沿先把门控时钟打一拍,然后再用这个使能信号和系统时钟clk相与后作为后续电路的门控时钟。

这样的门控时钟电路很好的解决了组合逻辑常见的一些问题。它避免了毛刺的出现,同时也有效的抑制了亚稳态可能带来的危害。但是从另一个方面来说,如果这个设计的系统时钟占空比不是很稳定,或者输出的使能信号(enable)与时钟信号(clk)的逻辑过于复杂,那么它也会带来一些功能和时序上的问题。总得来说,只要设计者控制好这个设计中时钟占空比和门控逻辑复杂度,他还是比下面这个简单的门控时钟电路方案可行。

关于时钟的讨论

无沦是用离散逻辑、可编程逻辑,还是用全定制硅器件实现的任何数字设计,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压或制造工艺的偏差情况下将导致错误的行为,并且调试困难、花销很大。在设计PLD/FPGA时通常采用几种时钟类型。时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。

1.全局时钟

对于一个设计项目来说,全局时钟(或同步时钟)是最简单和最可预测的时钟。在PLD/FPGA设计中最好的时钟方案是:由专用的全局时钟输入引脚驱动的单个主时钟去钟控设计项目中的每一个触发器。只要可能就应尽量在设计项目中采用全局时钟。PLD/FPGA都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。这种全局时钟提供器件中最短的时钟到输出的延时。

图1 全局时钟

A 建立时间Tsu

建立时间(setup time):是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被输入触发器。

B保持时间Th

保持时间(hold time):是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被输入触发器。

图1 示出全局时钟的实例。图1 定时波形示出触发器的数据输入D[1..3]应遵守建立时间和保持时间的约束条件。建立和保持时间的数值在PLD数据手册中给出,也可用软件的定时分析器计算出来。如果在应用中不能满足建立和保持时间的要求,则必须用时钟同步输入信号(参看下一章“异步输入”)。(最好的方法是用全局时钟引脚去钟控PLD内的每一个寄存器,于是数据只要遵守相对时钟的建立时间tsu和保持时间th)

2.门控时钟

在许多应用中,整个设计项目都采用外部的全局时钟是不可能或不实际的。PLD具有乘积项逻辑阵列时钟(即时钟是由逻辑产生的),允许任意函数单独地钟控各个触发器。然而,当你用阵列时钟时,应仔细地分析时钟函数,以避免毛刺。

通常用阵列时钟构成门控时钟。门控时钟常常同微处理器接口有关,用地址线去控制写脉冲。然而,每当用组合函数钟控触发器时,通常都存在着门控时钟。如果符合下述条件,门控时钟可以象全局时钟一样可靠地工作:

1.驱动时钟的逻辑必须只包含一个“与”门或一个“或”门。如果采用任何附加逻在某些工作状态下,会出现竞争产生的毛刺。

2.逻辑门的一个输入作为实际的时钟,而该逻辑门的所有其它输入必须当成地址或控制线,它们遵守相对于时钟的建立和保持时间的约束。

图2和图3 是可靠的门控时钟的实例。在图2 中,用一个“与”门产生门控时钟,在图3 中,用一个“或”门产生门控时钟。在这两个实例中,引脚nWR和nWE考虑为时钟引脚,引脚ADD[o..3]是地址引脚,两个触发器的数据是信号D[1..n]经随机逻辑产生的。

图2 “与”门门控时钟

图3 “或”门门控时钟

图2和图3 的波形图显示出有关的建立时间和保持时间的要求。这两个设计项目的地址线必须在时钟保持有效的整个期间内保持稳定(nWR和nWE是低电平有效)。如果地址线在规定的时间内未保持稳定,则在时钟上会出现毛刺,造成触发器发生错误的状态变化。另一方面,数据引脚D[1..n]只要求在nWR和nWE的有效边沿处满足标准的建立和保持时间的规定。

我们往往可以将门控时钟转换成全局时钟以改善设计项目的可靠性。图4 示出如何用全局时钟重新设计图2 的电路。地址线在控制D触发器的使能输入,许多PLD设计软件,如MAX+PLUSII软件都提供这种带使能端的D触发器。当ENA为高电平时,D输入端的值被钟控到触发器中:当ENA为低电平时,维持现在的状态。

图4 “与”门门控时钟转化成全局时钟

图4 中重新设计的电路的定时波形表明地址线不需要在nWR有效的整个期间内保持稳定;而只要求它们和数据引脚一样符合同样的建立和保持时间,这样对地址线的要求就少很多。图给出一个不可靠的门控时钟的例子。3位同步加法计数器的RCO输出用来钟控触发器。

然而,计数器给出的多个输入起到时钟的作用,这违反了可靠门控时钟所需的条件之一。在产生RCO信号的触发器中,没有一个能考虑为实际的时钟线,这是因为所有触发器在几乎相同的时刻发生翻转。而我们并不能保证在PLD/FPGA内部QA,QB,QC到D触发器的布线长短一致,因此,如图5 的时间波形所示,在器从3计到4时,RCO线上会出现毛刺(假设QC 到D触发器的路径较短,即QC的输出先翻转)。

图5 不可靠的门控时钟

(定时波形示出在计数器从3到4改变时,RCO信号如何出现毛刺的)

图6 给出一种可靠的全局钟控的电路,它是图5不可靠计数器电路的改进,RCO控制D 触发器的使能输入。这个改进不需要增加PLD的逻辑单元。

图6 不可靠的门控时钟转换为全局时钟

(这个电路等效于图5电路,但却可靠的多)

3.多级逻辑时钟

当产生门控时钟的组合逻辑超过一级(即超过单个的“与”门或“或”门)时,证设计项目的可靠性变得很困难。即使样机或仿真结果没有显示出静态险象,但实际上仍然可能存在着危险。通常,我们不应该用多级组合逻辑去钟控PLD设计中的触发器。

图7 给出一个含有险象的多级时钟的例子。时钟是由SEL引脚控制的多路选择器输出的。多路选择器的输入是时钟(CLK)和该时钟的2分频(DIV2)。由图7 的定时波形图看出,在两个时钟均为逻辑1的情况下,当SEL线的状态改变时,存在静态险象。险象的程度取决于工作的条件。多级逻辑的险象是可以去除的。例如,你可以插入“冗余逻辑”到设计项目中。然而,PLD/FPGA编译器在逻辑综合时会去掉这些冗余逻辑,使得验证险象是否真正被去除变得困难了。为此,必须应寻求其它方法来实现电路的功能。

图7 有静态险象的多级时钟

图8 给出图7 电路的一种单级时钟的替代方案。图中SEL引脚和DIV2信号用于使能D触发器的使能输入端,而不是用于该触发器的时钟引脚。采用这个电路并不需要附加PLD 的逻辑单元,工作却可靠多了。不同的系统需要采用不同的方法去除多级时钟,并没有固定的模式。

图7 无静态险象的多级时钟

(这个电路逻辑上等效于图7,但却可靠的多)

4.行波时钟

另一种流行的时钟电路是采用行波时钟,即一个触发器的输出用作另一个触发器的时钟输入。如果仔细地设计,行波时钟可以象全局时钟一样地可靠工作。然而,行波时钟使得与电路有关的定时计算变得很复杂。行波时钟在行波链上各触发器的时钟之间产生较大的时间偏移,并且会超出最坏情况下的建立时间、保持时间和电路中时钟到输出的延时,使系统的实际速度下降。

用计数翻转型触发器构成异步计数器时常采用行波时钟,一个触发器的输出钟控下一个触发器的输入,参看图9 同步计数器通常是代替异步计数器的更好方案,这是因为两者需要同样多的宏单元而同步计数器有较快的时钟到输出的时间。图10 给出具有全局时钟的同步计数器,它和图9 功能相同,用了同样多的逻辑单元实现,却有较快的时钟到输出的时间。几乎所有PLD开发软件都提供多种多样的同步计数器。

图9 行波时钟

图10 行波时钟转换成全局时钟

(这个3位计数器是图9异步计数器的替代电路,它用了同样的3个宏单元,但有更短的时钟到输出的延时)

5. 多时钟系统

许多系统要求在同一个PLD内采用多时钟。最常见的例子是两个异步微处理器器之间的接口,或微处理器和异步通信通道的接口。由于两个时钟信号之间要求一定的建立和保持时间,所以,上述应用引进了附加的定时约束条件。它们也会要求将某些异步信号同步化。

图11 给出一个多时钟系统的实例。CLK_A用以钟控REG_A,CLK_B用于钟控REG_B,由于REG_A驱动着进入REG_B的组合逻辑,故CLK_A的上升沿相对于CLK_B的上升沿有建立时间和保持时间的要求。由于REG_B不驱动馈到REG_A的逻辑,CLK_B的上升沿相对于CLK_A没有建立时间的要求。此外,由于时钟的下降沿不影响触发器的状态,所以CLK_A和CLK_B的下降沿之间没有时间上的要求。,如图4,2.II所示,电路中有两个独立的时钟,可是,在它们之间的建立时间和保持时间的要求是不能保证的。在这种情况下,必须将电路同步化。图12 给出REG_A的值(如何在使用前)同CLK_B同步化。新的触发器REG_C由GLK_B 触控,保证REG_G的输出符合REG_B的建立时间。然而,这个方法使输出延时了一个时钟周期。

图ll 多时钟系统

(定时波形示出CLK_A的上升沿相对于CLK_B的上升沿有建立时间和保持时间的约束条件)

图12 具有同步寄存器输出的多时钟系统

(如果CLK_A和CLK_B是相互独立的,则REG—A的输出必须在它馈送到1REG_B之前,用REG_C同步化)

在许多应用中只将异步信号同步化还是不够的,当系统中有两个或两个以上非同源时钟的时候,数据的建立和保持时间很难得到保证,我们将面临复杂的时间问题。最好的方法是将所有非同源时钟同步化。使用PLD内部的锁项环(PLL或DLL)是一个效果很好的方法,但不是所有PLD都带有PLL、DLL,而且带有PLL功能的芯片大多价格昂贵,所以除非有特殊要求,一般场合可以不使用带PLL的PLD。这时我们需要使用带使能端的D触发器,并引入一个高频时钟。

图13 不同源时钟

如图13所示,系统有两个不同源时钟,一个为3MHz,一个为5MHz,不同的触发器使用不同的时钟。为了系统稳定,我们引入一个20MHz时钟,将3M和5M时钟同步化,如图15所示。 20M 的高频时钟将作为系统时钟,输入到所有触发器的的时钟端。3M_EN 和5M_EN将控制所有触发器的使能端。即原来接3M时钟的触发器,接20M时钟,同时3M_EN 将控制该触发器使能,原接5M时钟的触发器,也接20M时钟,同时5M_EN 将控制该触发器使能。这样我们就可以将任何非同源时钟同步化。

图13 同步化任意非同源时钟

(一个DFF和后面非门,与门构成时钟上升沿检测电路)

另外,异步信号输入总是无法满足数据的建立保持时间,容易使系统进入亚稳态,所以也建议设计者把所有异步输入都先经过双触发器进行同步化,详情可参阅这篇文章:Are Your PLD Metastable?。

小结:稳定可靠的时钟是系统稳定可靠的重要条件,我们不能够将任何可能含有毛刺的输出作为时钟信号,并且尽可能只使用一个全局时钟,对多时钟系统要注意同步异步信号和非同源时钟。

FPGA设计中的组合逻辑与时钟方案

在用HDL设计时,理解综合工具如何解释不同的HDL代码风格和预期结果是非常重要的。设计人员的代码风格会影响逻辑的利用率和时限性能。本文讨论一些基本的设计技术,确保FPGA最佳的综合结果,同时避免一些不可靠和不稳定的因素。设计人员应当认真设计组合逻辑以避免潜在的问题,同时应注意时钟方案保证同步功能。

组合逻辑结构

组合环路

组合环路是数字逻辑设计中不稳定性和不可靠性最常见的原因之一。在同步设计中,所有的反馈环路都应该包括寄存器。组合环路直接建立没有寄存器的反馈,违反了同步设计的原则。例如,当算术表达式的左边也出现在右边,就会发生组合循环。当把一个寄存器输出通过组合逻辑反馈给同一个寄存器的异步管脚时,也会产生组合环路。

组合环路是高风险的设计结构,这是因为:

● 组合环路的功能通常依靠环路逻辑的相对传播延迟。正如所讨论的,传播延迟可能改变,那么环路行为也可能发生改变。

● 在一些设计工具中,组合环路可能造成无尽的计算循环。大部分的工具会打断组合环路进行处理。设计流程中所用的不同工具会以不同的方式打断同样的环路,这样可能和设计初衷不一致。

延迟链

当两个以上连续的单输入单扇出节点引起延迟时,就会产生延迟链。通常,把反相器连在一起增加延迟。延迟链通常是由异步设计引入的,有时是用来解决其它组合逻辑引起的竞争冒险。FPGA延迟会随每次布局布线的变化而改变。延迟链可能引起不同的设计问题,包括增加了设计对工作条件的敏感性,减小了设计的可靠性,不利于移植到其它器件结构上。在设计中要避免使用延迟链,而应采用同步设计。

脉冲发生器和多频振荡器

设计者有时用延迟链来产生单个脉冲(脉冲发生器)或一系列脉冲(多频振荡器)。脉冲生成有两种常见的方式,这些技术完全依靠异步逻辑,应该避免:

● 触发信号送给一个两输入AND或OR门的输入,但给其中一个输入设计反相或延迟链。脉冲的宽度取决于直接进入门和经过延迟进入门的这两个通道的相对延迟。输入发生变换,这同样在组合逻辑上产生毛刺。这种技术可以用延迟链,人为地增加脉冲信号的宽度。

● 寄存器的输出经过一个延迟链驱动同一个寄存器的异步复位信号。本质上就是寄存器在经过一定延迟之后异步复位自己。

这些设计的主要问题是综合和布局布线软件很难确定、设置或验证脉冲的宽度。只有在布局布线之后,知道布线和传播延迟之后才能最后确定实际的脉冲宽度。所以,在编写HDL 代码时,很难可靠地确定脉冲的宽度,也无法用EDA工具来设置这个宽度。在所有的PVT 条件下,脉冲可能并不够宽。如果移植到不同的器件上,脉冲宽度就会改变。另外,静态时限分析并不能用来验证脉冲宽度,所以验证是非常困难的。

多频振荡器除了用组合环路,把电路变成振荡器外,还采用了"毛刺生成器"的方式来产生脉冲。因为它涉及到多个脉冲,所以这种结构所带来的问题比脉冲生成器要多得多。另外,当结构生成多个脉冲时,它们也会增加设计的频率。

在本例设计中,脉冲宽度总是等于时钟周期。这种脉冲生成器是可预测的,可以用时限分析还验证,而且易于移植到其它体系、器件或速度等级。

锁存器

在数字逻辑中,锁存器保留一个信号的值直到赋予其一个新的值。当设计者不打算使用锁存器,HDL代码也会暗指出锁存器来保存值。FPGA拥有大量的寄存器,因此基于锁存器的设计比基于寄存器的设计要占用更多的逻辑,性能降低。

锁存器会造成设计中的各种困难。虽然锁存器是和寄存器类似的存储单元,但是它们根本上是不同的。当锁存器工作在"feed-through"模式下,就是数据输入和输出的直接通路。输入数据的毛刺也会传送到输出。锁存器的时限本来就很不明确。例如在分析带有D锁存器的设计时,软件无法确定设计人员是否打算在时钟的前沿或后沿把数据输出。在一些情况下,只有最初的设计者才会知道设计的全部考虑,因而另一个设计者不可能很容易地移植设计或重用代码。

在设计组合逻辑时,某些代码风格可能产生窃て诘乃 嫫鳌@ 纾 盋ASE或IF语句没有覆盖所有可能的输入条件时,如果没有赋于新的值,就可能产生锁存器来保持输出结果。在IF或CASE表达中遗漏最后一条ELSE语句或WHEN OTHERS语句也可能产生锁存器。为了避免产生非预期的锁存器,必须将缺省CASE或最后的ELSE语句赋给一个"don't care"值。

时钟方案

内部生成的时钟

避免使用内部生成的时钟,因为它们可能引起设计中的功能和时限问题。由组合逻辑产生的时钟会引入毛刺会造成功能问题,而引入的延迟则会导致时限问题。

如果用组合逻辑的输出作为时钟信号或异步复位信号,那么在设计中就会出现毛刺。在同步设计中,寄存器输入数据的毛刺是很正常的,对设计没有什么影响。然而,时钟输入(或寄存器异步输入)上的毛刺或脉冲则会导致严重的后果。窄毛刺可能违反了寄存器的最小脉冲宽带要求。如果当毛刺到达时钟输入时寄存器的输入数据正在变化,那么也无法满足建立和保持时限要求。即使设计没有违反时限需求,寄存器输出可能意想不到地改变值,造成设计其它部分的功能不正常。

因为存在这些问题,所有在用组合逻辑输出作为时钟信号之前,必须加一级寄存器。这个寄存操作确保了组合逻辑生成的毛刺被阻挡在寄存器的数据输入端口上。

用于生成内部时钟的组合逻辑也会增加时钟线的延迟。在一些设计中,时钟线上的逻辑延迟可能会造成时钟偏移大于两个寄存器之间的数据通道的长度。如果时钟偏移大于数据延迟,寄存器的时限参数将无法满足,设计也无法正确运行。为了减小时钟域上的时钟偏移,(如果可能的话)应把生成的时钟指定到FPGA中一个高扇出和低偏移的时钟树上。使用低偏移时钟树如Altera的全局信号,就可以帮助减小该信号的整个时钟偏移。在Altera的Quartus II软件,设计人员可以用Assignment Editor把一个节点指定为全局信号。

分频时钟

一些设计要分频主时钟产生工作时钟。一些FPGA为时钟分频提供专门的电路,如Altera 的锁相环(PLL)。使用PLL电路会避免有异步时钟分频逻辑引入的一些问题。

当使用逻辑分频主时钟时,总要使用同步计数器或状态机。另外,在设计中总是用寄存器直接产生分频时钟信号。设计不再对计数器或状态机进行译码来产生时钟信号。这种实现通常会造成毛刺。

波纹计数器

FPGA设计者经常实现波纹计数器来对时钟进行二次幂分频,因为计数器易于设计而且比同步计数器占用更少的逻辑门。波纹计数器使用级联寄存器,每个寄存器的输出管脚进入下一级寄存器的时钟管脚。因为寄存器在每级上建立了波纹时钟,这种级联方式会造成一些问题。这些波纹时钟必须和时限分析那样处理,这可能很困难并在综合和布局步行工具中设置合适的时限需求。设计人员需要努力避免这些类型的结构,减轻验证压力。

复用时钟

时钟复用可以用不同的时钟源来作同一个逻辑功能。某些复用逻辑选择时钟源。例如,涉及多个频率标准的电信应用通常使用复用时钟。

给时钟信号增加复用逻辑可能会出现一些问题,但是复用时钟的需求根据不同的应用也大大不同。如果满足下列条件,则可以采用时钟复用:

● 初始化配置之后时钟复用逻辑不会变化。

● 设计用复用逻辑选择时钟进行测试。

● 切换时钟之后总是进行复位。

● 时钟切换产生暂时不正确的响应对设计没有什么影响。

如果设计没有经过复位就匆忙地切换时钟,设计就无法容忍暂时不正确的响应。那么必

须采用同步设计,这样才不会违反寄存器的时限,时钟信号也没有毛刺,没有竞争冒险或其它逻辑问题。

门控时钟

门控时钟用使能信号打开和关闭时钟信号,这个使能信号控制着某种门电路。当时钟关闭时,相应的时钟域被关闭,功能也暂停。门控时钟是减小功耗的强大技术。当门控时钟时,时钟树和寄存器不再触发,不消耗切换能量。

门控时钟不是同步方案,因此在某些情况下它能够大大地增加设计实现和验证工作,造成一些问题。门控时钟会造成时钟偏移,不利于器件的移植。这些时钟对毛刺也很敏感,造成设计无法工作。

从功能方面考虑,设计人员可以用同步时钟使能在纯同步方式下关闭时钟域。然而,当使用同步时钟使能方案时,时钟树一直触发,每个寄存器的内部电路仍在工作(虽然输出不改变值),它不减小功耗。因此,设计人员应该在绝大部分情况下使用下面归纳的同步方案。要降低更多的功耗,见推荐的时钟门控方案

同步时钟使能

要以同步方式关闭时钟域,褂猛 绞敝邮鼓堋T诰 蟛糠諪PGA中,器件寄存器上有时钟使能信号。该方案不会降低功耗,因为时钟树和内部电路一直在触发中,但是具有门控时钟同样的功能。在每个寄存器的输入数据前插入一个复用器,以载入新的数据或复制寄存器的输出。

推荐采用的时钟门控方式

只有当目标应用需要大量地降低功耗才有必要使用门控时钟。如果必须使用门控时钟,可以使用图5所示的安全的时钟门控技术来实现。

设计人员可以在时钟树的根部、叶或二者之间的某个位置门控一个时钟信号。因为时钟树在切换时会消耗能量,那么在根部生成时钟就可以关闭整个时钟树而不是沿着时钟树在叶子上门控时钟。

一个寄存器生成使能信号确保其没有毛刺和窄脉冲。设计在时钟的无效沿上钟控着生成使能信号进行门控的寄存器(在图5中,当门控的时钟是上升沿有效的情况下,门控寄存器要使用下降沿)。这种实现方案,一次开关时钟门只有一个输入会改变,这样就不会在输出上产生毛刺或窄脉冲。使用AND门门控上升沿有效的时钟。对于下降沿有效的时钟,则使用OR门来生成时钟,由正沿寄存器来存储使能信号。

在采用这种方案的时候,应该注意时钟的占空比,因为只有准时的操作才能生成有效的使能信号。如果生成使能信号的逻辑特别复杂,或者时钟的占空比极其不平衡,那么这种方案也可能会产生一些问题。然而,占空比和其它门控时钟方式相比,是一个微不足道的问题

世界电子元器件

FPGACPLD数字电路设计经验

FPGA/CPLD数字电路设计经验分享 摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高,并且系统的工作频率可以达到一个较高水平。 关键词:FPGA数字电路时序时延路径建立时间保持时间 1 数字电路设计中的几个基本概念: 1.1 建立时间和保持时间: 建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间 注:在考虑建立保持时间时,应该考虑时钟树向后偏斜的情况,在考虑建立时间时应该考虑时钟树向前偏斜的情况。在进行后仿真时,最大延迟用来检查建立时间,最小延时用来检查保持时间。 建立时间的约束和时钟周期有关,当系统在高频时钟下无法工作时,降低时钟频率就可以使系统完成工作。保持时间是一个和时钟周期无关的参数,如果设计不合理,使得布局布线工具无法布出高质量的时钟树,那么无论如何调整时钟频率也无法达到要求,只有对所设计系统作较大改动才有可能正常工作,导致设计效率大大降低。因此合理的设计系统的时序是提高设计质量的关键。在可编程器件中,时钟树的偏斜几乎可以不考虑,因此保持时间通常都是满足的。

基于FPGA的数字时钟的设计1

基于FPGA的数字时钟的设计课题: 基于FPGA的数字时钟的设计 学院: 电气信息工程学院 专业: 测量控制与仪器 班级 : 08测控(2)班 姓名 : 潘志东 学号 : 08314239 合作者姓名: 颜志林 2010 年12 月12 日

综述 近年来随着数字技术的迅速发展,各种中、大规模集成电路在数字系统、控制系统、信号处理等方面都得到了广泛的应用。这就迫切要求理工科大学生熟悉与掌握常用中、大规模集成电路功能及其在实际中的应用方法,除通过实验教学培养数字电路的基本实验方法、分析问题与故障检查方法以及双踪示波器等常用仪器使用方法等基本电路的基本实验技能外,还必须培养大学生工程设计与组织实验能力。 本次课程设计的目的在于培养学生对基本电路的应用与掌握,使学生在实验原理的指导下,初步具备基本电路的分析与设计能力,并掌握其应用方法;自行拟定实验步骤,检查与排除故障、分析与处理实验结果及撰写实验报告的能力。综合实验的设计目的就是培养学生初步掌握小型数字系统的设计能力,包括选择设计方案,进行电路设计、安装、调试等环节,运用所学知识进行工程设计、提高实验技能的实践。数字电子钟就是一种计时装置,它具有时、分、秒计时功能与显示时间功能;具有整点报时功能。 本次设计我查阅了大量的文献资料,学到了很多关于数字电路方面的知识,并且更加巩固与掌握了课堂上所学的课本知识,使自己对数字电子技术有了更进一步的认识与了解。

1、课题要求 1、1课程设计的性质与任务 本课程就是电子与信息类专业的专业的专业基础必修课——“数字电路”的配套实验课程。目的在于培养学生的理论联系实际,分析与解决问题的能力。通过本课程设计,使学生在理论设计、计算机仿真、指标调测、故障排除等方面得到进一步的训练,加强学生的实践能力。学生通过设计、仿真、调试、撰写设计报告等过程,培养学生的动手能力与严谨的工作作风。 1、2课程设计的基本技术要求 1)根据课题要求,复习巩固数字电路有关专业基础知识; 2)掌握数字电路的设计方法,特别就是熟悉模块化的设计思想; 3) 掌握QUARTUS-2软件的使用方法; 4) 熟练掌握EDA工具的使用,特别就是原理图输入,波形仿真,能对仿真波形进行分析; 5) 具备EDA技术基础,能够熟练使用VHDL语言进行编程,掌握层次化设计方法; 6) 掌握多功能数字钟的工作原理,学会不同进制计数器及时钟控制电路的设计方法; 7) 能根据设计要求对设计电路进行仿真与测试; 8) 掌握将所设计软件下载到FPGA芯片的下载步骤等等。 9) 将硬件与软件连接起来,调试电路的功能。 1、3课程设计的功能要求 基本功能:能进行正常的时、分、秒计时功能,分别由6个数码管显示24小时,60分钟,60秒钟的计数器显示。 附加功能:1)能利用硬件部分按键实现“校时”“校分”“清零”功能; 2)能利用蜂鸣器做整点报时:当计时到达59’59’’时开始报时, 鸣叫时间1秒钟; 3)定时闹铃:本设计中设置的就是在七点时进行闹钟功能,鸣叫 过程中,能够进行中断闹铃工作。 本人工作:负责软件的编程与波形的仿真分析。 2、方案设计与分析

FPGA的数字电路设计综述

封面

作者:PanHongliang 仅供个人学习 1 数字电子基础4 1.1 导读4 1.2 数字电路概述4 1.2.1 数字信号与数字电路4 1.2逻辑函数及其表示方法5 1.2.1逻辑代数5

1.2.2逻辑函数的表示方法及相互转换5 1.3逻辑函数的公式化简法6 1.3.1逻辑函数的不同表达方式6 1.3.2逻辑函数的公式化简法6 1.4逻辑函数的卡诺图化简法7 1.4.1逻辑函数的最小项及其表达式7 1.4.2逻辑函数的卡诺图表示法7 1.4.3用卡诺图化简逻辑函数8 2逻辑门电路8 2.1 导读8 2.1逻辑门电路9 2.1.1三种基本门电路9 2.1.2 DTL与非门10 2.2 TTL逻辑门电路10 2.2.1 TTL与非门的电路结构10 2.2.2 TTL与非门的工作原理10 2.3 其他类型的TTL门电路11 2.3.1集电极开路与非门(OC门)11 2.3.2三态门(TSL门)11 2.4多余输入端的处理12 3组合逻辑13 3.1 导读13 3.2组合逻辑电路基础13 3.2.1组合逻辑电路的基本概念13 3.2.2组合逻辑电路的分析方法14 3.2.3组合逻辑电路的设计方法14 3.3常用组合逻辑建模14 3.3.1编码器14 3.3.2 译码器和数据分配器16 3.3.3数据选择器18 3.3.4数值比较器19 3.3.5加法器(减法器)20 3.3.6乘法器22 3.3.7除法器24 4触发器24 4.1导读24 4.2触发器的电路结构及工作原理24 4.2.1基本RS触发器(异步)24 4.2.2同步RS触发器25 4.2.3主从触发器和边沿触发器26 4.3触发器的功能分类及相互转换27 4.3.1触发器的功能分类27 4.3.2不同类型时钟触发器的相互转换28 5时序逻辑电路29

基于FPGA的数字时钟的设计1

基于FPGA 的数字时钟的设计 课 题: 基于FPGA 的数字时钟的设计 学 院: 电气信息工程学院 专 业 : 测量控制与仪器 班 级 : 08测控(2)班 姓 名 : 潘 志 东 学 号 : 08314239 合作者姓名: 颜志林 2010 年 12 月 12 日

综述 近年来随着数字技术的迅速发展,各种中、大规模集成电路在数字系统、控制系统、信号处理等方面都得到了广泛的应用。这就迫切要求理工科大学生熟悉和掌握常用中、大规模集成电路功能及其在实际中的应用方法,除通过实验教学培养数字电路的基本实验方法、分析问题和故障检查方法以及双踪示波器等常用仪器使用方法等基本电路的基本实验技能外,还必须培养大学生工程设计和组织实验能力。 本次课程设计的目的在于培养学生对基本电路的应用和掌握,使学生在实验原理的指导下,初步具备基本电路的分析和设计能力,并掌握其应用方法;自行拟定实验步骤,检查和排除故障、分析和处理实验结果及撰写实验报告的能力。综合实验的设计目的是培养学生初步掌握小型数字系统的设计能力,包括选择设计方案,进行电路设计、安装、调试等环节,运用所学知识进行工程设计、提高实验技能的实践。数字电子钟是一种计时装置,它具有时、分、秒计时功能和显示时间功能;具有整点报时功能。 本次设计我查阅了大量的文献资料,学到了很多关于数字电路方面的知识,并且更加巩固和掌握了课堂上所学的课本知识,使自己对数字电子技术有了更进一步的认识和了解。

1、课题要求 1.1课程设计的性质与任务 本课程是电子与信息类专业的专业的专业基础必修课——“数字电路”的配套实验课程。目的在于培养学生的理论联系实际,分析和解决问题的能力。通过本课程设计,使学生在理论设计、计算机仿真、指标调测、故障排除等方面得到进一步的训练,加强学生的实践能力。学生通过设计、仿真、调试、撰写设计报告等过程,培养学生的动手能力和严谨的工作作风。 1.2课程设计的基本技术要求 1)根据课题要求,复习巩固数字电路有关专业基础知识; 2)掌握数字电路的设计方法,特别是熟悉模块化的设计思想; 3) 掌握QUARTUS-2软件的使用方法; 4) 熟练掌握EDA工具的使用,特别是原理图输入,波形仿真,能对仿真波形进行分析; 5) 具备EDA技术基础,能够熟练使用VHDL语言进行编程,掌握层次化设计方法; 6) 掌握多功能数字钟的工作原理,学会不同进制计数器及时钟控制电路的设计方法; 7) 能根据设计要求对设计电路进行仿真和测试; 8) 掌握将所设计软件下载到FPGA芯片的下载步骤等等。 9) 将硬件与软件连接起来,调试电路的功能。 1.3课程设计的功能要求 基本功能:能进行正常的时、分、秒计时功能,分别由6个数码管显示24小时,60分钟,60秒钟的计数器显示。 附加功能:1)能利用硬件部分按键实现“校时”“校分”“清零”功能; 2)能利用蜂鸣器做整点报时:当计时到达59’59’’时开始报时,鸣叫时间1秒钟; 3)定时闹铃:本设计中设置的是在七点时进行闹钟功能,鸣叫过程中,能够进行中断闹铃工作。 本人工作:负责软件的编程与波形的仿真分析。 2、方案设计与分析

verilog数字钟设计FPGA

一、课程设计目标 1. 熟悉并掌握verilog 硬件描述语言 ;

是 总模块: module clock(clk,reset,MODE,Alarm_ctr,BT2,H12_24,DSH,DSL,DMH,DML,DHH,DHL,dian,bao _signal,nao_signal); input clk;//50MHz input reset,MODE,Alarm_ctr,BT2,H12_24;//复位键,模式选择按钮,闹钟开关档,调节按钮,12—24小时切换档 output [7:0]DMH,DML,DHH,DHL; //4个数码管显示输入信号 output dian,bao_signal,nao_signal; //时分间隔点,报时信号,闹钟信号 output [3:0]DSH,DSL; //秒钟输出信号 wire [3:0] SH,SL,MH,ML,HH,HL; wire [3:0] LED_mode; wire [3:0] HH12,HL12,HH24,HL24,MH24,ML24,SH24,SL24;

wire [3:0] set_HH,set_HL,set_MH,set_ML; wire _1HZ,_10ms,_250ms,_500ms; wire Keydone1; wire Keydone2; wire co1,co11,co111,co2,co22,co222,set_co2; wire [3:0]mode_flag; assign dian=1'b0; devide_f u1(_1HZ,_10ms,_250ms,_500ms,reset,clk); //分频,得到4种不同频率的时钟信号 key_press u2(_10ms,MODE,Keydone1); //模式档按钮去抖动 key_press u20(_10ms,BT2,Keydone2); //调节按钮去除抖动 mode u3(Keydone1,mode_flag); //通过模式按钮产生不同模式second u4(_1HZ,reset,mode_flag,Keydone2,SH24,SL24,co1); //秒计时 minute u5(co11,reset,MH24,ML24,co2); //分计时 hour u6(co22,reset,HH24,HL24); //小时计时 SEG7_LUT u7(DML,ML); //4个数码管显示

基于FPGA 的数字系统设计

《基于FPGA的数字系统设计》项目设计项目名称: 电子密码锁 姓名:蒋流洲 院系:应用技术学院 专业: 09电子信息工程(应电应本) 学号: 200915254137 指导教师:徐正坤 完成时间: 2011年6月 30日

目录 1 项目名称、内容与要求………………………………………… 1页1.1 设计内容……………………………………………………… 1页 1.2 具体要求……………………………………………………… 1页 2 系统整体架构(Architecture Description)…………………1页2.1 设计思路……………………………………………………… 1页2.2 系统原理(包含:框图等阐述)与设计说明等内容…………2页 2.3 创新点与原创性内容………………………………………… 3页 3 系统设计 (含HDL 或原理图输入设计)……………………… 3页注:此部分包含主要逻辑单元、模块、源代码等内容 3.1 HDL 代码……………………………………………………… 3页 3.2 系统整体电路图(或RTL 级电路图)……………………… 11页 4 系统仿真(Simulation Waveform)……………………………12页 5 FPGA 实现(FPGA Implementation)………………………… 12页注:此处应包含硬件验证、操作过程、结果等说明 6 总结(Closing)……………………………………………… 15页参考书目(Reference):………………………………………… 16页

1项目名称、内容与要求 1.1 设计内容 实验板上有10个按键k1~k10,其中k1~k10作为密码输入按键,k10作为复位按键,一便重新开始输入的密码。当然,这个电子密码锁与实际的电子密码锁的设计有一些不一样,也许实际的电子密码锁并不设置复位按键,而是当密码输入错误后,延长很长一段时间才接受新密码的输入。 假设电子密码锁的密码为四位数3216。利用实验板上的一个数码管显示输入密码次数,当输入密码正确时,在数码管上显示字符“H”;当输入密码不正确时,在数码管上显示字符“E”。 1.2 具体要求 1﹞.具有密码输入功能。 2﹞.设置复位按键,以便重新输入新的密码。 3﹞.在数码管上显示输入密码次数。 4﹞.拒绝接受超过规定次数的密码输入信号。 5﹞.当密码输入正确时,在数码管上显示字符“H”;当密码输入不正确时,在数码管上显示字符“E”; 2 系统整体架构 2.1 设计思路 电子密码锁在生活中十分常见,在这我将设计一个具有较低成本的电子密码锁,本文讲述了我整个设计过程及收获。讲述了电子密码锁的的工作原理以及各个模块的功能,并讲述了所有部分的设计思

基于FPGA的数字电子时钟设计与实现

课程设计(论文)说明书 题目:基于FPGA的数字电子时 钟设计 院(系):信息与通信学院 专业:微电子学 学生姓名: 学号:0900240115 指导教师: 职称:实验师 2012 年12 月25 日

一、所用设备与器材 1.1仪器设备 使用仪器设备有FPGA DE2-70开发板、PC机、信号发生器。 图1 FPGA DE2-70开发板图 二.系统方案 2.1 设计思想 利用数字电子技术、EDA设计方法、FPGA等技术,设计、仿真并实现一个基于FPGA的数字电子时钟基本功能,其基本组成框图如图1所示,振荡器采用ALTERA的DE2-70实验板的50MHz输出,分频器将50MHz的方波进行分频进而得到1Hz的标准秒脉冲,时、分、秒计时模块分别由二十四进制时计数器、六十进制分计数器和六十进制秒计数器完成,校时模块完成时和分的校正。扩展功能设计为倒计时功能,从59分55秒至59分59秒,每秒亮一盏灯报时。 2.1.1课题背景 20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力的推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能更进一步,产品更新换代的节奏也越来越快。 20世纪80年代末,出现了FPGA(Field Progrommable Gate Array),CAE 和CAD技术的应用更为广泛,它们在PCB设计的原理图输入,自动布局布线及PCB分析,以及逻辑设计,逻辑仿真布尔综合和化简等方面担任了重要的角色,

为电子设计自动化必须解决的电路建模,标准文档及仿真测试奠定了基础。硬件描述语言是EDA技术的重要组成部分,VHDL是作为电子设计主流硬件的描述语言。本论文就是应用VHDL语言来实现秒表的电路设计。VHDL语言是标准硬件描述语言,它的特点就是能形式化抽样表示电路结构及行为,支持逻辑设计中层次领域的描述,借用了高级语言的精巧结构简化电路描述,具有电路模拟与验证及保证设计的正确性,支持电路由高层向底层的综合变换,便于文档管理,易于理解和设计重用。 EDA技术是在电子CAD技术基础上发展起来的计算机软件系统,是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。 利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程在计算机上自动处理完成。 现在对EDA的概念或范畴用得很宽。包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。目前EDA 技术已在各大公司、企事业单位和科研教学部门广泛使用。例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。本文所指的EDA技术,主要针对电子电路设计、PCB设计和IC设计。EDA 设计可分为系统级、电路级和物理实现级。 用VHDL语言开发的流程: (1)文本编辑:用任何文本编辑器都可以进行,也可以用专用的HDL编辑环境。 通常VHDL文件保存为.vhd文件。 (2)功能仿真:将文件调入HDL仿真软件进行功能仿真,检查逻辑功能是否正确(也叫前仿真,对简单的设计可以跳过这一步,只在布线完 成以后,进行时序仿真)。 (3)逻辑综合:将源文件调入逻辑综合软件进行综合,即把语言综合成最简的布尔表达式和信号的连接关系。逻辑综合软件会生成.edf (edif)的EDA工业标准文件。 (4)布局布线:将.edf文件调入PLD厂家提供的软件中进行布线,即把设计好的逻辑安放到PLD/FPGA内。

数字电路的FPGA设计与实现基础篇

数字电路的FPGA设计与实现基础篇杨凡,邮箱lvfanzai@https://www.360docs.net/doc/d26031026.html, MSN:lvfanzai@https://www.360docs.net/doc/d26031026.html, 大家给点意见~~有助于我进一步的学习!谢谢! 2、基础篇: 2.1 组合逻辑: 2.1.1 三态门(总线) 三态门有:bufif0,bufif1,notif0,notif1。 总线是运算部件之间数据流通的公共通道,在硬线逻辑构成的运算电路 中只要电路的规模允许,可以比较自由地确定总线的宽度,可以提高数 据流通的速度。 2.1.2 异或门 xor A1(T,A,B); 2.1.3 编译码器:利用case进行编程(38译码器和83优先解码器的 编程比较简单仿真在这里就就不做说明) 2.1.4 全加器:(门级结构实现,数据流,过程语句) 数据流描述的4位加法器 Module adder4(a,b,cin,,cout,s); Input [3:0] a,b;Input cin;Output c;Output [3:0] s; Reg [3;0] s; Assign {c,s}=a+b+cin;//利用位拼接实现结果的进位 endmodule 2.1.5 多位串行进位加法器 多位串行进位加法器虽然简单但是速度较慢,一般使用超前进位加法器 2.1.6 数据选择器:(if else 语句,case语句描述实现) 多位的数据选择器大部分情况下我大部分代码都用case分支选择语句

很容易实现,另外还可以利用行为和数据流描述方式简单的组合逻辑编码也是一样的。 数据流描述的选择器(2选1) Module mux21(out,a,b,sel); Input a,b,sel; Output out; Assign out=sel?a:b;endmodule 2.1.7 数值比较器(直接比较两个数的大小可以利用上面数据选择器使用的数据流描述方法来实现);要具体比较出两者的关系利用以下代码仿真: module cmp(A,B,FA,FB,FE); parameter width=9; input [width:0] A,B; output [1:0] FA,FB,FE; assign FA=(A>B);// 当A大于B时FA输出为1 assign FB=(A 基于FPGA的数字时钟的设计课题:基于FPGA的数字时钟的设计 学院:电气信息工程学院 专业:测量控制与仪器 班级: 08测控(2)班 姓名:潘志东 学号: 08314239 合作者姓名:颜志林 2010 年12 月12 日 综述 近年来随着数字技术的迅速发展,各种中、大规模集成电路在数字系统、控制系统、信号处理等方面都得到了广泛的应用。这就迫切要求理工科大学生熟悉和掌握常用中、大规模集成电路功能及其在实际中的应用方法,除通过实验教学培养数字电路的基本实验方法、分析问题和故障检查方法以及双踪示波器等常用仪器使用方法等基本电路的基本实验技能外,还必须培养大学生工程设计和组织实验能力。 本次课程设计的目的在于培养学生对基本电路的应用和掌握,使学生在实验原理的指导下,初步具备基本电路的分析和设计能力,并掌握其应用方法;自行拟定实验步骤,检查和排除故障、分析和处理实验结果及撰写实验报告的能力。综合实验的设计目的是培养学生初步掌握小型数字系统的设计能力,包括选择设计方案,进行电路设计、安装、调试等环节,运用所学知识进行工程设计、提高实验技能的实践。数字电子钟是一种计时装置,它具有时、分、秒计时功能和显示时间功能;具有整点报时功能。 本次设计我查阅了大量的文献资料,学到了很多关于数字电路方面的知识,并且更加巩固和掌握了课堂上所学的课本知识,使自己对数字电子技术有了更进一步的认识和了解。 1、课题要求 1.1课程设计的性质与任务 本课程是电子与信息类专业的专业的专业基础必修课——“数字电路”的配套实验课程。目的在于培养学生的理论联系实际,分析和解决问题的能力。通过本课程设计,使学生在理论设计、计算机仿真、指标调测、故障排除等方面得到进一步的训练,加强学生的实践能力。学生通过设计、仿真、调试、撰写设计报告等过程,培养学生的动手能力和严谨的工作作风。 1.2课程设计的基本技术要求 1)根据课题要求,复习巩固数字电路有关专业基础知识; 2)掌握数字电路的设计方法,特别是熟悉模块化的设计思想; 3) 掌握QUARTUS-2软件的使用方法; 4) 熟练掌握EDA工具的使用,特别是原理图输入,波形仿真,能对仿真波形进行分析; 5) 具备EDA技术基础,能够熟练使用VHDL语言进行编程,掌握层次化设计方法; 6) 掌握多功能数字钟的工作原理,学会不同进制计数器及时钟控制电路的设计方法; 7) 能根据设计要求对设计电路进行仿真和测试; 8) 掌握将所设计软件下载到FPGA芯片的下载步骤等等。 9) 将硬件与软件连接起来,调试电路的功能。 1.3课程设计的功能要求 基本功能:能进行正常的时、分、秒计时功能,分别由6个数码管显示24小时,60分钟,60秒钟的计数器显示。 附加功能:1)能利用硬件部分按键实现“校时”“校分”“清零”功能; 2)能利用蜂鸣器做整点报时:当计时到达59’59’’时开始报时,鸣叫时间1秒钟; 3)定时闹铃:本设计中设置的是在七点时进行闹钟功能,鸣叫过程中,能够进行中断闹铃工作。 本人工作:负责软件的编程与波形的仿真分析。 2、方案设计与分析 NUMBER REPRESENTATION Why we study number representation ?To meet design metrics minimum number of bits that result in correct answer are required ?Additional bits will results in: ?Additional Hardware ?Increases power (Because of more switching of gates and wires) ?May increase latency Fixed point integer ?Unsigned (Non-negative integer) ?For n-bit number, range is given by [0, 2n -1] ?Ex. 111 range [0, 7] Fixed point integer ?Signed ?Sign magnitude ?For n-bit number, range is given by: ?Ex. 0 111 7 1 111 -7 ?Signed 2’s complement ?For n-bit number, range is given by: ?Ex. 1 1 1 1 [-(2n-1 –1), 2n-1 -1] Sign bit Sign bit Magnitude Magnitude [-2n-1 , 2n-1 -1] -8421 -1 Fixed point integer-Example for different types Binary number Unsigned Sign magnitude Signed 2’s complement 111115-7-1 111014-6-2 100080-8 0111777 《数字电路与FPGA》 第一部分课程性质与任务 一、课程性质与特点 《数字电路与FPGA》是高等教育自学考试、通信工程专业的一门专业基础课,是在《电路分析》、《电子线路与pspice》课程知识的基础上开设的必修课程之一,本课程的学习为通信系统底层硬件电路设计自动化打下了坚实的基础。 本课程详细论述数字逻辑电路的基本知识和基本电路的工作原理与特性,重点介绍了组合逻辑电路,时序逻辑电路与可编程逻辑器件CPLD与FPGA,结合数字电路与系统在CPLD与FPGA上的实现详细介绍了CPLD与FPGA的硬件描述语言,并上机进行实践。通过学习可以使考生对上述内容有一个完整的、系统的认识,达到熟悉并掌握数字电路与FPGA的基本理论和人工与MAX+PLVSⅡ开发软件的分析与设计方法,为后续课程的学习打好基础。本大纲是根据教育部(天津市)制定的高等教育自学考试通信工程专业培养目标编写的,立足于培养高素质人才,适应通信工程专业的培养方向,本大纲的内容尽可能简明实用,便于自学。 二、课程目标与基本要求 本课程的目标和任务是使学生通过本课程的自学和辅导考试,进行有关数字电路和FPGA 的基本理论,基本知识与基本技能的考察和训练,并了解数字电路分析与设计的现代进程,为以后的学习和工作打下坚实的基础。 课程的基本要求如下: 1、掌握数字逻辑的基础知识:对各类数制的定义,表示方法,相互间的转换,码制与常用的编码,基本逻辑与复合逻辑的定义,表示符号能熟记并能灵活应用;对逻辑代数的基本运算公式、基本定理和逻辑函数的标准表达形式能正确理解,并能熟练的应用逻辑函数的化简方法。 2、理解TTL集成门电路和CMOS集成门电路的工作原理与逻辑功能,掌握各类组合逻辑电路的人工分析与设计方法并能采用EDA方法(即应用VHDL、Verilog或AHDL硬件描述语言)进行分析与设计。 3、理解各类触发器、波形变换与产生电路的组成与工作原理。 4、掌握各类时序逻辑电路的人工分析方法,并能熟练应用EDA的分析与设计方法。 5、了解程序逻辑电路的组成和应用,掌握半导体存储器的工作原理和使用方法。 6、掌握可编程逻辑器CPLD与FPGA的基本结构特点和使用场合的选择,了解它们的编程方法并能熟练应用。 7、了解三种硬件描述语言(VHDL、Verilog HDL和AHDL)、并能掌握其中一种用于CPLD 与FPGA的设计。 8、通过上机实验学习并掌握MAX+PLOSⅡ开发软件的上机操作以及完成数字电路与系统的分析设计全过程。 三、与本专业其他课程的关系 本课程在通信工程专业的教育计划中被列为专业基础课,在电路分析(或电工基理)、信号与系统、电子成路与PSpice与通信硬件电路课程之间有承前启后的相互联系作用,对全面掌握通信工程专业各学科的知识起重要的基础作用 第二部分考核内容与考核目标 第一章数字逻辑基础 一、学习目的与要求基于FPGA的数字时钟的设计1.(精选)

数字电路设计 FPGA 讲义— number-representation

数字电路与FPGA