Cadence实验报告

电子科技大学成都学院

(微电子技术系)

实验报告书

课程名称:

学号:

姓名:

教师:

2012 年 6 月29日

实验一:制作原理图器件

实验时间:合作伙伴:

一、实验目的

1.掌握器件手册(datasheet)资料的阅读;

2.掌握通过Capture软件制作原理图器件;

3.了解原理图器件的制作步骤;

二、实验仪器设备

硬件:PC机一台;

软件:Cadence(Allegro16.2);

三、实验原理和内容

原理:根据USB2.0接口通信协议标准,通过Capture软件完成与实务器件电气特性对应的器件原理图;

内容:根据数据手册,制作USB2.0通信接口原理图器件

四、实验步骤

1.打开Capture软件界面,选择File菜单栏中的New(新建),在弹出的菜单

栏中选择Library;

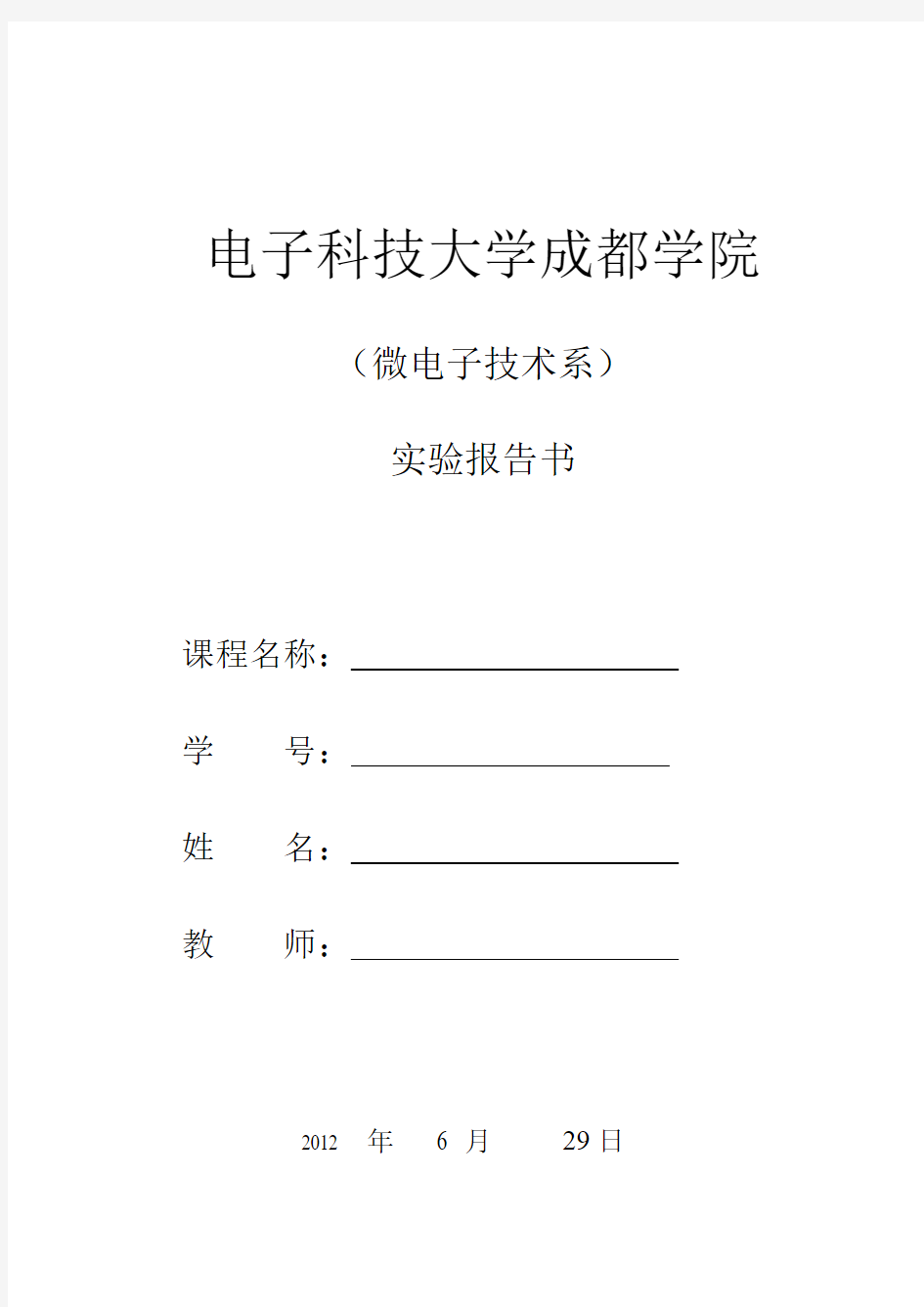

2.在弹出的窗口中,选中“library.old”,然后执行菜单命令“Design”,“New

part...”或单击鼠标右键选择“New part...”,创立新的元器件,弹出

“New Part Properties”对话框。

3.根据题目,在Name中输入元器件名称,在Part Preference Prefix中输

入元器件编号关键字母

4.绘制图形外框。

5.按照实验数据添加引脚,在Shape中选择Line

6.保存元器件。

五、实验数据

六、结果及分析

实验二电路原理图设计

实验时间:合作伙伴:

一、实验目的

1.掌握电路原理图设计方法和技巧;

2.掌握通过Capture软件设计电路原理图及相关操作;

3.掌握原理图的设计步骤;

二、实验仪器设备

硬件:PC机一台;

软件:Cadence(Allegro16.2);

三、实验原理和内容

原理:根据选用的器件手册资料,结合电路设计理论知识,完成电路原理图设计;

内容:完成基于STM32F103芯片的最小系统电路设计设计,包括:系统时钟电路;外部硬件复位电路;串口通信电路;USB接口电路;JTAG接口电

路;LED指示验证电路;BOOT电路;5V和3.3V电源电路;

四、实验步骤

1.打开Capture软件界面,选择File菜单栏中的New(新建),在弹出的菜单

栏中选择Design;

2.选择器件添加工具按钮,弹出器件选择窗口

3.选择器件添加工具按钮,打开器件选择窗口,双击添加器如需更多摆放,

继续单击鼠标完成;如不需摆放,右键单击,在弹出列表中选择end mode

4.添加外围电路

5.添加电源以及接地

6.最后完成网络标号的与器件值的添加。

五、实验数据

电阻R12为33R,R13也为33R,VCC接电源,电源值为5v 六,结果及分析

做出如图

实验三元器件封装制作

实验时间:合作伙伴:

一、实验目的

1.、掌握如何运用cadence软件制作焊盘、;

2.、掌握焊盘结构和焊盘制作、;

3.、掌握封装结构和制作封装、;

二、实验仪器设备

硬件:PC机一台;

软件:Cadence(Allegro16.2);

三、实验原理和内容

原理:根据USB2.0引脚功能和特点,通过Capture软件完成与焊盘与封装的制作;

内容:制作USB2.0的封装。(以制作瞳孔焊盘,DIP3封装为例)

四、实验步骤

1.找到并打开pad designer

2. 在parameters选项中,完成对焊盘制作单位,小数点位数,钻孔大小等的设置操作

3. 在Layer选项中,完成对各层的属性设置。如图所示

4. 将其保存在桌面为“STM32F103”

5. 在开始程序中打开PCB ediror

6.在PCB Editor 面板中点击新建,并在选项中选着封装向导

7. 在选项界面选择STM32F103封装

8. 选择毫米为单位

9. 设计引脚个数及相应长度,如图所示:

10.加入焊盘:

五、实验数据

焊盘1.3,热风焊1.8,焊盘边距1.8,孔0.8,助焊层1.5,焊盘(指针)间距0.5,指针数量为8,长度为6.7,宽(包含指针)为4.3

六、结果及分析

Dip标贴式封装,双列直插,贴片引脚数位8,引脚间距0.5大小1.3

实验四PCB设计

实验时间:合作伙伴:

一、实验目的

1.理解Layout目的及设计思路;

2.掌握Layout基本方法技巧;

3.熟悉PCB设计的一般流程;

二、实验仪器设备

硬件:PC机一台;

软件:Cadence(Allegro16.2);

三、实验原理和内容

原理:根据所要设计的PCB工程相应板子的接口通信协议标准,通过

capture软件完成与实务器件电气特性对应的器件符号图,运用

cadence软件将所要设计的PCB作出,最后产生实验图片

内容:制作PCB,完成PCB工程的制作

四、实验步骤

1.在安装好Allegro软件后,打开开始菜单,鼠标点击AllegroSPB 16.2 PCB Editor图标选项

2.打开Cadence Product Choices对话框,并选择第一个选项

3.进入PCB编辑,打开新建菜单

4.打开建立项目对话框,选择board,并命合适名

5.点击OK,进入PCB界面设置Allegro工作环境,包括设计参数、格点、子层、器件布局走线规则等。单击Setup菜单,选择Design Parameters选项,弹出Drawing Parameters Editor窗口

6.选择Design选项,完成gid的操作,完成图纸大小和设计使用单位的选择,选择Display,完成对栅格大小的操作,如下图所示:

7.选择Setup选择,在弹出的菜单中选择Cross-section选项,完成对PCB板层的设置,如下图所示:

8. 完成分层参数设置,如下图所示

9. 设置设计规则,包括物理规则设置、间距规则设置、设计约束条件和元件/网络属性设置等;

10. 选择Setup选择,在弹出的菜单中选择Constraints选项,在弹出菜单栏中选择设置项

11. 点击Physical选项,打开物理规则设置界面,如下图所示:

12.建一个规则属性。鼠标右键单击Default上,弹出菜单栏如下图所示,鼠标放到Create上,弹出选项Physical CSet;

13. 点击选项Physical CSet,弹出输入框如图所示,输入约束命名,点击选项Physical CSet,弹出输入框如图所示,输入约束命名,如图所示;

14. 物理规则建立完成后如下图所示:

图4-11 建立完成后的相关数据

15. 规则添加。在规则设置菜单栏中选择Net下的All Layers,弹出网络规则设制窗口

16. 点击DEFAULT后的箭头,在下拉列表中选择刚刚建立的规则6.5MIL。及完成对该网络的布线约束添加;

17. 间距规则设置完成后如下图所示:

18. 电气规则约束窗口:

19. 电气规则约束完成后如下图所示(图中为部分约束)

20.电气约束规则检查。在Setup下拉菜单中选择Constraints选项在弹出栏中选择Modes:

21. 电气约束规则检查窗口如下左图所示:

22. 到这儿我们完成了PCB设计环境及工程的建立,接下来就可以开始对PCB

进行Layout;

五、实验数据

六、结果及分析

实验五光绘文件制作

实验时间:合作伙伴:

一、实验目的

1.了解是光绘文件及其作用;

2.掌握文件制作方法;

二、实验仪器设备

硬件:PC机一台;

软件:Cadence(Allegro16.2);

三、实验原理和内容

原理:通过capture相应的导出原理到处Gerber(光绘文件)文件。

内容:制作光绘文件。

四、实验步骤打开

1.钻孔文件参数。打开manufacture目录下NC Parameters

注意:ameter file 设置nc_param.text文件所在位置。

Output file 不改变

Format :设置参数显示格式。

Output units 显示是英制单位m制单位。

(其余默认)

2.开NC drill

主要设置drilling选项:

Layer pair 是设计文件中都为过.

By layer:是设计文件中有盲孔等。

3:打开drill legend ,选择输出单位,剩下不改动。4:当含有不规则孔时运行NC route。

下面开始进行光绘文件生成

1,打开artwork,如图

在available films下各层生成丝印文件加入。

注意事项:

在PASTEMASK层不要加入过孔。SOLDERMASK层也不加入过孔,只是在DRILL_DRA WING中加入MANUFACTURING/NCLEGEND-1-2就可以了。

在TOP和BOTTOM层不要在undefined line width 加入默认值,默认值只在silkscreen层加入。

以下是各层需要加入的部分:

TOP

OMETRY/OUTLINE

ETCH/TOP

PIN/TOP

VIA CLASS/TOP

BOTTOM:

BOARD GEOMETRY/OUTLINE

ETCH/BOTTOM

PIN/BOTTOM

VIA CLASS/BOTTOM

DRILL_DRAWING:

MANUFACTURING/NCLEGEND-1-2

BOARD GEOMETRY/OUTLINE

OUTLINE:

BOARD GEOMETRY/OUTLINE

PASTEMASK_BOTTOM:

PIN/PASTEMASK_BOTTOM

PACKAGE GEOMETRY/PASTEMASK_BOTTOM BOARD GEOMETRY/OUTLINE

PASTEMASK_TOP:

PIN/PASTEMASK_TOP

PACKAGE GEOMETRY/PASTEMASK_TOP BOARD GEOMETRY/OUTLINE

SILKSCEEN_TOP:

MANUFACTURING/AUTOSILK_TOP

BOARD GEOMETRY/SILKSCREEN_TOP

BOARD GEOMETRY/OUTLINE

SILKSCEEN_BOTTOM:

MANUFACTURING/AUTOSILK_BOTTOM BOARD GEOMETRY/SILKSCREEN_BOTTOM BOARD GEOMETRY/OUTLINE

SOLDERMASK_TOP:

PIN/SOLDERMASK_TOP

PACKAGE GEOMETRY/SOLDERMASK_TOP BOARD GEOMETRY/OUTLINE

SOLDERMASK_BOTTOM:

PIN/SOLDERMASK_BOTTOM

PACKAGE GEOMETRY/SOLDERMASK_BOTTOM BOARD GEOMETRY/OUTLINE