CC2530定时器设置以及应用

定时器的应用

一、教学目标

1、熟悉定时器相关寄存器的功能

2、能对程序进行改写以实现不同时间的定时操作

二、教学重点

定时器T1寄存器设置

通过变量累计定时溢出调整定时时间的方法

三、教学难点

定时器以及定时中断寄存器的设置

四、教学方法

案例法、对比法

五、教学过程

[引入]定时器也是CC2530的重要资源之一,CC2530的定时器比51单片机的定时器功能更多,本次课通过阅读、修改程序以及相关寄存器的学习,使大家能基本应用定时器完成不同定时时间的程序设计。

定时器程序设计方法也分为查询法和中断法。

任务一、查询法程序设计

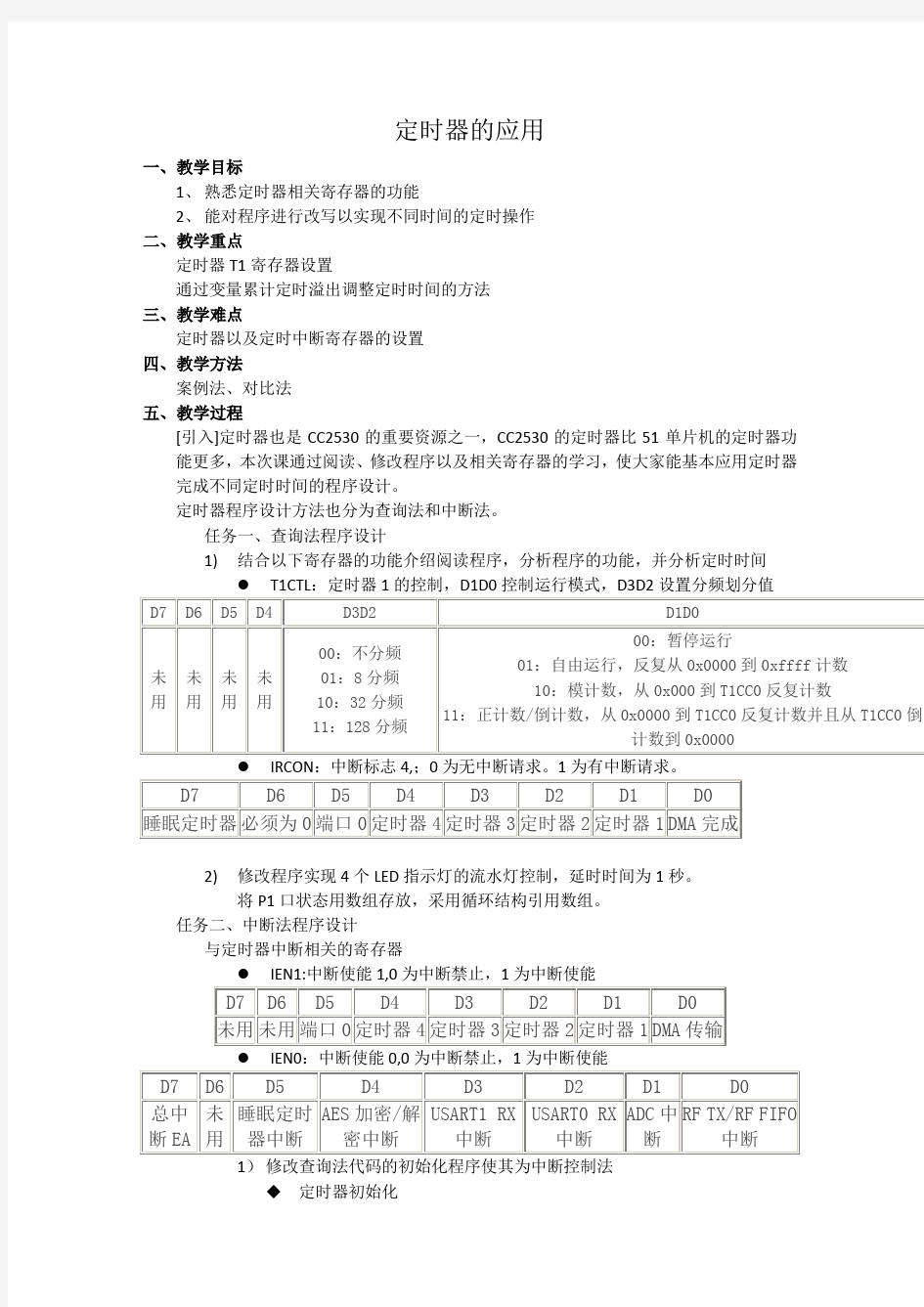

1)结合以下寄存器的功能介绍阅读程序,分析程序的功能,并分析定时时间

2)修改程序实现4个LED指示灯的流水灯控制,延时时间为1秒。

将P1口状态用数组存放,采用循环结构引用数组。

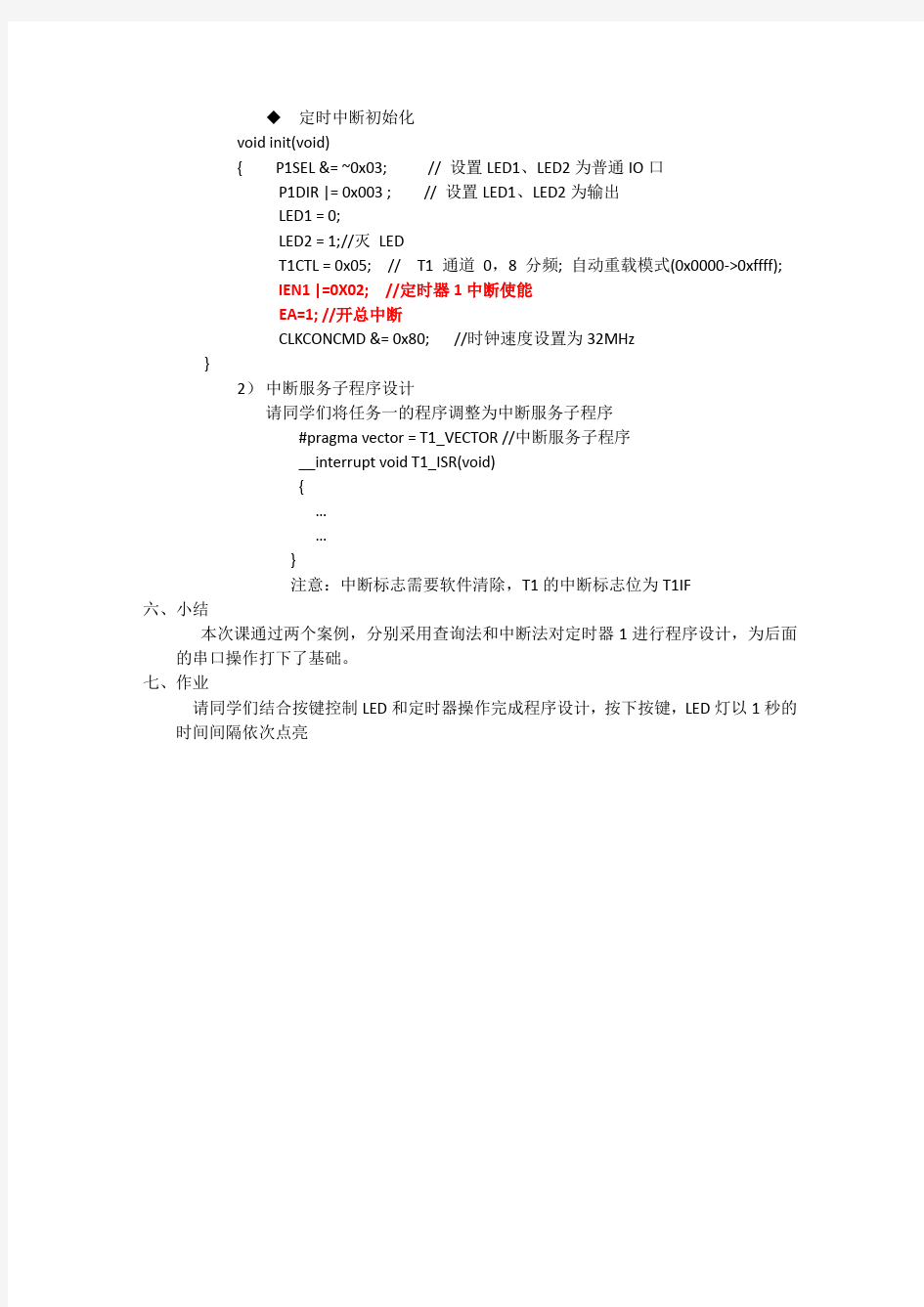

任务二、中断法程序设计

与定时器中断相关的寄存器

◆定时器初始化

定时中断初始化

void init(void)

{ P1SEL &= ~0x03; // 设置LED1、LED2为普通IO口

P1DIR |= 0x003 ; // 设置LED1、LED2为输出

LED1 = 0;

LED2 = 1; //灭LED

T1CTL = 0x05; // T1 通道0,8 分频; 自动重载模式(0x0000->0xffff);

IEN1 |=0X02; //定时器1中断使能

EA=1; //开总中断

CLKCONCMD &= 0x80; //时钟速度设置为32MHz

}

2)中断服务子程序设计

请同学们将任务一的程序调整为中断服务子程序

#pragma vector = T1_VECTOR //中断服务子程序

__interrupt void T1_ISR(void)

{

…

…

}

注意:中断标志需要软件清除,T1的中断标志位为T1IF

六、小结

本次课通过两个案例,分别采用查询法和中断法对定时器1进行程序设计,为后面的串口操作打下了基础。

七、作业

请同学们结合按键控制LED和定时器操作完成程序设计,按下按键,LED灯以1秒的时间间隔依次点亮

第十章 PWM定时器

PWM Timer 概述 S3C2410A有5个16位定时器。其中定时器0、1、2、3有脉宽调制(PWM)功能。定时器4有只有一个内部定时器而没有输出管脚。定时器0有一个死区发生器,用于大电流器件。 定时器0和1共享一个8位预定标器,定时器2、3和4共享另一个8位预定标器。每一个定时器有一个有5种不同值的时钟分割器(1/2,1/4,1/8,1/16和TCLK)。其中每一个定时器块从时钟分割器接收时钟信号,而时钟分割器从响应的预定标器接收时钟信号。8位预定标器是可编程的,它根据TCFG0和TCFG1中的数值分割PCLK。 在定时器计数缓冲寄存器(TCNTBn)中有一个初始值,当定时器使能后,这个值就被装载到递减计数器中。而在定时器比较缓冲寄存器(TCMPBn)中也有一个初始值,这一值被装载到比较寄存器中,用来与递减计数器值进行比较。这两个缓冲器使得在频率和占空比发生改变时仍能产生一个稳定的输出。 每一个定时器有一个16位的递减计数器,由定时器时钟驱动。当计数器的值到0,定时器就会产生一个中断请求来通知CPU定时器的操作已经完成。当定时器计数器到0时,TCNTn的值自动的加载到递减计数器中以继续下一操作。但是,当定时器因某种原因停止,如在定时器运行模式中清除定时器使能位(TCONn中)时,TCNTBn中的值将不再加载到计数器中。 TCMPBn中的数据是用来脉宽调制的。当递减计数器的值与比较寄存器的值相同时,定时器控制逻辑将改变输出电平。因此,比较寄存器决定一个PWM 输出的接通时间。 特性 5个16位定时器; 2个8位预定标器和2个4位分割器; 可编程的占空比; 自动再装入模式或一次脉冲模式; 死区发生器。

labview定时器模块

labview深入探索----谈谈LABVIEW的几种定时器2008-04-27 15:29 LABVIEW提供了几种定时器(包括DELAY),如下图所示 1.首先看看Tick Count 节点的帮助说明: 返回毫秒定时器的值. 基准参考时间(0 毫秒)未定义,也就是说,不能把返回的毫秒数直接转换成现实世界的时间 和日期.必须注意当你使用这个函数进行比较的时候,毫秒定时器达到2^32-1后反转成0. 基准参考时间未定义,说法比较模糊,难道会是个随机数,那显然不可能,如果是随机数,那两次调用TICK COUNT取得差值就不可能表示经过的毫秒数.无论如何,必须有个时间的起点. API函数中也有一个类似的函数:GetTickCount,该函数返回计算机启动以来经过的毫秒数.在9X中,它读取的是BIOS中保存的系统时钟的滴答数,早期PC的ROM初始化Intel8259定时器芯片来产生硬件中断08H。这个中断有时称为"定时器滴答"中断。中断08H每隔54。925毫秒产生一次,或大约每秒18.2次。BIOS使用中断08H更新存于BIOS数据区的"时间"值.这就是长说的55MS的由来.对于NT操作系统,常规的说法是能精确到 10MS,也就是说精度在1MS时是不精确的. 经过实际测试,LABVIEW的TICK COUNT的返回值和API的返回值是一致的,也就是计算机启动以来经过的毫秒数. 毫秒数达到2^32-1后反转成0,可见它的数值形式是U32,最大值是2^32-1,大概相当于49.7天.对于一个连续运行的计算机,用这个节点进行比较的时候,在连续运行49.7天后,该值自动恢复到零,如果在这个时刻进行比较,可能会出现错误的结果. 2.wait(ms)节点帮助文件中的解释是这样的.

DSP28335定时器模块儿【中英版】

5.5 32-Bit CPU Timers 0/1/2 This section describes the three 32-bit CPU timers (Figure 31) (TIMER0/1/2). CPU-Timer 0 and CPU-Timer 1 can be used in user applications. Timer 2 is reserved for DSP/BIOS. If the application is not using DSP/BIOS, then Timer 2 can be used in the application. The CPU-timer interrupt signals (TINT0, TINT1, TINT2) are connected as shown in Figure 32. [1].三个定时器0、1、2,32位 [2].0、1可随用户任意使用,2专为DSP/BIOS模式预备(当不启用DSP/BIOS模式时可以随 意定义定时器2) The general operation of the CPU timer is as follows: The 32-bit counter register TIMH:TIM is loaded with the value in the period register PRDH:PRD. The counter decrements once every (TPR[TDDRH:TDDR]+1) SYSCLKOUT cycles where TDDRH:TDDR is the timer divider. When the counter reaches 0, a timer interrupt output signal generates an interrupt pulse. The registers listed in Table 31 are used to configure the timers. [1].定时器配置流程:32位计数寄存器TIMH||TIM将PRDH||PRD中的值载入; [2].每[TDDRH||TDDR]+1个系统时钟,计数寄存器都递减一次。 [3].当计数器为0时,发起一次定时中断。

定时器电路

时分秒可校的定时器电路 设计报告 摘要 本设计的目的是设计一时分秒可校的定时器电路,该电路由数据预置部分对核心部分定时器模块进行时间预置,输出接至显示模块并

通过LED数码管显示时分秒信息,定时时间到通过声光报警模块进行报警。设计采用可编程芯片和VHDL语言进行软硬件设计,不但可使硬件大为简化,而且稳定性也有明显提高。本设计采用逐位设定预置时间,其最长时间设定可长达24小时59分59秒,并由六个共阴数码管进行时分秒的显示,定时时间到喇叭发出声响,同时两个LED灯亮。关键字: VHDL语言定时器显示报警 目录 一、系统设计 (4) 二、单元电路设计

(4) 三、软件设计 (6) 四、系统测试 (7) 五、结论 (8) 六、参考文献 (9) 七、附录 (9) 一、系统设计 1、设计要求 时分秒可校的定时器,定时范围为10秒—24时59分59秒,精度为1秒,能同时显示时分秒信息(LED数码管),定时时间到能发出声

光警告信号。 2、系统设计方案 总体框图如图所示: 图中定时模块由2个59进制、1个24进制的减计数器连接,实现定时器递减到零的倒计时功能;输出由七段数码显示译码器驱动数码管显示;报警模块由输出系列检测实现喇叭和LED 灯的时间报警;时间预置由六个输入端口分别对时分秒进行预置。 二、单元电路设计 1、倒计时部分(以秒为例):该部分是整个电路的核心,clk 为时钟信号,当时钟上升沿到来,倒计时开始,cn 为使能端,高电平有效,res 为复位端,用来清零,采用异步复位方式,s1、s2端为别为十位、个位数据预置端;count 为数据溢出端,高电平有效,dlow 、high 为四位BCD 码输出端口,用于显示及报警。 当cn 有效时,clk 脉冲上升沿到来时,开始倒计时,每60秒为一个周期,溢出端count 输出一信号使分计数减1,直到计时完成。

STM教程STMS定时器模块及其应用实例

S T M教程S T M S定时器模块及其应用实例集团标准化工作小组 [Q8QX9QT-X8QQB8Q8-NQ8QJ8-M8QMN]

第十三章 STM8S207 定时器模块及其应用实例 这一节,我们将向大家介绍如何使用 STM8 的定时器中的基本定时功能,STM8 的 定时器功能十分强大,有 TIM1 高级定时器,也有 TIM2、TIM3 等通用定时器,还有TIM4 基本定时器。在 STM8S 参考手册里面,定时器的介绍占了 1/3 的篇幅,足见其 重要性。这一节,我们分别介绍 TIM1 到 TIM4 定时器中的基本定时功能。 例程一、16 位高级控制定时器(TIM1) 简介: TIM1 由一个 16 位的自动装载计数器组成,它由一个可编程的预分频器驱动。 TIM1 有 4 个通道,分别是 1 到 4。分别对应于四个不同的捕获/比较通道。 高级控制定时器适用于许多不同的用途: 基本的定时 测量输入信号的脉冲宽度(输入捕获) 产生输出波形(输出比较,PWM 和单脉冲模式) 对应与不同事件(捕获,比较,溢出,刹车,触发)的中断 与 TIM5/TIM6 或者外部信号(外部时钟,复位信号,触发和使能信号)同步 高级控制定时器广泛的适用于各种控制应用中,包括那些需要中间对齐模式 PWM 的应用,该模式支持互补输出和死区时间控制。 高级控制定时器的时钟源可以是内部时钟,也可以是外部的信号,可以通过配置寄存器来进行选择。 这一节我们实现的功能是基本的定时,关于 PWM 的编程留下以后的章节中。还有建议大家研究更为深入的功能 TIM1 的时基单元包括,如下图所示: ● 16 位向上/向下计数器 ● 16 位自动重载寄存器 ●重复计数器 ●预分频器 16 位计数器,预分频器,自动重载寄存器和重复计数器寄存器都可以通过软件 进行读写操作。 自动重载寄存器由预装载寄存器和影子寄存器组成。 可在在两种模式下写自动重载寄存器: ●自动预装载已使能(TIM1_CR1 寄存器的 ARPE 位置位)。在此模式下,写入 自动重载寄存器的数据将被保存在预装载寄存器中,并在下一个更新事件(UEV)时传送 到影子寄存器。 ●自动预装载已禁止(TIM1_CR1 寄存器的 ARPE 位清除)。在此模式下,写入自动重载寄存器的数据将立即写入影子寄存器。 更新事件的产生条件: ●计数器向上或向下溢出。 ●软件置位了 TIM1_EGR 寄存器的 UG 位。 ●时钟/触发控制器产生了触发事件。 在预装载使能时(ARPE=1),如果发生了更新事件,预装载寄存器中的数值(TIM1_ARR)将写入影子寄存器中,并且 TIM1_PSCR 寄存器中的值将写入预分频器中。 置位 TIM1_CR1 寄存器的 UDIS 位将禁止更新事件(UEV)。

stm32通用定时器详解

stm32通用定时器 STM32的定时器是个强大的模块,定时器使用的频率也是很高的,定时器可以做一些基本的定时,还可以做PWM输出或者输入捕获功能。 时钟源问题: 名为TIMx的有八个,其中TIM1和TIM8挂在APB2总线上,而TIM2-TIM7则挂在 APB1总线上。其中TIM1&TIM8称为高级控制定时器(advanced control timer).他们所在的APB2总线也比APB1总线要好。APB2可以工作在72MHz下,而APB1最大是36MHz。 定时器的时钟不是直接来自APB1或APB2,而是来自于输入为APB1或APB2的一个倍频器。 下面以定时器2~7的时钟说明这个倍频器的作用:当APB1的预分频系数为1时,这个倍频器不起作用,定时器的时钟频率等于APB1的频率;当APB1的预分频系数为其它数值(即预分频系数为2、4、8或16)时,这个倍频器起作用,定时器的时钟频率等于APB1的频率两倍。 假定AHB=36MHz,因为APB1允许的最大频率为36MHz,所以APB1的预分频系数可以取任意数值;当预分频系数=1时,APB1=36MHz,TIM2~7的时钟频率=36MHz(倍频器不起作用);当预分频系数=2时,APB1=18MHz,在倍频器的作用下,TIM2~7的时钟频率=36MHz。有人会问,既然需要TIM2~7的时钟频率=36MHz,为什么不直接取APB1的预分频系数=1?答案是:APB1不但要为TIM2~7提供时钟,而且还要为其它外设提供时钟;设置这个倍频器可以在保证其它外设使用较低时钟频率时,TIM2~7仍能得到较高的时钟频率。 再举个例子:当AHB=72MHz时,APB1的预分频系数必须大于2,因为APB1的最大频率只能为36MHz。如果APB1的预分频系数=2,则因为这个倍频器,TIM2~7仍然能够得到72MHz的时钟频率。能够使用更高的时钟频率,无疑提高了定时器的分辨率,这也正是设计这个倍频器的初衷。

第6章 定时器相关模块

第6章定时器相关模块 本章导读:本章讲述了计数器/定时器的一般工作原理,介绍K60N512的定时接口模块(PDB、 FTM、PIT、LPTMR、CMT和RTC )的基本功能与编程基础,并给出具体的例子,读者要仔细体会各种不同的使用方法,并将这些方法运用到具体的应用中。本章知识点有①计数器/定时器的工作原理;②可编程延时模块PDB;③Flex定时器FTM;④周期中断定时器PIT; ⑤低功耗定时器LPTMR;⑥载波调制传输接口 CMT;⑦实时时钟RTC。 6.1计数器/定时器的基本工作原理 在嵌入式应用系统中,有时要求能对外部脉冲信号或开关信号进行计数,这可通过计数器来完成。有些设备要求每间隔一定时间开启并在一段时间后关闭,有些指示灯要求不断地闪烁,这可利用定时信号来完成。个人计算机也经常要用到定时信号,如系统日历时钟的计时、产生不同频率的声源等。在计算机系统屮,计数与定时问题的解决方法是一致的,只不过是同一个问题的两种表现形式。 实现计数与定时的基本方法有三种:完全硬件方式、完全软件方式、可编程计数器/定时器。 1.完全硬件方式 在过去的许多仪器仪表或设备中,需要进行延时、定时或计数,经常使用数字逻辑电路实现, 即完全用硬件电路实现计数/定时功能,若要改变计数/定时的要求,必须改变电路参数,通用性和灵活性差。在微型电子计算机出现以后,特別是随着单片微型计算机的发展与普及,这种完全硬件方式实现定时与计数的方法已较少使用。 2.完全软件方式 在计算机中,通过编程利用计算机执行指令的时间实现定时,称为完全软件方式,简称软件方式。在这种方式中,一般是根据所需要的时间常数来设计一个延时子程序,延时子程序中包含一定的指令,设计者要对这些指令的执行时间进行精确的计算和测试,以便确定延时时间是否符合要求。当时间常数比较大时,常常将延时子程序设计为一个循环程序,通过循环常数和循环体内的指令来确定延时时间。这样,每当延时子程序结束以后,可以直接转入下而的操作,也可以用输出指令产生一个信号作为定时输出。这种方法的优点是节省硬件。主要缺点是执行延时程序期间,CPU一直被占用,所以降低了CPU的使用效率,也不容易提供多作业环境;另外,设计延时子程序时,要用指令执行时间来拼凑延时时间,显得比较麻烦。不过,这种方法在实际应用中还是经常使用的,尤其是在已有系统上作软件开发时,以及延时时间较小而重复次数又较少的情况。在计算机控制软件开发过程中,作为粗略的延时,经常使用软件方法来实现定时。 3.可编程计数器/定时器 利用专门的可编程计数器/定时器实现计数与定时,克服了完全硬件方式与完全软件方式的缺点,综合利用了它们各自的优点,其计数/定时功能可由程序灵活地设置,设定之后与CPU 并行地工作,不占用CPU的工作时间。应用可编程计数器/定时器,在简单的软件控制下,可以产生准确的时间延时。这种方法的主要思想是根据需要的定时时间,用指令对计数器/定时器设置定时常数,并用指令启动计数器/定时器开始计数,当计数到指定值时,便自动产生一个定时输出。在计数器/定时器开始工作以后,CPU不必去管它,而可以去做其他工作。这种方法最突出的优点是计数时不占用CPU的时间,如果利用计数器/定时器产生中断

定时器捕获.

-------------------------- MSP430的定时器中有比较捕获的概念,刚刚接触非常生疏。看了半天终于清楚:比较模式: 这是定时器的默认模式,当在比较模式下的时候,与捕获模式相关的硬件停止工作,如果这个时候开启定时器中断,然后设置定时器终值(将终值写入TACCRx),开启定时器,当TAR的值增到TACCRx的时候,中断标志位CCIFGx置一,同时产生中断。若中断允许未开启则只将中断标志位CCIFGx置一。 例子:比较模式就像51单片机一样,要能够软件设置定时间隔来产生中断处理一些事情,如键盘扫描,也可以结合信号输出产生时序脉冲发生器,PWM信号发生器。如:不断装载TACCRx,启动定时器,TAR和TACCRx比较产生中断处理。捕获模式: 利用外部信号的上升沿、下降沿或上升下降沿触发来测量外部或内部事件,也可以由软件停止。捕获源可以由CCISx选择CCIxA,CCIxB,GND,VCC。完成捕获后相应的捕获标志位CCIFGx置一 捕获模式的应用: 利用捕获源的来触发捕获TAR的值,并将每次捕获的值都保存到TACCRx 中,可以随时读取TACCRx的值,TACCRx是个16位的寄存器,捕获模式用于事件的精确定位。如测量时间、频率、速度等 例子:利用两次捕获的值来测量脉冲的宽度。或捕获选择任意沿, CCISx=”11“(输入选择VCC),这样即当VCC与GND发生切换时产生捕获条件 结合利用:异步通讯

同时应用比较模式和捕获模式来实现UART异步通信。即利用定时器的比较模式来模拟通讯时序的波特率来发送数据,同时采用捕获模式来接收数据,并及时转换比较模式来选定调整通信的接受波特率,达到几首一个字节的目的 ---------------------------------------- 利用MSP430单片机定时器A和捕获/比较功能模块结合使用,实现脉冲宽度的测量。 本例程用到了定时器A的CCI1A端口(例如MSP430F14X的P1.2引脚)作捕获外部输入的脉冲电平跳变,同时结合简单的软件算法就能实现脉冲宽度的测量。在实际应用中可根据例程中的start,end,overflow三个变量来计算脉冲宽度。此功能模块在实际产品应用中体现出有较高的应用价值。 2-例程 #include

定时器模块控制小灯周期性的闪烁

定时器模块控制小灯周期性的闪烁 //红色字体是本次主要添加或者修改的内容 //本程序主要是演示计数器的基本功能 //用键盘产生脉冲信号,接到TPM1的计数器引脚 //每按键一次,计数器加1,把计数器的结果TPM1CNT显示在数码管上 //-------------------------------------------------------------------------* // 工程名: KeyCtrlLight * // 硬件连接: 见工程说明* // 程序描述: 用开关通过芯片控制小灯闪烁* // 目的: 第一个Freescale AW系列MCU C语言程序框架* // 说明: 提供Freescale MCU的编程框架,供教学入门使用* //----------------苏州大学飞思卡尔嵌入式系统实验室2010年-------------------* #include "Includes.h" const uint8 Dtable[10]={0x3F,0x06,0x5B,0x4F,0x66,0x6D,0x7D,0x07,0x7F,0x6F }; uint16 soc01; void Delay_n_ms(uint16 n) { uint16 i,j; for(i=0;i<n;i++) { for(j=0;j<950;j++); } } void SMG_show(uint16 n) { uint8 b1,b10,b100,b1000; b1=n%10; b10=(n/10)%10; b100=(n/100)%10; b1000=(n/1000)%10; BSET(5,PTDD); PTBD=Dtable[b1]; Delay_n_ms(2);

定时器模块介绍

1、简述 MC9S12XS128定时器模块与MC9S12DG128 ECT部分功能完全类似,以下均以ECT模块介绍xs128定时器模块。 HC12 增强型捕捉计时器模块在HCS12标准定时器的基础上增加了一些特点,用以扩展它的应用范围,特别是在汽车ABS 方面。 基准计时器的核心仍然是一个16 位的可编程计数器,其时钟源来自一个预分频器。该计时器可以被应用于多个方面,包括在对输入波形进行测量的同时产生一个输出波形。波形的脉宽可以在几微秒到数秒的范围内变化。 增强型定时器模块(ECT)的结构框图如下,ECT功能相当于高速的I/O口,由一个4位预分频器、一个16位自由运行计数器,8个16位IC/OC通道,2个16位脉冲累加器以及一个16位模数递减计数器组成。

ECT实际上是一个16位的可编程计数器,它的基本时钟频率可以通过预分频器设置,用于产生波形输出,测量输入波形,统计脉冲个数,可以作为定时中断功能和独立时钟基准。 2、运行模式 停止:由于时钟停止,计时器和计数器均关闭。 冻结:计时器和计数器均保持运行,直到T SCR($06)的T SFRZ 位被置1。 等待:计数器保持运行,直到T SCR($06)的T SWAI 位被置1。

正常:计时器和计数器均保持运行, 直到T SCR($06)的T EN 位和M CCTL($26)的MCEN 位被分别清0。 IC 通道组 IC 通道组由四个标准的缓冲通道IC0-IC3 和四个非缓冲通道IC4-IC7 组成,两部分的基本功能都是捕捉外部事件发生的时刻,但是缓冲通道除了IC /OC 寄存器TCn 外,还设有保持寄存器TCnH,此外还在入口设置了延迟计数器,用来提高抗干扰能力。非缓冲通道没有保持寄存器,入口也没有延迟计数器,但每个通道入口设置了一个 2 输入端的多路器,事件触发信号可以是来自本通道的输入引脚PORTn,也可以是来自其关联通道PORT(n-4)的延迟计数器输出,使用更加灵活。当延迟功能有效时,输入引脚检测到一个有效的边沿后,延迟计数器开始对P 时钟(模块时钟)进行计数,当到达设定的计数值后,延迟计数器在其输出端有条件地产生一个脉冲,这个条件就是延迟前后的引脚电平相反。这样可以避免对窄输入脉冲做出反应。延迟计数结束后,计数器自动清除。输入信号两个有效边沿之间的持续时间必须大于设定的延迟时间。 在ECT 中,所有IC 通道均设置了覆盖保护功能,可以通过寄存器ICOVW 设置是否允许某个通道用新的捕捉结果覆盖上一个结果。 对于缓冲的IC 通道PT0-PT3,还具有锁存与队列两种工作方式。在锁存方式下,每个有效的引脚事件只将自由定时器的值放入捕捉寄存器TCn,而TCn 到保持寄存器TCnH 的传送必须依赖递减模数计数器回0 或者其他强制锁存命令才能实现,这时IC 的工作情形与第 6 章的TIM 模块相似。在队列方式下(图7-2),TCn 与TCnH 形成了一个类似先进先出的队列,每个捕捉结果从TCn 进入,然后随着下一个捕捉结果的到来移入TCnH,程序可以从TCnH 取得结果,然而这个队列是开放的,即程序也可以直接从TCn 取得捕捉结果。队列方式为CPU 提供了充分的响应时间。 由于PAC0-3 与IC0-3 共享相同的引脚,而且共享入口的逻辑,因此在两种方式下,PAI 与IC 都可以同时工作,对同一引脚进行记录,前者记录脉冲或者边沿的数量,后者记录具体的时刻。 模数递减计数器 16 位递减模数计数器(MDC)可以用作时钟基准,产生周期性的中断请求,也可用于将IC 寄存器和脉冲累加器的值锁存到各自的保持寄存器中。锁存动作可以通过程序设定为周期性的或一次性的。MDC 的时钟频率可通过独立的定标器设定,内部设有定时常数寄存器,可以实现自动重装载,但MDC 的常数寄存器与MDC 计数器使用相同的地址,加载时通过特殊的时序实现。 每当MDC 回0 时,将在给定的时间段内控制贮和PAI 寄存器的内容向各自的缓冲寄存器传输。反映了MDC 在IC、PAI 系统中的作用。 脉冲累加器