贵州大学实验报告模板

课程名称:

学院:专业:

姓名:学号:

年级:任课教师:

年月日

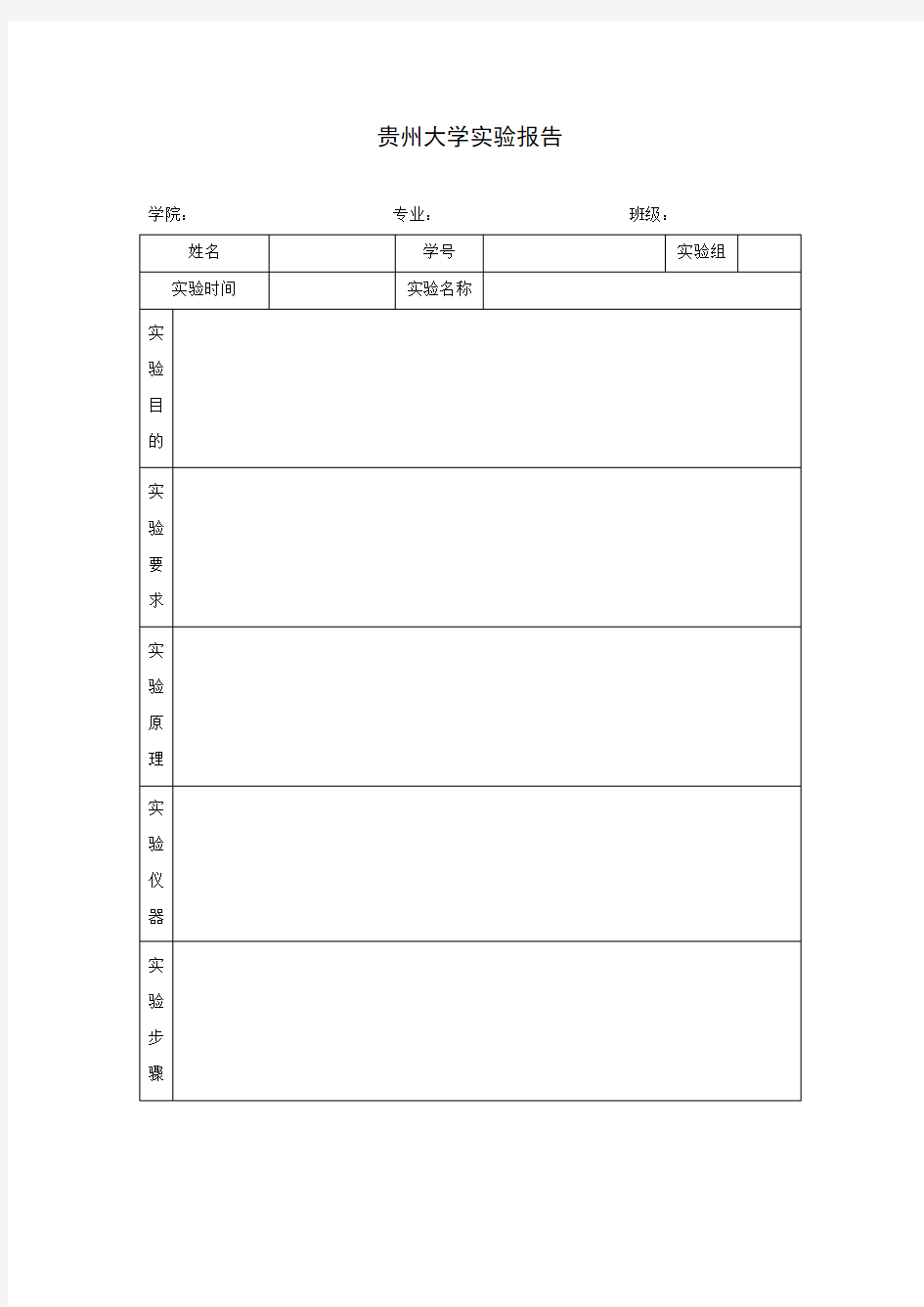

贵州大学实验报告

学院:专业:班级:姓名学号实验组实验时间实验名称

实

验

目

的

实

验

要

求

实

验

原

理

实

验

仪

器

实

验

步

骤

实

验

内

容

实

验

数

据

实

验

总

结

注:各实验可根据教学需要对以上栏目进行增减。表格内容可根据内容扩充。

贵州大学本科毕业的论文范本

本科毕业论文(设计)论文(设计)题目: 学院:________ 专业:________ 班级:________ 学号:________ 学生姓名:________ 指导教师:________ 年月日

贵州大学本科毕业论文(设计) 贵州大学本科毕业论文(设计) 诚信责任书 本人郑重声明:本人所呈交的毕业论文(设计),是在导师的指导下独立进行研究所完成。毕业论文(设计)中凡引用他人已经发表或未发表的成果、数据、观点等,均已明确注明出处。 特此声明。 论文(设计)作者签名: 日期:

目录 摘要 .................................................................................................................................... I II Abstract ..................................................................................................................................... I V 第一章前言(小四黑体) (1) 1.1 控制系统..................(小四宋体). (1) 1.1.1 控制系统..................(小四宋体) .. (1) 1.1.2 控制系统 ...................................................................... 错误!未定义书签。第二章自反对法. (2) 2.1 自适应系统的概念 (2) 2.1.1 自适应系统的应用 (2) 第三章控制系统在数控 (3) 3.1 自适应系统的概念 (3) 3.1.1 自适应系统的应用 (3) 第四章自适应控制系统在数控 (4) 4.1 在日常生活中 (4) 第五章控制系统的应用 (5) 5.1 在日常生活中 (5) 第六章控制系统数控 (6) 6.1 风风火火机 (6) 第七章自适应控制系统在数控 (7) 7.1 公司飞过海后 (7) 第八章自适应控制系统在数控 (8) 8.1 善卷洞科技 (8) 第九章自适应控制系统在数控 (9) 9.1 反对咖啡碱棵 (9) 第十章自适应控制系统在数控 (10) 10.1 第三等级 (10)

北京邮电大学数电实验一实验报告

北京邮电大学数字电路与逻辑 设计实验 学院: 班级: 作者: 学号:

实验一 Quartus II原理图输入法设计 一、实验目的: (1)熟悉Quartus II原理图输入法进行电路设计和仿真 (2)掌握Quartus II 图形模块单元的生成与调 (3)熟悉实验板的使用 二、实验所用器材: (1)计算机 (2)直流稳压电源 (3)数字系统与逻辑设计实验开发板 三、实验任务要求 (1)用逻辑门设计实现一个半加器,仿真验证其功能,并生成新的半加器图形模 块单元。 (2)用(1)中生成的半加器模块和逻辑门设计实现一个全加器,仿真验证其功能, 并下载到实验板测试,要求用拨码开关设定输入信号,发光二极管显示输出信号。 (3)用3线-8线译码器(74LS138)和逻辑门设计实现函数 ,仿真验证其功能,并下载到实验板测试。要求用拨码开关设定输入信号,发光二极管显示输出信号。 四、设计思路和过程 (1)半加器的设计 半加器电路是指对两个输入数据位进行加法,输出一个结果位和进位,不产生进位输入的加法器电路。是实现两个一位二进制数的加法运算电路。数据输入AI被加数、BI加数,数据输出SO和数(半加和)、进位C0。 在数字电路设计中,最基本的方法是不管半加器是一个什么样的电路,按组合数字电路的分析方法和步骤进行。 1.列出真值表 半加器的真值表见下表。表中两个输入是加数A0和B0,输出有一个是和S0,另一个是进位C0。

2 该电路有两个输出端,属于多输出组合数字电路,电路的逻辑表达式如下函数的逻辑表达式为:SO=AI⊕BI CO=AB 所以,可以用一个两输入异或门和一个两输入与门实现。

贵州大学毕业设计论文格式

第四章毕业论文(设计说明书)的撰写 4.1 基本要求 1.毕业论文(设计说明书),必须由学生本人独立完成,不得弄虚作假,不得抄袭他人成果。 2.毕业论文(设计说明书)应中心突出,容充实,论据充分,论证有力,数据可靠,结构紧凑,层次分明,图表清晰,格式规,文字流畅,字迹工整,结论正确。 3.毕业论文(设计)篇幅要求:工学类毕业论文(设计)字数不少于1.5万字;农学类毕业论文(设计)字数不少于1.0万字;理学类毕业论文(设计)字数不少于0.8万字;经济管理类毕业论文(设计)字数不少于0.6万字;语言文学类毕业论文(设计)字数不少于0.5万字;艺术类毕业论文(设计)字数不少于0.4万字。设计类专业题目应附设计图纸、计算机程序、设计说明书等;研究类专题应附实验原始记录及报告、数据处理及相关模型、计算机程序或调研报告、读书笔记等支撑材料。阅读中外文献资料,理工农类不得少于10篇,其他专业不少于15篇,文献综述不少于0.3万字。 4.毕业论文(设计)符合统一规定的格式。 4.2 容要求 4.2.1 毕业论文的容要求 1.题目:应简洁、明确、有概括性,字数不宜超过20个字。 2.摘要:要有高度的概括力,语言精练、明确。扼要叙述论文的主要容、方法、成果和结论。摘要中不宜使用公式、图表,不标注引用文献编号。同时要有中、英文对照摘要,中文摘要约300~500汉字;英文摘要相对应汉字。 3.关键词:从论文标题或正文中挑选3~5个最能表达主要容的词作为关键词,同时有中、英文对照,分别附于中、英文摘要后。

4.目录:写出目录,标明页码。 5.正文:包括前言、本论、结论三个部分。 (1)前言(引言):是论文的开头部分,主要说明论文写作的目的、现实意义、对所研究问题的认识,并提出论文的中心论点等。前言要写得简明扼要,篇幅不要太长。 (2)本论:是毕业论文的主体,包括实验材料、研究容与方法、实验结果与分析(讨论)等。在本部分要运用各方面的实验结果和研究方法,分析问题,论证观点,尽量反映出自己的科研能力和学术水平。 (3)结论:是毕业论文的收尾部分,是围绕本论所作的结束语。其基本的要点就是总结全文,加深题意。 6.参考文献:在毕业论文末尾要列出在论文中参考过的专著、论文及其他资料(按学科类别分别为10或15篇以上),所列参考文献应按论文参考或引证的先后顺序排列。 7.致:简述自己通过毕业论文的体会,并应对指导教师和协助完成论文的有关人员表示意。 8.注释:在论文写作过程中,有些问题需要在正文之外加以阐述和说明。 9.附录:对于一些不宜放在正文中,但有参考价值的容,可编入附录中。例如,公式的推演、编写的算法、语言程序等。 4.2.2 毕业设计说明书的容要求 1.题目:要求简洁、确切、鲜明,字数不宜超过20个字。 2.摘要:扼要叙述本设计的主要容、特点,文字要精练。中文摘要约300汉字;英文摘要对应汉字。 3.关键词:从说明书标题或正文中挑选3~5个最能表达主要容的词作为关键词,同时有中、英文对照,分别附于中、英文摘要后。 4.目录:写出目录,标明页码。 5.正文:包括前言、本论、结论三个部分。 (1)前言:说明本设计的目的、意义、围及应达到的技术要求;简述本课题在国外的发展概况及存在的问题;本设计的指导思想;阐述本设计应解决的主

数电实验报告一

姓名:谭国榕班级:12电子卓越学号:201241301132 实验一逻辑门电路的研究 一、任务 1.熟悉实验室环境及实验仪器、设备的使用方法。 2.掌握识别常用数字集成电路的型号、管脚排列等能力。 3.熟悉74 LS系列、CMOS 4000B系列芯片的典型参数、输入输出特性。 4.掌握常规数字集成电路的测试方法。 二、实验设备及芯片 双踪示波器(DF4321C)1台 信号发生器(DF1641B1)1台 数字万用表(UT58B)一台 数电实验箱1个(自制) 芯片2个:74LS04 CD4069 。 三、实验内容 1.查阅芯片的PDF文件资料,分清管脚名与逻辑功能的对应关系及对应的真值表。74LS04:

CD4069: 2.静态测试 验证6非门74LS04、4069逻辑功能是否正常,并用数字万用表测量空载输出的逻辑电平值(含高、低电平)。 结论:由表格可以看出,CD4069输出的高电平比74LS04高,输出的低电平比74LS04低,所以CD4069的噪声容限相对于74LS04来说较大,故其抗干扰能力强。 3.动态测试 测逻辑门的传输延迟时间:将74LS04、4069中的6个非门分别串接起来,将函数发生器的输出调为方波,对称,幅度:0-5V,单极性,加至第一个门的输入端,并用示波器的通道1观察;用示波器的通道2观察最后一个非门的输出信号,对比输入输出波形以及信号延迟时间。

调节方波信号:

74LS04输出延迟特性: CD4069输出延迟特性:

输出延迟时间的实验数据表: 结论:74LS04的输出延迟比CD4069的输出延迟要短,说明前者的工作速度比后者快。 4.观察电压传输特性 用函数发生器的输出单极性的三角波,幅度控制在5伏,用示波器的X-Y 方式测量TTL 、 CMOS 逻辑门的传输特性,记录波形并对TTL 、CMOS 两种类型电路的高电平输出电压、低电平输出电压以及噪声容限等作相应比较。 (1) 调节函数发生器的输出:单极性三角波,对称,幅度:5V ,频率:500Hz ,从函数发生 器的下部50Ω输出端输出信号; 如图: (2) 扫描方式改为X-Y ,CH1、CH2 接地,调光标使其处于左下角附近; (3) CH1 用 2.0V/DIV (DC ),接函数发生器输出(即非门的输入);CH2 用 0.2V/DIV (DC ),接非门输出。 (4) 记录示波器波形(如图)。

2018年贵州大学本科论文格式模板

本科毕业论文(设计) 论文(设计)题目:基于人工智能的快论文排版系统研究 学院:信息学院 专业:计算机 班级:计算机131 学号:20135091612 学生姓名:快论文 指导教师:***教授 2017年6月8日

贵州大学本科毕业论文(设计) 诚信责任书 本人郑重声明:本人所呈交的毕业论文(设计),是在导师的指导下独立进行研究所完成。毕业论文(设计)中凡引用他人已经发表或未发表的成果、数据、观点等,均已明确注明出处。 特此声明。 论文(设计)作者签名: 日期:

贵州大学毕业论文第I页 基于人工智能的快论文排版系统研究 摘要 快论文(https://www.360docs.net/doc/2114281346.html,)是一款专业的毕业论文在线排版系统,上传论文草稿,选定学校模板,点击一键排版,只需几分钟就可完成论文排版,免费下载预览,满意后付款。快论文平台现已汇集了全国617所高校权威毕业论文模板,均源自各校官方最新发布的毕业论文撰写规范,基本涵盖了各类高校毕业论文格式要求。 据统计,毕业论文排版涉及的几十项格式设置中,80%的操作都属于不常用操作,因此绝大多数同学以前没用过,以后用到的概率也很低,但为了达到排版的规范,却需要花费大量的时间去解读论文撰写规范和学习这些不常用的word操作。面对复杂的格式规范,大多数同学熬夜反复调整修改却还是存在各种各样的问题。 基于人工智能的快论文排版系统,剔除了人们手动排版时不可避免的误操作,和由于视觉疲劳导致的错漏等,较之传统的人工排版方式,质量更可靠,价格更优惠,速度更快捷。快论文平台秉持人性化的设计理念,在充分研究分析人们的操作习惯的基础上,针对应届毕业的大学生,充分考虑其个性需求,设计并开发完成了一个界面简洁、功能强大、操作便捷的毕业论文排版和编辑系统,帮助大学生提高毕业论文写作效率和提升毕业论文质量。 快论文根据各个高校官方的论文写作规范要求,分别构建了属于各高校自己的定制模板,更准确,更便捷,是国内最大的毕业论文排版平台。 关键词:快论文;专业排版;质量可靠;价格优惠;值得信赖 I

数字电路实验报告

数字电路实验报告 姓名:张珂 班级:10级8班 学号:2010302540224

实验一:组合逻辑电路分析一.实验用集成电路引脚图 1.74LS00集成电路 2.74LS20集成电路 二、实验内容 1、组合逻辑电路分析 逻辑原理图如下:

U1A 74LS00N U2B 74LS00N U3C 74LS00N X1 2.5 V J1 Key = Space J2 Key = Space J3 Key = Space J4 Key = Space VCC 5V GND 图1.1组合逻辑电路分析 电路图说明:ABCD 按逻辑开关“1”表示高电平,“0”表示低电平; 逻辑指示灯:灯亮表示“1”,灯不亮表示“0”。 真值表如下: A B C D Y 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1 表1.1 组合逻辑电路分析真值表 实验分析: 由实验逻辑电路图可知:输出X1=AB CD =AB+CD ,同样,由真值表也能推出此方程,说明此逻辑电路具有与或功能。 2、密码锁问题: 密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开;否则,报警信号为“1”,则接通警铃。

试分析下图中密码锁的密码ABCD 是什么? 密码锁逻辑原理图如下: U1A 74LS00N U2B 74LS00N U3C 74LS00N U4D 74LS00N U5D 74LS00N U6A 74LS00N U7A 74LS00N U8A 74LS20D GND VCC 5V J1 Key = Space J2 Key = Space J3 Key = Space J4 Key = Space VCC 5V X1 2.5 V X2 2.5 V 图 2 密码锁电路分析 实验真值表记录如下: 实验真值表 A B C D X1 X2 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 0 1 1 0 0 0 0 1 1 0 0 1 1 0 1 0 1 0 0 1 1 0 1 1 0 1 1 1 0 0 0 1 1 1 0 1 0 1 1 1 1 0 0 1 1 1 1 1 0 1 表1.2 密码锁电路分析真值表 实验分析: 由真值表(表1.2)可知:当ABCD 为1001时,灯X1亮,灯X2灭;其他情况下,灯X1灭,灯X2亮。由此可见,该密码锁的密码ABCD 为1001.因而,可以得到:X1=ABCD ,X2=1X 。

贵州大学计算机网络实验报告-实验二-TCPIP 协议常用网络工具的使用

实验课程名称计算机网络实验报告 实验项目名称TCP/IP 协议常用网络工具的使用专业班级电子信息科学与技术08级1班学生姓名 学号 指导教师 理学院 实验时间:2010年4月22日

实验名称: 实验二TCP/IP协议常用网络工具的使用 实验目的: ●了解系统网络命令及其所代表的含义,以及所能对网络进行的操作。 ●通过网络命令了解运行系统网络状态,并利用网络命令对网络进行简单的操作。 实验器材: 连接到因特网的计算机,个人电脑Windows XP sp3系统。 实验内容(步骤): 学习使用windows环境下常用的网络命令: 1)Ipconfig:IP地址与以太网卡硬件地址查看命令 2)Ping:网络连接测试命令 3)ARP:地址解析命令 4)FTP:文件传输命令 5)Netstat:显示协议及其端口信息和当前的TCP/IP 网络连接 6)Route:控制网络路由表 7)TFTP:简单文件传输命令 8)Tracert:该诊断实用程序将包含不同生存时间(TTL) 值的Internet 控制消息 协议(ICMP) 回显数据包发送到目标,以决定到达目标采用的路由。 9)Net:网络服务等 1. ipconfig Ipconfig命令应该是最最基础的命令了,主要功能就是显示用户所在主机内部的 IP协议的配置信息等资料。 它的主要参数有: all:显示与TCP/IP协议相关的所有细节信息,其中包括测试的主机名、IP地址、 子网掩码、节点类型、是否启用IP路由、网卡的物理地址、默认网关等。 renew all:更新全部适配器的通信配置情况,所有测试重新开始。 release all:释放全部适配器的通信配置情况。 renew n:更新第n号适配器的通信配置情况,所有测试重新开始。 命令格式是: C:\>ipconfig/(参数)

贵州大学毕业论文模板【贵州大学毕业论文的致谢词】

贵州大学毕业论文模板【贵州大学毕业论文的致谢词】 写完论文时,我正在美丽的江城,此时已是阳春三月,东湖的杨柳已经吐芽,磨山上的桃花已是绚烂绽放,光谷的荷兰风情园风景旖旎,这一切的一切,正昭示着春天已经来临。 一个人在深夜静静地坐在书桌前,突然恍然惊醒,已是白驹过隙,弹指一挥间,三年之韶光已逝,蓦然回首,以前的我从未想过会有一天来到美丽的贵州来求学,记得第一次坐火车从荆楚大地南下至黔时,我看到了以前从未见过的巍峨大山,这里的山是一望无际的,怎么也看不到尽头,当时的我,对前途有着一股浓浓的忧虑之感,故而触景生情,在随身携带的笔记本上,顺手写下:“古夜郎,南下荆楚旅,坐看满城连绵山.巍巍黔灵,黑云疑是卷帘雨,暗袭蹙眉描青黛,多少愁绪,拟作婉蜒崎岖。”但不曾想过,不爱出远门的我,在三年的时光里,踏遍了大半个贵州的山山水水,有瀑声如雷的黄果树,有宁静幽远的青岩古镇,有赤色之城的遵义,有风俗古城屯堡,有平静如面的红枫湖,有秀美玲珑的黔灵山,每处都留下了我的脚印,这里的山是美的,这里的水亦是美的,这里是一片神奇而充满万种风情的地方。 在贵州大学的三年时光里,给我感触颇多,尤其是当要结束毕业论文的写作而行将搁笔之时,仿佛无穷的字意涌现在笔头,汩汩而流,我本是一个生性懒怠之人,有时候在路上走一段路都觉得步履很是沉重,写完论文,正是预示着离开贵州大学的钟声已经敲响,这钟声敲响昭示着今天的结束与明天的到来。 吾师谭先生,每次遇到我,则问的最多的则是关于论文问题,而我亦每每有惶恐不安之感,书到用时方恨少,自己胸中的疏淡之黑迹在先生眼里如同曝日下的水珠,随之化为白汽,何来谈之学术? 感谢谭先生对我的不离不弃,感谢王晓卫老师、梅桐生老师、黄海老师、胡晓军老师对我的悉心教诲,感谢同窗之友谊对我的莫大支持,亦感谢家人对我的顽劣的包容。 离开贵州大学,我即将有一个新的开始,曾看过当代作家周涛写的一篇文章《山河判断——大西北札记》,里面有一句对我感触良深,“沙漠对河流说:结束!河流回答:我本身就是开始。” 感谢您的阅读!

数电实验报告

选课时间段: 序号(座位号): 杭州电子科技大学 实验报告 课程名称: 数字原理与系统设计实验 实验名称: 组合电路时序分析与自动化设计 指导教师: 学生姓名 学生学号 学生班级 所学专业 实验日期

实验一、设计8位串行进位加法器电路设计: 一位全加器: 八位串行进位加法器:

仿真波形:

实验二、设计5人表决电路 代码: module BJDL45(A,B,C,D,E,YES,NO); input A,B,C,D,E; output YES,NO; reg YES,NO; always@ (A,B,C,D,E,YES,NO) case ({A,B,C,D,E}) 5'B00000:{YES,NO}<=2'B01; 5'B00001:{YES,NO}<=2'B01; 5'B00010:{YES,NO}<=2'B01; 5'B00011:{YES,NO}<=2'B01; 5'B00100:{YES,NO}<=2'B01; 5'B00101:{YES,NO}<=2'B01; 5'B00110:{YES,NO}<=2'B01; 5'B00111:{YES,NO}<=2'B10; 5'B01000:{YES,NO}<=2'B01; 5'B01001:{YES,NO}<=2'B01; 5'B01010:{YES,NO}<=2'B01; 5'B01011:{YES,NO}<=2'B10; 5'B01100:{YES,NO}<=2'B01; 5'B01101:{YES,NO}<=2'B10; 5'B01110:{YES,NO}<=2'B10; 5'B01111:{YES,NO}<=2'B10; 5'B10000:{YES,NO}<=2'B01; 5'B10001:{YES,NO}<=2'B01; 5'B10010:{YES,NO}<=2'B01; 5'B10011:{YES,NO}<=2'B10; 5'B10100:{YES,NO}<=2'B01; 5'B10101:{YES,NO}<=2'B10; 5'B10110:{YES,NO}<=2'B10; 5'B10111:{YES,NO}<=2'B10; 5'B11000:{YES,NO}<=2'B01; 5'B11001:{YES,NO}<=2'B10; 5'B11010:{YES,NO}<=2'B10; 5'B11011:{YES,NO}<=2'B10; 5'B11100:{YES,NO}<=2'B10; 5'B11101:{YES,NO}<=2'B10; 5'B11110:{YES,NO}<=2'B10; 5'B11111:{YES,NO}<=2'B10; default: {YES,NO}<=2'B10; endcase

(整理)数字图像处理实验指导书 _贵州大学

计算机科学与信息学院 《数字图像处理》 实验指导书 适用专业:信息安全、网络工程、计算机 贵州大学 二O一三年五月

前言 本指导书是根据数字图像处理教学大纲和实验大纲编写的,在教学过程中指导学生实验时使用。运用MATLAB软件平台,结合图像处理工具箱,对图像处理相关算法进行编程和实现。通过学生上机操作实践与教师指导,使学生深入理解和掌握数字图像处理的技术和方法,增强处理实际问题的能力。 考虑到《数字图像处理》课程的自身特点,以及软件的升级更新性,本实验指导书具有适应性。 本实验指导书主要适用于计算机科学与信息学院的各个相关专业。

目录 实验一图像基本操作 (4) 实验二图像增强 (7) 实验三图像分割 (11) 实验四汽车牌照自动识别 (16) 实验报告的基本内容及要求 (18) 贵州大学实验报告 (19)

实验一图像基本操作 实验学时:2 实验类型:验证 实验要求:必做 一、实验目的 利用MATLAB软件,熟悉图像的数据矩阵操作、图像的类型转换及图像的存储等基本操作。 1.熟悉图像矩阵的基本操作 2.掌握图像数据类型转换及图像类型转换 3.掌握图像文件的读写 4.掌握图像及灰度图像直方图的显示 5.掌握图像缩放和旋转 二、实验原理和方法 1.关于图像矩阵 MATLAB中图像数据以矩阵方式的存储。所以有必要学会关于矩阵的操作,由于篇幅有限,这里只作简要的介绍。 生成矩阵的函数有: eye 生成单位矩阵 ones全1阵 zeros 全零阵 rand 均匀随机阵 randn 正态随机阵 2.图像数据类型及图像类型 2.1 图像数据类型转换 MATLAB中图像数据矩阵的存储方式为双精度(double)类型即64位浮点数。而存储图像时MATLAB有时采用无符号整型(uint8)即图像矩阵中的每个数据占用一个字节。由于大多数运算和函数(比如最基本的矩阵加减运算)都不支持uint8类型,所以运算时通常要将图像转换成 double型。 函数double将数据转换为双精度浮点类型,调用格式为: X64=double(x8) /256 2.2 图像类型及转换 在MATLAB中,一幅图像可能包含一个数据矩阵,也可能有一个颜色映像表矩阵。MATLAB图像处理工具箱支持四种图像类型,其区别在于数据矩阵元素的不同含意。它们是:● 真彩色图像 ● 索引图像 ● 灰度图像 ● 二值图像 (1)真彩色图像 真彩色图像又称RGB图像,对于一个尺寸为M×N的彩色图像来说,在MATLAB中则存储为一个M×N×3的多维数组,像素的颜色由保存在像素位置上的R、G、B的强度值的组合来确定。如果需要知道图像A中(x,y)处的像素值,则可以使用这样的代码A(x,y,1:3)。 (2)索引图像

数电仿真实验报告

数字电子技术仿真 实验报告 班级: 姓名: 学号:

实验一组合逻辑电路设计与分析 一、实验目的 1.掌握组合逻辑电路的特点; 2.利用逻辑转换仪对组合逻辑电路进行分析与设计。 二、实验原理 组合逻辑电路是一种重要的、也是基本的数字逻辑电路,其特点是:任意时刻电路的输出仅取决于同一时刻输入信号的取值组合。 对于给定的逻辑电路图,我们可以先由此推导出逻辑表达式,化简后,由所得最简表达式列出真值表,在此基础上分析确定电路的功能,这也即是逻辑电路的分析过程。 对于组合逻辑电路的设计,一般遵循下面原则,由所给题目抽象出便于分析设计的问题,通过这些问题,分析推导出真值表,由此归纳出其逻辑表达式,再对其化简变换,最终得到所需逻辑图,完成了组合逻辑电路的设计过程。 逻辑转换仪是在Multisim软件中常用的数字逻辑电路设计和分析的仪器,使用方便、简洁。 三、实验电路及步骤 1.利用逻辑转换仪对已知逻辑电路进行分析。 (1)按图1-1连接电路。 图1-1 待分析的逻辑电路 (2)通过逻辑转换仪,得到下图1-2所示结果。 由图可看到,所得表达式为:输出为Y, D'+ABCD CD'+ABC' AB' + D C' BCD'+AB' A' + D BC' A'+ CD B' D'+A' C' B' A' Y

图1-5 经分析得到的真值表和表达式 (3)分析电路。观察真值表,我们发现:当输入变量A、B、C、D中1的个数为奇数时,输出为0;当其为偶数时,输出为1。因此,我们说,这是一个四输入的奇偶校验电路。 2.根据要求,利用逻辑转换仪进行逻辑电路的设计。 问题提出:有一火灾报警系统,设有烟感、温感和紫外线三种类型不同的火灾推测器。为了防止误报警,只有当其中有两种或两种以上的探测器发出火灾探测信号时,报警系统才会产生报警控制信号,试设计报警控制信号的电路。 具体步骤如下: (1)分析问题:探测器发出的火灾探测信号有两种情况,一是有火灾报警(可用“1”表示),一是没有火灾报警(可用“0”来表示),当有两种或两种以上报警器发出报警时,我们定义此时确有警报情况(用“1”表示),其余以“0”表示。由此,借助于逻辑转换仪面板,我们绘出如图1-3所示真值表。 图1-3 经分析得到的真值表

贵州大学C++实验报告2

贵州大学实验报告 学院:大数据信息与工程专业:通信班级: 122

2. 声明Boat和cat两个类,两者都有weight属性,定义二者的一个友元函数totalweight(),计算二者的重量和。 #include

this->weight=weight; } Cat::~Cat() { } int weight1(Cat&c) { int sss; sss=c.weight; return sss; } class Boat { public: Boat( int weight); ~Boat(); friend int weight1(Boat&); private: int weight; }; Boat::Boat(int weight) { cout<<"这个Boat的weight为:"< 实验一门电路逻辑功能及测试 一、实验目的 1、熟悉门电路逻辑功能。 2、熟悉数字电路学习机及示波器使用方法。 二、实验仪器及材料 1、双踪示波器 2、器件 74LS00 二输入端四与非门 2片 74LS20 四输入端双与非门 1片 74LS86 二输入端四异或门 1片 74LS04 六反相器 1片 三、预习要求 1、复习门电路工作原理相应逻辑表达示。 2、熟悉所有集成电路的引线位置及各引线用途。 3、了解双踪示波器使用方法。 四、实验内容 实验前按学习机使用说明先检查学习机是否正常,然后选择实验用的集成电路,按自己设计的实验接线图接好连线,特别注意Vcc及地线不能接错。线接好后经实验指导教师检查无误方可通电。试验中改动接线须先断开电源,接好线后在通电实验。 1、测试门电路逻辑功能。 (1)选用双输入与非门74LS20一只,插入面包板,按图 连接电路,输入端接S1~S4(电平开关输入插口),输 出端接电平显示发光二极管(D1~D8任意一个)。 (2)将电平开关按表1.1置位,分别测出电压及逻辑状态。(表1.1) 2、异或门逻辑功能测试 (1)选二输入四异或门电路74LS86,按图接线,输入端1﹑2﹑4﹑5接电平开关,输出端A﹑B﹑Y接电平显示发光二极管。 (2)将电平开关按表1.2置位,将结果填入表中。 表 1.2 3、逻辑电路的逻辑关系 (1)选用四二输入与非门74LS00一只,插入面包板,实验电路自拟。将输入输出逻辑关系分别填入表1.3﹑表1.4。 (2)写出上面两个电路的逻辑表达式。 表1.3 Y=A ⊕B 表1.4 Y=A ⊕B Z=AB 4、逻辑门传输延迟时间的测量 用六反相器(非门)按图1.5接线,输80KHz 连续脉冲,用双踪示波器测输入,输出相位差,计算每个门的平均传输延迟时间的tpd 值 : tp d=0.2μs/6=1/30μs 5、利用与非门控制输出。 选用四二输入与非门74LS00一只,插入面包板,输入接任一电平开关,用示波器观察S 对输出脉冲的控制作用: 一端接高有效的脉冲信号,另一端接控制信号。只有控制信号端为高电平时,脉冲信号才能通过。这就是与非门对脉冲的控制作用。 6.用与非门组成其他门电路并测试验证 (1)组成或非门。 用一片二输入端与非门组成或非门 Y = A + B = A ? B 画出电路图,测试并填表1.5 中。 表1.5 图如下: (2)组成异或门 ① 将异或门表达式转化为与非门表达式。 A ⊕B={[(AA)'B]'[A(BB)']}' ② 画出逻辑电路图。 ③ 测试并填表1.6。 表1.6 输入 输出 A B Y 0 1 0 1 0 1 0 0 1 1 A B Y 0 0 0 0 1 1 1 0 1 1 1 [键入文档标题] 实验一组合逻辑电路分析 一.试验用集成电路引脚图 74LS00集成电路74LS20集成电路 四2输入与非门双4输入与非门 二.实验内容 1.实验一 2.实验二 密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开。否则,报警信号为“1”,则接通警铃。试分析密码锁的密码ABCD是什么? ABCD接逻辑电平开关。 最简表达式为:X1=AB’C’D 密码为:1001 A B C D X1 X2 A B C D X1 X2 0 0 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 1 1 0 0 1 1 0 0 0 1 0 0 1 1 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 0 1 0 1 0 0 0 1 1 1 0 0 0 1 0 1 0 1 0 1 1 1 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 1 0 1 1 1 0 1 1 1 1 1 0 1 三.实验体会: 1.分析组合逻辑电路时,可以通过逻辑表达式,电路图和真值表之间的相互转换来到达实验所要求的目的。 2.这次试验比较简单,熟悉了一些简单的组合逻辑电路和芯片,和使用仿真软件来设计和构造逻辑电路来求解。 实验二组合逻辑实验(一)半加器和全加器 一.实验目的 1.熟悉用门电路设计组合电路的原理和方法步骤 二.预习内容 1.复习用门电路设计组合逻辑电路的原理和方法步骤。 2.复习二进制数的运算。 3.用“与非门”设计半加器的逻辑图。 4.完成用“异或门”、“与或非”门、“与非”门设计全加器的逻辑图。 5.完成用“异或”门设计的3变量判奇电路的原理图。 三.元件参考 依次为74LS283、 74LS00、74LS51、 74LS136 其中74LS51:Y= (AB+CD)’, 74LS136: Y=A⊕B(OC门)四.实验内容 1.用与非门组成半加器,用或非门、与或非门、与非门组成全加器(电路自拟) 半加器 被加数A i0 1 0 1 0 1 0 1 加数B i0 0 1 1 0 0 1 1 前级进位C i-10 0 0 0 1 1 1 1 和S i0 1 1 0 1 0 0 1 数电实验报告(含实验内容) 班级:专业:姓名:学号:实验一用与非门构成逻辑电路 一、实验目的 1、熟练掌握逻辑电路的连接并学会逻辑电路的分析方法 2、熟练掌握逻辑门电路间的功能变换和测试电路的逻辑功能 二、实验设备及器材 KHD-2 实验台 集成 4 输入2 与非门74LS20 集成 2 输入4 与非门74LS00 或CC4011 三、实验原理 本实验用的逻辑图如图 2-1 所示 图1-1 图1-1 四、实验内容及步骤 1、用与非门实现图1-1电路,测试其逻辑功能,将结果填入表1-1中,并说明该电路的逻辑功能。 2、用与非门实现图1-1电路,测试其逻辑功能,将结果填入表1-2中,并说明该电路的逻辑功能。 3、用与非门实现以下逻辑函数式,测试其逻辑功能, 将结果填入表1-3中。 Y(A,B,C)=A’B+B’C+AC 班级:专业:姓名:学号:五、实验预习要求 1、进一步熟悉 74LS00、74LS20 和CC4011 的管脚引线 2、分析图 1-1 (a)、的逻辑功能,写出逻辑函数表达式,并作出真值表。 六、实验报告 1、将实验数据整理后填入相关的表格中 2、分别说明各逻辑电路图所实现的逻辑功能 A B C Z A B C Y 表1-1 表1-2 A B C Y 表1-3 班级:专业:姓名:学号:实验二组合逻辑电路的设计与测试 一、实验目的 1、掌握组合逻辑电路的设计与测试方法 2、进一步熟悉常用集成门电路的逻辑功能及使用 二、实验设备及器材 KHD-2 实验台 4 输入2 与非门74LS20 2 输入4 与非门74LS00 或CC4011 三、实验原理 使用中、小规模集成电路来设计组合电路是最常见的逻辑电路的设计方式。设计组合电路的一般步骤如图2-1 所示。 图 2-1 组合逻辑电路设计流程图 根据设计任务的要求建立输入、输出变量,并列出真值表。然后用逻辑代数或卡诺图化简法求出简化的逻辑表达式。并按实际选用逻辑门的类型修改逻辑表达式。根据简化后的逻辑表达,画出逻辑图,用标准器件构成逻辑电路。最后,用实验来验证设计的正确性。 四、实验内容及步骤 1、用与非门设计一个数码转换电路,将一个三位二进制码转换成3 位格雷码。即当输入信号为三位二进制代码时其输出为相应的3 位格雷码。要求: 1)分析逻辑功能,作出真值表,写出逻辑表达式。 班级:专业:姓名:学号: 2)简化逻辑表达式,画出逻辑图 3)按逻辑图连接逻辑电路并测试其逻辑功能。 2、用与非门设计一个一位的数值比较器,即比较两个1 位的二进制数A、B 的大小,假定当A>B 时,1 号灯亮,AB 时,1 号灯亮,A 数字电路实验报告 实验一 组合逻辑电路分析 一.试验用集成电路引脚图 74LS00集成电路74LS20集成电路 四2输入与非门双4输入与非门 二.实验内容 1.实验一 X1 2.5 V A B C D U1A 74LS00N U2A U3A 74LS00N 逻辑指示灯:灯亮表示“1”,灯灭表示“0” ABCD按逻辑开关,“1”表示高电平,“0”表示低电平 自拟表格并记录: A B C D Y A B C D Y 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 1 0 0 1 0 0 0 1 0 0 1 0 1 0 0 0 0 1 1 1 1 0 1 1 1 0 1 0 0 0 1 1 0 0 1 0 1 0 1 0 1 1 0 1 1 0 1 1 0 0 1 1 1 0 1 0 1 1 1 1 1 1 1 1 1 2.实验二 密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时, 开锁信号为“1”,将锁打开。否则,报警信号为“1”,则接通警铃。试分析密码锁的密码ABCD是什么? A B C D ABCD接逻辑电平开关。 最简表达式为:X1=AB’C’D 密码为:1001 三.实验体会: 1.分析组合逻辑电路时,可以通过逻辑表达式,电路图和真值表之间的相互转换来到达实验所要求的目的。 2.这次试验比较简单,熟悉了一些简单的组合逻辑电路和芯片,和使用仿真软件来设计和构造逻辑电路来求解。 实验二组合逻辑实验(一)半加器和全加器 一.实验目的 1.熟悉用门电路设计组合电路的原理和方法步骤 二.预习内容 1.复习用门电路设计组合逻辑电路的原理和方法步骤。 2.复习二进制数的运算。 3.用“与非门”设计半加器的逻辑图。 4.完成用“异或门”、“与或非”门、“与非”门设计全加器的逻辑图。 5.完成用“异或”门设计的3变量判奇电路的原理图。 贵州大学实验报告 (1)建立学生课程库操作,在SQL Server企业管理器中实现。库中表结构为: 学生(学号,姓名,年龄,性别,所在系); 课程(课程号,课程名,先行课); 选课(学号,课程号,成绩) 要求:1)建库、建表和建立表间联系。 2)选择合适的数据类型。 3)定义必要的索引、列级约束和表级约束。 (2)将自设计的数据库、库中的表、索引和约束用SQL语句表达,并通过企业管理器或查询分析器实现建库、建表、建立表间联系和建立必要的索引、列级约束和表级约束的操作。 实验步骤一、基本操作实验 (1)、打开Sqlserver 2008,新建查询; (2)、在新建的空白窗口输入如下的代码先建数据库名称: 然后在”对象资源管理器”中点击“刷新”按钮可看到如下所示界面,表示数据库新建成功 (3)然后新建“图书”数据库,输入如下代码: 然后执行代码,显示: 表示“图书”数据表成功建立;(4)、新建“读者”数据库,输入如下代码: 然后执行代码,显示: 表示“读者”数据表成功建立;(5)、新建“借阅”数据库,输入如下代码: 然后执行代码,显示: 表示“借阅”数据表成功建立(6)、最后的关系如下所示: 2、提高操作实验 (1)、打开Sqlserver 2008,新建查询; (2)、在新建的空白窗口输入如下的代码先建数据库名称: 然后在”对象资源管理器”中点击“刷新”按钮可看到如下所示界面,表示数据库新建成功 (3)、新建“学生”数据库,输入如下代码: 然后执行代码,显示: 表示“学生”数据表成功建立 (4)、新建“课程”数据库,输入如下代码: 然后执行代码,显示: 表示“课程”数据表成功建立(5)、新建“选课”数据库,输入如下代码: 然后执行代码,显示: 表示“选课”数据表成功建立;(6)、最后的关系如下所示: 河 北 科 技 大 学 实 验 报 告 级 专业 班 学号 年 月 日 姓 名 同组人 指导教师 张敏 实验名称 实验二 基本门电路逻辑功能的测试 成 绩 实验类型 验证型 批阅教师 一、实验目的 (1)掌握常用门电路的逻辑功能,熟悉其外形及引脚排列图。 (2)熟悉三态门的逻辑功能及用途。 (3)掌握TTL 、CMOS 电路逻辑功能的测试方法。 二、实验仪器与元器件 (1)直流稳压电源 1台 (2)集成电路 74LS00 四2输入与非门 1片 74LS86 四2输入异或门 1片 74S64 4-2-3-2输入与或非门 1片 74LS125 四总线缓冲门(TS ) 1片 CD4011 四2输入与非门 1片 三、实验内容及步骤 1.常用集成门电路逻辑功能的测试 在数字实验板上找到双列直插式集成芯片74LS00和74LS86。按图进行连线。测试各电路的逻辑功能,并将输出结果记入表中。 门电路测试结果 2.测试与或非门74S64的逻辑功能 在实验板上找到芯片74S64,实现Y AB CD =+的逻辑功能。 Y Y & 3.用与非门组成其他逻辑门电路 (1)用与非门组成与门电路 按图接线,按表测试电路的逻辑功能。根据测得的真值表,写出输出Y的逻辑表达式。 真值表 逻辑表达式: (2)用与非门组成异或门电路 按图接线,将测量结果记入表中,并写出输出Y 的逻辑表达式。 真值表 逻辑表达式: 真值表 4.三态门测试 (1)三态门逻辑功能测试 三态门选用 74LS125将测试结果记入表中。 (2)按图接线。将测试结果记录表中。 真值表 4–46 实验名称门电路逻辑功能及其应用 1、实验目的 1.熟悉数字电子技术实验箱。 2.掌握常用的逻辑门电路的逻辑功能和测试方法 3.掌握集电极开路门的逻辑功能及使用特点。 2、实验原理 1.基本逻辑功能 (1)与门的功能 特点:全1出1;只要有一-个为0,输出为0。 (2)或门的功能 特点:全0出0;只要有一-个为1,输出为1。 (3)与非门门的功能 特点:全1出0; 只要有一-个为0,输出为1。 (4)异或门门]的功能 特点:相异为1;相同为0。 2.集电极开路门(0C门) 线与的功能 集电极开路门(简称0C门),它工作时必须外接负载电阻RL。若把两个0C门输出端连接在一-起,通过公共电阻RL接到电源,就可实现“线与”的功能。 3、实验步骤 1、测试门电路的逻辑功能 (1)将四2输入与非门74LS00 一只插入数字电子实验箱,按图2.1.1接线,输入端接S1、S2 (逻辑电平开关输出插口),输出端接直流电压表或电平显示发光二极管。 (2)将电平开关按表要求输入电平,分别测输出电压及逻辑状态,验证输出与输入变量是否符合“与非”关系。 2.测试门电路传输特性 (1)按图2.1.4接线。 (2)调Rp,用电压表测量当U分别为0.3、0.6、1、1.3、1.4、1.5、2、3V时对应的U值,填入表中,并画出传输特性曲线。 3.利用与非门控制 用与非门按图接线,S接任一电平开关,用示波器观察S对 输出脉冲的控制作用。用坐标纸画出观测图输入与输出的对 应波形。 4.0C门的“线与”功能测试 按图接线,A、B、C、D分别接至逻辑开关S1、S2、S3、S4的插孔中,按照逻辑图,有L=ABCD。把A、B、C、D的16种组合列出真值表,再用实验测定L,并填表。数电实验报告

数电实验实验报告

数电实验报告(含实验内容)

数电实验实验报告

贵州大学实验报告1之令狐文艳创作

数电实验报告(2013年开始新)

数字电子技术实验报告1