JTAG接口介绍

JTAG(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP(Test Access Port,测试访问口),通过专用的JTAG测试工具对内部节点进行测试。

目前大多数比较复杂的器件都支持JTAG协议,如ARM、DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。

JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。JTAG接口还常用于实现ISP(In-System Programmable在系统编程)功能,如对FLASH器件进行编程等。

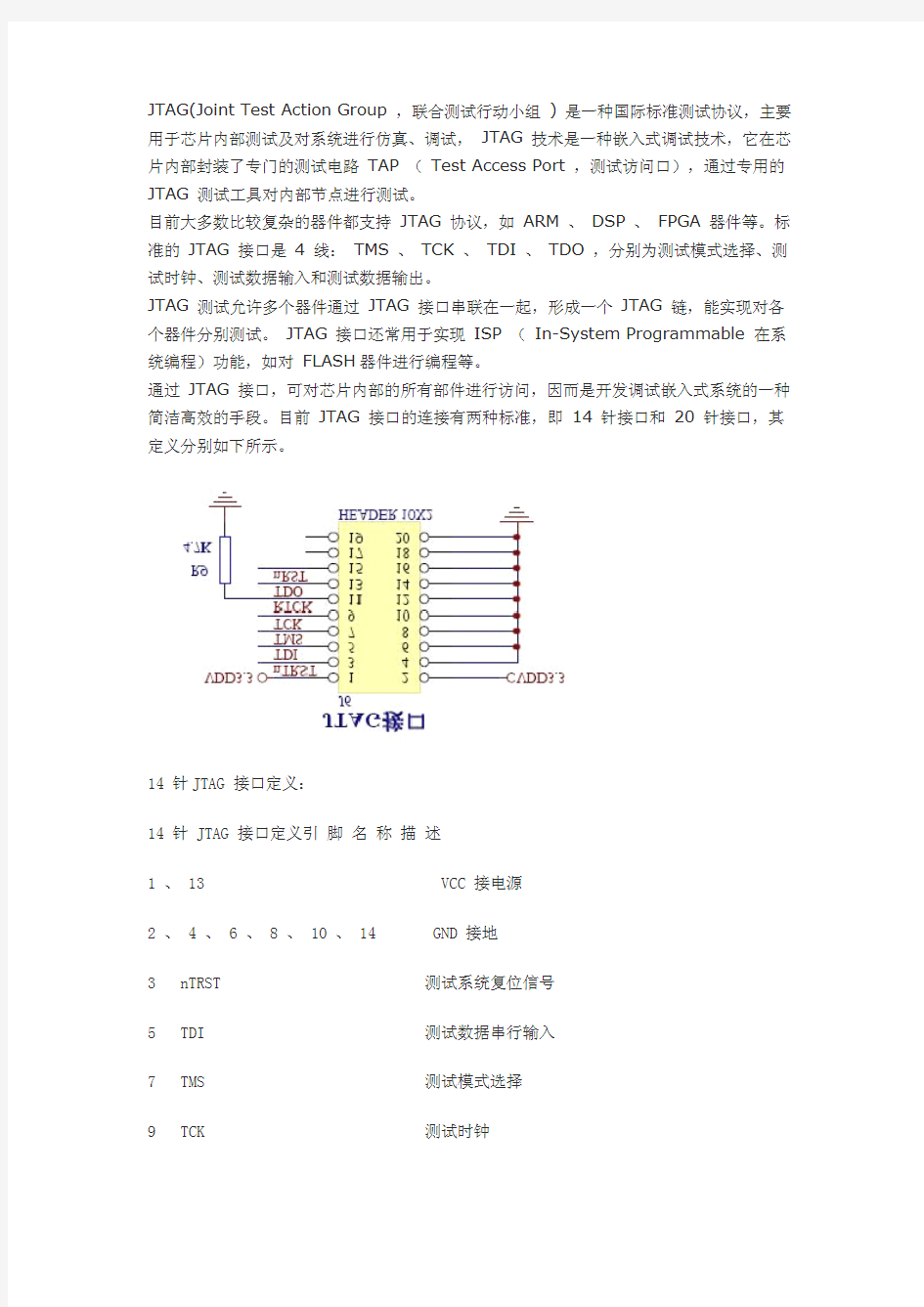

通过JTAG接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。目前JTAG接口的连接有两种标准,即14针接口和20针接口,其定义分别如下所示。

14针JTAG接口定义:

14针JTAG接口定义引脚名称描述

1、13VCC接电源

2、4、6、8、10、14GND接地

3nTRST测试系统复位信号

5TDI测试数据串行输入

7TMS测试模式选择

9TCK测试时钟

11TDO测试数据串行输出

12NC未连接

20针JTAG接口定义引脚名称描述

1VTref目标板参考电压,接电源

2VCC接电源

3nTRST测试系统复位信号

4、6、8、10、12、14、16、18、20GND接地

5TDI测试数据串行输入

7TMS测试模式选择

9TCK测试时钟

11RTCK测试时钟返回信号

13TDO测试数据串行输出

15nRESET目标系统复位信号

17、19NC未连接

下面以S3C4510B开发板为例说明JTAG接口:

在保证电源电路、晶振电路和复位电路正常工作的前提下,可通过JTAG接口调试S3C4510B,在系统上电前,首先应检测JTAG接口的TMS、TCK、TDI、TDO信号是否已与S3C4510B 的对应引脚相连,其次应检测S3C4510B的nEWAIT引脚(Pin71)是否已上拉,ExtMREQ 引脚(Pin108)是否已下拉,对这两只引脚的处理应注意,作者遇到多起S3C4510B不能正常工作或无法与JTAG接口通信,均与没有正确处理这两只引脚有关。

给系统上电后,可通过示波器查看S3C4510B对应引脚的输出波形,判断是否已正常工作,若S3C4510B已正常工作,在使能片内PLL电路的情况下,SDCLK/MCLKO引脚(Pin77)应输出频率为50MHz的波形,同时,MDC引脚(Pin50)和其他一些引脚也应有波形输出。

在保证S3C4510B已正常工作的情况下,可使用ADS或SDT通过JTAG接口对片内的部件进行访问和控制。

在此,首先通过对片内控制通用I/O口的特殊功能寄存器的操作,来点亮连接在P3~P0口上的4只LED,用以验证ADS或SDT调试环境是否已正确设置,以及与JTAG接口的连接是否正常。

ADS和SDT均为ARM公司为方便用户在ARM芯片上进行应用开发而推出的一整套集成开发工具,其中,ADS为SDT的升级版本。该系统的调试以ADS为例,同时也适合于SDT开发环境。

连接好硬件后,打开AXD Debugger,建立与目标板(待调试的系统板)的连接,AXDDebugger 有软件仿真方式和带目标系统的调试方式,此时应工作在带目标系统的调试方式。

选择菜单System Views→Command Line Interface功能,该选项为AXD Debugger的一个命令行窗口,可在该窗口内输入各种调试命令,使用非常方便。在命令行窗口输入:

>setmem0x3FF5000,0xFFFF,32

>setmem0x3FF5008,0xFFFF,32

setmem命令用于对特定的地址设置特定的值,待设定的值可以是8位、16位或32位,在此,对通用I/O口的模式寄存器和数据寄存器设置相应的值,点亮LED。

S3C4510B在复位后,特殊功能寄存器的基地址为0x3FF0000,由表5-2-3可知,I/O口的模式寄存器偏移地址为0x5000,因此,I/O口的模式寄存器的物理地址为0x3FF5000,设定该寄存器的值为0xFFFF,将I/O口置为输出方式。I/O口的数据寄存器的物理地址为0x3FF5008,设定该寄存器的值为0xFFFF,将I/O口的输出置为高电平。

在执行完以上两条命令后,连接在通用I/O口的4只LED应被点亮,表示调试系统的软、硬件连接完好,可进行下一步的调试工作,否则,应重新检查调试系统。

用户若使用SDT作为调试工具,操作方法类似。连接好硬件后,打开ARM Debugger for Windows,建立与目标板(待调试的系统板)的连接,选择菜单View→Command功能,即可显示命令行窗口,在命令行窗口输入:

Debug:let0x3FF5000=0xFFFF

Debug:let0x3FF5008=0xFFFF

执行完以上两条命令后,连接在通用I/O口的4只LED应被点亮。

关于通用I/O口更具体的工作原理和使用方法,可参考S3C4510B用户手册。

用户系统若能正常完成上述操作并成功点亮连接在P3~P0口上的LED显示器,则表明

S3C4510B已在正常工作,且调试环境也已正确建立,以后的调试工作就相对简单。笔者曾遇到多个用户系统因为不能完成这步工作,使开发者失去信心而最终放弃。

很多工程师在对按键去抖动都会采用软件延时的方法,今天介绍下关于Piccolo DSP GPIO所具有的硬件去抖功能.

信号首先同步于系统时钟,在输入到内核改变之前要经过一定周期个数的量化,这种方式可以滤除噪声。量化窗口输入的结构示意图如图所示。

由图可知,外部的管脚输入信号经过一个量化窗口到达DSP内核。量化窗口的时间宽度取决于采样间隔和采样个数。采样间隔由GPxCTRL寄存器决定,采样个数由寄存器GPxQSELn决定。

如果QUxLPRDn=0,采样间隔为一个系统周期整数倍。如果QUxLPRDn=N(N≠0),

采样周期为系统周期的2N倍。如表所示

采样个数可以配置位三个或六个。通过寄存器GPAQSEL1、GPAQSEL2、GPBQSEL1来配置,当外部管脚电平状态发生变化时,量化窗口检测到三个或六个周期内相同的状态时,才把此次状态改变传送到内核,否则会当成杂波滤除。

量化窗口的宽度与采样周期和采样个数有关,当采样周期和采样个数确定之后,量化窗口的宽度就确定了。量化窗口与采样周期及采样个数的关系如表所示。

现举例说明量化窗口的用法及效果。假如某个GPIO引脚为数字输入,量化模式为6个采样周期量化,采样周期寄存器中QUxLPRDn值为一,则采样周期为两个系统时钟周期宽度,量化输入的结果如图所示。

eQEP是28335用在运动控制系统中获得电机的位置信息、速度信息和方向的和编码器直接接口的模块。

有四个输入引脚:两个是正交脉冲方式或者是方向-脉冲方式引脚,一个索引或者叫零位引脚,最后一个是事件引脚。后两个还可以作为位置比较输出引脚。

包括一下几个子模块单元:

(1)QDU(正交解码单元)

可以接收正交编码器输出的正交信号,进入此单元可以进行极性的改变和两相信号的互换,在解码逻辑中进行4*倍频,得到4*后的脉冲串和方向送入计数单元。也可以接收脉冲方向信号,当接收此编码器信号时解码单元只对脉冲信号进行监测,通过配置寄存器可以选择对脉冲信号进行上升沿监测或者上升沿和下降沿监测,从而进行1*或2*倍频,把信号送入计数单元。

(2)PCCU(位置计数和控制单元)

此单元有一个位置计数器,对QDU解码过的信号进行计数,从而得到位置信息,计数方式可以通过寄存器选择,如根据索引引脚或者事件引脚进行计数器的复位或者锁存位置信息。此单元还包括一个位置比较单元,位置比较寄存器里的值和位置计数器里的值相匹配的时候产生一个位置匹配中断,同时产生匹配输出,可以配置索引引脚或事件引脚作为输出引脚。通过相关寄存器可以配置输出的脉冲宽度和极性。

(3)QCP(边缘捕获单元)

此单元可以计算速度,低速和高速时的速度计算方法不相同,低速时采用v(k)=X/t(k)-t(k-1)=X/△t,X为单位编码器脉冲,t通过QCP单元的时间计数器进行计算,当X值满足设定的值时,会产生一个事件,这时可以读时间计数器里的值进行速度V的计算。高速时采用v(k)=X(k)-X(k-1)/T=△X/T,计算时用到单位时间基子模块产生单位时间,在单位时间里通过读取PCCU单元里的△X可以计算高速时的速度。

(4)Watchdog(看门狗单元)

此单元有一个周期寄存器和计数器,计数器时钟采用SYSCLKOUT/64,解码单元的脉冲可以复位计数器,当没有脉冲复位时当达到周期值时就产生中断,可以非使能此模块。

(完整word版)各种接口针脚定义大全,推荐文档

3.5mm插头 最常见的立体声耳机分三层,标准分布为“左右地红白”(从端部到根部依次是左声道、右声道、地线,其中左声道常用红色线皮,右声道常用白色的)。 最常见的是银白色的和铜黄色的,银色的是铜镀银,铜黄色的就是铜。由于银的稳定性和电子工程性优于铜,所以铜镀上银后可以升级使用该插头设备的用户体验。 USB接口 USB是一种常用的pc接口,他只有4根线,两根电源两根信号,故信号是串行传输的,usb接口也称为串行口,usb2.0的速度可以达到480Mbps。可以满足各种工业和民用需要.USB接口的输出电压和电流是: +5V 500mA 实际上有误差,最大不能超过+/-0.2V 也就是4.8-5.2V 。usb接口的4根线一般是下面这样分配的,需要注意的是千万不要把正负极弄反了,否则会烧掉usb设备或者电脑的南桥芯片:黑线:gnd 红线:vcc 绿线:data+ 白线:data-

USB接口定义图 USB接口定义颜色 一般的排列方式是:红白绿黑从左到右 定义: 红色-USB电源:标有-VCC、Power、5V、5VSB字样 白色-USB数据线:(负)-DATA-、USBD-、PD-、USBDT- 绿色-USB数据线:(正)-DATA+、USBD+、PD+、USBDT+ 黑色-地线: GND、Ground USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB数据线而仅仅包含与电脑相连的“A”连接头)。 USB接口是一种越来越流行的接口方式了,因为USB接口的特点很突出:速度快、兼容性好、不占中断、可以串接、支持热插拨等等,

JTAG接口的定义及常见问题

JTAG接口的定义及常见问题 ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM 系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。 1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的? 下图是JTAG接口的信号排列示意: 接口是一个20脚的IDC插座。下表给出了具体的信号说明: 表 1 JTAG引脚说明 序号信号名方向说明 1 Vref Input 接口电平参考电压,通常可直接接电源 2 Vsupply Input 电源 (设备提供) 3 nTRST Output (可选项) JTAG复位。在目标端应加适当的上拉电阻以防止误触发。 4 GND -- 接地 5 TDI Output Test Data In from Dragon-ICE to target. 6 GND -- 接地 7 TMS Output Test Mode Select 8 GND -- 接地 9 TCK Output Test Clock output from Dragon-ICE to the target 10 GND -- 接地 11 RTCK Input (可选项) Return Test Clock。由目标端反馈给Dragon-ICE的时钟信号,用来同步TCK信号的产生。不使用时可以直接接地。12 GND -- 接地

13 TDO Input Test Data Out from target to Dragon-ICE. 14 GND -- 接地 15 nSRST Input/Output (可选项) System Reset,与目标板上的系统复位信号相连。可以直接对目标系统复位,同时可以检测目标系统的复位情况。为了防止误触发,应在目标端加上适当的上拉电阻。 16 GND -- 接地 17 NC -- 保留 18 GND -- 接地 19 NC -- 保留 20 GND -- 接地 2.目标系统如何设计? 目标板使用与Dragon-ICE一样的20脚针座,信号排列见表1。RTCK和 nTRST 这两个信号根据目标ASIC有否提供对应的引脚来选用。nSRST则根据目标系统的设计考虑来选择使用。下面是一个典型的连接关系图: 复位电路中可以根据不同的需要包含上电复位、手动复位等等功能。如果用户希望系统复位信号nSRST能同时触发JTAG口的复位信号nTRST,则可以使用一些简单的组合逻辑电路来达到要求。后面给出了一种电路方案的效果图。

(完整版)各种接口针脚定义大全,推荐文档

3.5mm 插头 最常见的立体声耳机分三层,标准分布为“左右地红白”(从端部到根部依次是左声道、右声道、地线,其中左声道常用红色线皮,右声道常用白色的)。 最常见的是银白色的和铜黄色的,银色的是铜镀银,铜黄色的就是铜。由于银的稳定性和电子工程性优于铜,所以铜镀上银后可以升级使用该插头设备的用户体验。 USB 接口 USB 是一种常用的 pc 接口,他只有 4 根线,两根电源两根信号,故信号是串行传输的,usb 接口也称为串行口,usb2.0 的速度可以达到 480Mbps。可以满足各种工业和民用需要.USB 接口的输出电压和电流是: +5V 500mA 实际上有误差,最大不能超过+/-0.2V 也就是4.8-5.2V 。usb 接口的 4 根线一般是下面这样分配的,需要注意的是千万不要把正负极弄反了,否则会烧掉 usb 设备或者电脑的南桥芯片:黑线:gnd 红线:vcc 绿线:data+ 白线:data-

USB 接口定义颜色 一般的排列方式是:红白绿黑从左到右 定义: 红色-USB 电源:标有-VCC、Power、5V、5VSB 字样 白色-USB 数据线:(负)-DATA-、USBD-、PD-、USBDT- 绿色-USB 数据线:(正)-DATA+、USBD+、PD+、USBDT+ 黑色-地线: GND、Ground USB 接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建 USB 数据线而仅仅包含与电脑相连的“A”连接头)。 USB 接口是一种越来越流行的接口方式了,因为 USB 接口的特点很突出:速度快、兼容性好、不占中断、可以串接、支持热插拨等 USB 接口定义图

Jtag的各种引脚定义

Jtag的各种引脚定义 使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。 以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。 Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。正版的Jlink是卖的很贵的。大概是1000到2000RMB吧。不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。 除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。还有人制作了开源版本的JTAG仿真器——OpenJTAG。而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。还有飞思卡尔公司的USBDM和OSJTAG。他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。 今天我要说的是几种JTAG仿真器的引脚定义,首先我看看比较常见的JTAG 20-Pin的引脚接口如下:

完整word版各种接口针脚定义大全

3.5mm 插头 最常见的立体声耳机分三层,标准分布为“左右地红白”(从端部到根部依次是左声道、右声道、地线,其中左声道常用红色线皮,右声道常用白色的)。 最常见的是银白色的和铜黄色的,银色的是铜镀银,铜黄色的就是铜。由于银的稳定性和电子工程性优于铜,所以铜镀上银后可以升级使用该插头设备的用户体验。 USB接口 USB是一种常用的pc接口,他只有4根线,两根电源两根信号,故信号是串行传输的,usb接口也称为串行口, usb2.0的速度可以达到480Mbps。可以满足各种工业和民用需要.USB接口的输出电压和电流是: +5V 500mA 实际上有误差,最大不能超过+/-0.2V 也就是4.8-5.2V 。usb接口的4根线一般是下面这样分配的,需要注意的是千万不要把正负极弄反了,

否则会烧掉usb设备或者电脑的南桥芯片:黑线:gnd 红线:vcc 绿线:data+ 白线:data- 1 USB接口定义图 USB接口定义颜色 一般的排列方式是:红白绿黑从左到右 定义: 红色-USB电源:标有-VCC、Power、5V、5VSB字样 白色-USB数据线:(负)-DATA-、USBD-、PD-、USBDT- 绿色-USB数据线:(正)-DATA+、USBD+、PD+、USBDT+ 黑色-地线: GND、Ground USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB数据线而仅仅包含与电脑相连的“A”连

接头)。 USB接口是一种越来越流行的接口方式了,因为USB接口的特点很突出:速度快、兼容性好、不占中断、可以串接、支持热插拨等等, 2 所以如今有许多打印机、扫描仪、数字摄像头、数码相机、MP3播放器、MODEM等都开始使用USB做为接口模式,USB接口定义也很简单: 1 +5V 2 DATA-数据- 3 DATA+数据+ 4 GND 地 串口 主板一般都集成两个串口,可Windows却最多可提供8个串口资源供硬件设置使用(编号COM1到COM8),虽然其I/O地址不相同,但是总共只占据两个IRQ(1、3、5、7共享IRQ4,2、4、6、8共享IRQ3),平常我们常用的是COM1~COM4这四个端口。我们经常在使用中遇到这个问题——如果在COM1上安装了串口鼠标或其他外设,就不能在COM3上安装如Modem之类的其它硬件,这就是因为IRQ设置冲突而无法工作。这时玩家们可以将另外的外设安装在COM2或4。 标准的串口能够达到最高115Kbps的数据传输速度,而一些增强型串口如ESP(Enhanced Serial Port,增强型串口) 、Super

RS232接口针脚定义

DB9和DB25的常用信号脚说明;RS232接口针脚定义 (2008-03-21 16:14:17) 转载 9针接口针脚定义 Pin 1 Received Line Signal Detector (Data Carrier Detect) Pin 2 Received Data Pin 3 Transmit Data Pin 4 Data Terminal Ready Pin 5 Signal Ground Pin 6 Data Set Ready Pin 7 Request To Send Pin 8 Clear To Send Pin 9 Ring Indicator RS232接口针脚定义 25针的接口定义: Pin 1 Protective Ground Pin 2 Transmit Data Pin 3 Received Data Pin 4 Request To Send Pin 5 Clear To Send Pin 6 Data Set Ready Pin 7 Signal Ground Pin 8 Received Line Signal Detector (Data Carrier Detect) Pin 20 Data Terminal Ready 接线说明 1.DB9和DB25的常用信号脚说明 9针串口(DB9) 25 针串口(DB25) 针号功能说明缩写针号功能说明缩写 1 数据载波检测 DCD 8 数据载波检测 DCD 2 接收数据 RXD 3 接收数据 RXD 3 发送数据 TXD 2 发送数据 TXD 4 数据终端准备 DTR 20 数据终端准备 DTR 5 信号地 GND 7 信号地 GND 6 数据设备准备好 DSR 6 数据准备好 DSR 7 请求发送 RTS 4 请求发送 RTS 8 清除发送 CTS 5 清除发送 CTS 9 振铃指示 DELL 22 振铃指示 DELL

JTAG各类接口针脚定义及含义

JTAG各类接口针脚定义及含义 JTAG有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的,各个引脚的定义如下。 一、引脚定义 Test Clock Input (TCK) -----强制要求1 TCK在IEEE1149.1标准里是强制要求的。TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。 Test Mode Selection Input (TMS) -----强制要求2 TMS信号在TCK的上升沿有效。TMS在IEEE1149.1标准里是强制要求的。TMS信号用来控制TAP状态机的转换。通过TMS信号,可以控制TAP在不同的状态间相互转换。 Test Data Input (TDI) -----强制要求3 TDI在IEEE1149.1标准里是强制要求的。TDI是数据输入的接口。所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。 Test Data Output (TDO) -----强制要求4 TDO在IEEE1149.1标准里是强制要求的。TDO是数据输出的接口。所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。 Test Reset Input (TRST) ----可选项1 这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。TRST可以用来对TAPController进行复位(初始化)。因为通过TMS也可以对TAP Controll进行复位(初始化)。所以有四线JTAG与五线JTAG之分。 (VTREF) -----强制要求5 接口信号电平参考电压一般直接连接Vsupply。这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?) Return Test Clock ( RTCK) ----可选项2 可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地。System Reset ( nSRST)----可选项3 可选项,与目标板上的系统复位信号相连,可以直接对目标系统复位。同时可以检测目标系统的复位情况,为了防止误触发应在目标端加上适当的上拉电阻。 USER IN 用户自定义输入。可以接到一个IO上,用来接受上位机的控制。 USER OUT 用户自定义输出。可以接到一个IO上,用来向上位机的反馈一个状态 由于JTAG经常使用排线连接,为了增强抗干扰能力,在每条信号线间加上地线就出现了这种20针的接口。但事实上,RTCK、USER IN、USER OUT一般都不使用,于是还有一种14针的接口。对于实际开发应用来说,由于实验室电源稳定,电磁环境较好,干扰不大。

JTAG接口电路

JTAG接口电路 1 JTAG(Joint Test Action Group;联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。 JTAG最初是用来对芯片进行测试的,JTAG的基本原理是在器件内部定义一个TAP(Test Access Port;测试访问口)通过专用的JTAG测试工具对进行内部节点进行测试。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。现在,JTAG接口还常用于实现ISP(In-System Programmable�在线编程),对FLASH等器件进行编程。 JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程现再装到板上因此而改变,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。JTAG接口可对PSD芯片内部的所有部件进行编程 具有JTAG口的芯片都有如下JTAG引脚定义: TCK——测试时钟输入; TDI——测试数据输入,数据通过TDI输入JTAG口; TDO——测试数据输出,数据通过TDO从JTAG口输出; TMS——测试模式选择,TMS用来设臵JTAG口处于某种特定的测试模式。 可选引脚TRST——测试复位,输入引脚,低电平有效。 含有JTAG口的芯片种类较多,如CPU、DSP、CPLD等。 JTAG内部有一个状态机,称为TAP控制器。TAP控制器的状态机通过TCK和TMS进行状态的改变,实现数据和指令的输入。图1为TAP控制器的状态机框图。 2 JTAG芯片的边界扫描寄存器 JTAG标准定义了一个串行的移位寄存器。寄存器的每一个单元分配给IC芯片的相应引脚,每一个独立的单元称为BSC(Boundary-Scan Cell)边界扫描单元。这个串联的BSC在IC内部构成JTAG回路,所有的BSR (Boundary-Scan Register)边界扫描寄存器通过JTAG测试激活,平时这些引脚保持正常的IC功能。图2为具有JTAG口的IC内部BSR单元与引脚的关系。 3 JTAG在线写Flash的硬件电路设计和与PC的连接方式 以含JTAG接口的StrongARM SA1110为例,Flash为Intel 28F128J32 16MB容量。SA1110的JTAG的TCK、TDI、TMS、TDO分别接PC并口的2、3、4、11线上,通过程序将对JTAG口的控制指令和目标代码从PC的并口写入JTAG的BSR中。在设计PCB时,必须将SA1110的数据线和地址线及控制线与Flash的地线线、数据线和控制线相连。因SA1110的数据线、地址线及

USB接口针脚定义,插口针脚识别

USB接口针脚定义,插口针脚识别 2009-11-06 12:10 USB接口通常只有4根线,两根电源线和两根数据信号线,故信号是串行传输的。USB接口也称为串行口,usb2.0的速度可以达到480Mbps。可以满足各种工业和民用需要。 USB接口的输出电压和电流是:+5V 500mA 实际上有误差,最大不能超过+/-0.2V 也就是4.8-5.2V 。usb接口的4根线一般是下面这样分配的,需要注意的是千万不要把正负极弄反了,否则会烧坏USB设备或者电脑的南桥芯片。USB接口定义如 下: USB接口定义颜色 一般的排列方式是:红白绿黑从左到右 定义: 红色-USB电源:标有-VCC、Power、5V、5VSB字样 绿色-USB数据线:(正)-DATA+、USBD+、PD+、USBDT+ 白色-USB数据线:(负)-DATA-、USBD-、PD-、 USBDT+ 黑色-地线: GND、Ground 其中ID脚在OTG功能中才使用。由于Mini-USB接口分Mini-A、B和AB接口。如果你的系统仅仅是用做Slave,那么就使用B接口。系统控制器会判断ID脚的电平判断是什么样的设备插入,如果是高电平,则是B接头插入,此时系统就做主模式(master mode) ;如果ID为低,则是A接口插入,然后系统就会使用HNP对话协议来决定哪个做Master,哪个做Slave。这些说明为技术人员总结的,仅供参考。 我们手机上一般用的都是B型Mini-USB口 关于MINIUSB 一般MINIUSB是5芯的: 1——VCC 2——D- 3——D+

4——ID 5——GND 常见USB接口识别

最新各种接口针脚定义大全

各种接口针脚定义大 全

3.5mm插头 最常见的立体声耳机分三层,标准分布为“左右地红白”(从端部到根部依次是左声道、右声道、地线,其中左声道常用红色线皮,右声道常用白色的)。 最常见的是银白色的和铜黄色的,银色的是铜镀银,铜黄色的就是铜。由于银的稳定性和电子工程性优于铜,所以铜镀上银后可以升级使用该插头设备的用户体验。 USB接口 USB是一种常用的pc接口,他只有4根线,两根电源两根信号,故信号是串行传输的,usb接口也称为串行口,usb2.0的速度可以达到480Mbps。可以满足各种工业和民用需要.USB接口的输出电压和电流是: +5V 500mA 实际上有误差,最大不能超过+/-0.2V 也就是4.8-5.2V 。usb接口的4根线一般是下面这样分配的,需要注意的是千万不要把正负极弄反了,否则会烧掉usb设备或者电脑的南桥芯片:黑线:gnd 红线:vcc 绿线:data+ 白线:data-

USB接口定义图 USB接口定义颜色 一般的排列方式是:红白绿黑从左到右 定义: 红色-USB电源:标有-VCC、Power、5V、5VSB字样 白色-USB数据线:(负)-DATA-、USBD-、PD-、USBDT- 绿色-USB数据线:(正)-DATA+、USBD+、PD+、USBDT+ 黑色-地线: GND、Ground USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB数据线而仅仅包含与电脑相连的“A”连接头)。

USB接口是一种越来越流行的接口方式了,因为USB接口的特点很突出:速度快、兼容性好、不占中断、可以串接、支持热插拨等等,所以如今有许多打印机、扫描仪、数字摄像头、数码相机、MP3播放器、MODEM等都开始使用USB做为接口模式,USB接口定义也很简单: 1 +5V 2 DATA-数据- 3 DATA+数据+ 4 GND 地 串口 主板一般都集成两个串口,可Windows却最多可提供8个串口资源供硬件设置使用(编号COM1到COM8),虽然其I/O地址不相同,但是总共只占据两个IRQ(1、3、5、7共享IRQ4,2、4、6、8共享IRQ3),平常我们常用的是COM1~COM4这四个端口。我们经常在使用中遇到这个问题——如果在COM1上安装了串口鼠标或其他外设,就不能在COM3上安装如Modem之类的其它硬件,这就是因为IRQ设置冲突而无法工作。这时玩家们可以将另外的外设安装在COM2或4。 标准的串口能够达到最高115Kbps的数据传输速度,而一些增强型串口如ESP(Enhanced Serial Port,增强型串口) 、Super

JTAG接口总结

并口与连接 1.并行口基地址: 0x0378 新系统通用,通常是LPT1,也可以是LPT2,通常使用中断IRQ7 0x0278 通常是LPT2,也可以是LPT1,LPT3(只能用此基地址),通常使用中断IRQ5 2.寄存器定义 3.状态寄存器(379)和控制寄存器(37A)的定义:

5.连接方式 a)hybus255与并口的连接是通过74CH541与并口连接 LPT D0 Pin 2 and TCK J10 Pin 4 LPT D1 Pin 3 and TDI J10 Pin 11 LPT D2 Pin 4 and TMS J10 Pin 9 LPT Busy Pin 11 and TDO J10 Pin 13 b)2410以及44b0连接图 TCK---------------->DATA0 TDI---------------->DATA1 TMS---------------->DATA2 TDO---------------->STATUS7

6.寄存器的读写 a)先对控制寄存器(Control)初始化 如果禁止中断用out(37A,0x80),如果使用中断用out(37A,0x90) b)写一个寄存器的两条基本指令: out(37B,addr);// 将addr写入用户设备地址寄存器 写:out(37C,data);// 将数据data写入addr指向的用户设备空间单元 读:in(37C);// 从addr指向的用户设备空间单元中读取数据 JTAG接口信息 1.TCK:输入移位时钟TMS和TDI的数据在TCK的上升沿被采样数据在时钟的下降沿输出到TDO 2.TMS:输入方式选择TMS用于控制TAP状态机 3.TDI:输入。输入到指令寄存器IR或数据寄存器DR的数据出现在TDI输入端在TCK的上升沿被采样 4.TDO:TDO输出来自指令寄存器或数据寄存器的数据在时钟的下降沿被移出到TDO

计算机接口大全及阵脚定义

PS2、USB、DB-9、网卡、串口、并口、VGA针脚定义及接口定义图 以下为仅为主板各接口的针脚定义,外接出来的设备接口则应与主板对应接口针脚定义相反,如鼠标的主板接口定义为6——数据,4——VCC,3——GND,1——时钟,鼠标线的接口定义则与之相反为5——数据,3——VCC,4——GND,2——时钟;其他外接设备与此相同。 首先是ATX20-Pin电源接口电源接口,根据下图你可方便判断和分辨。现在为提高CPU的供电,从P4主板开始,都有个4P接口,单独为CPU供电,在此也已经标出。

鼠标和键盘绝大多数采用PS/2接口,鼠标和键盘的PS/2接口的物理外观完全相同,初学者往往容易插错,以至于业界不得不在PC'99规范中用两种不同的颜色来将其区别开,而事实上它们在工作原理上是完全相同的,从下面的PS/2接口针脚定义我们就可以看出来。

上图的分别为AT键盘(既常说的大口键盘),和PS2键盘(即小口键盘),如今市场上PS2键盘的数量越来越多了,而AT键盘已经要沦为昨日黄花了。因为键盘的定义相似,所以两者有共同的地方,各针脚定义如下: 1、DATA 数据信号 2、空 3、GND 地端 4、+5V 5、CLOCK 时钟 6 空(仅限PS2键盘) USB(Universal Serial Bus,通用串行总线)接口是由Compaq、IBM、Microsoft等多家公司于1994年底联合提出的接口标准,其目的是用于取代逐渐不适应外设需求的传统串、并口。1996年业界正式通过了USB1.0标准,但由于未获当时主流的Win95支持(直到Win95 OSR2才通过外挂模块提供对USB1.0的支持)而未得到普及,直到1998年USB1.1标准确立和Win98内核正式提供对USB接口的直接支持之后,USB才真正开始普及,到今天已经发展到USB2.0标准。 USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB数据线而仅仅包含与电脑相连的“A”连接头)。 USB接口是一种越来越流行的接口方式了,因为USB接口的特点很突出:速度快、兼容性好、不占中断、可以串接、支持热插拨等等,所以如今有许多打印机、扫描仪、数字摄像头、数码相机、MP3播放器、MODEM等都开始使用USB做为接口模式,USB接口定义也很简单: 1 +5V 2 DATA-数据- 3 DATA+数据+ 4 GND 地 主板一般都集成两个串口,可Windows却最多可提供8个串口资源供硬件设置使用(编号

Jtag的各种引脚定义

使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。 以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。 Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。正版的Jlink是卖的很贵的。大概是1000到2000RMB吧。不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。 除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。还有人制作了开源版本的JTAG仿真器——OpenJTAG。而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。还有飞思卡尔公司的USBDM和OSJTAG。他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。 今天我要说的是几种JTAG仿真器的引脚定义,首先我看看比较常见的JTAG 20-Pin的引脚接口如下:

IDE接口及针脚定义

IDE接口及针脚定义 November 12th, 2009 § 0 目前硬盘接口常见的就三种:IDE、SATA、SCSI。IDE是比较老的接口了,现在基本上使用SATA接口,现在很多新主板上都找不到IDE接口了,市面上的硬盘也清一色的SATA接口的。当然,我们说的是民用市场,像超市收款机等专门的设备上很多还是用的IDE的。SCSI是面向服务器的,产品是价高稳定。 IDE:Integrated Drive Electronics,也就是我们平时说的串行接口(注意不是串口)。由 Compaq 和 Western Digital 公司开发,新版的 IDE 命名为 ATA 即 AT bus Attachment,IDE 接口在设备和主板侧的外观为 40 脚插针。 IDE数据线:IDE数据线是扁平的40针或者80针的,可以连接两个IDE设备。 IDE数据线的接口是公头,主板上的IDE接口是母头(这个公母应该还是很好区分)。IDE数据线第一根针是连接红线或者黑线,就是一排线中最边上颜色不一样的那一根。 IDE针脚定义: Pin 1 Reset 复位硬盘(就是硬盘重启) Pin 2 Ground 接地 Pin 3-18 D ata 这几个接口传输数据信号 Pin 19 Ground 接地 Pin 20 空空,什么也不接 Pin 21 DMARQ DMA Request-DMA请求信号 Pin 22 Ground 接地 Pin 23 I/O write 写选通信号 Pin 24 Ground 接地 Pin 25 I/O read 读选通信号 Pin 26 Ground 接地 Pin 27 IOCHRDY I/O Channel Ready-设备就绪 信号 Pin 28 Cable select 主从设备选择 Pin 29 DMAACK DMA Acknowledge-DMA响应信 号 Pin 30 Ground 接地 Pin 31 IRQ Interrupt request-中断请 求信号 Pin 32 IOCS16 为IO片选16 Pin 33 Addr 1 地址1

嵌入式开发JTAG接口的应用介绍

嵌入式开发JTAG接口的应用介绍 通常所说的JTAG大致分两类,一类用于测试芯片的电气特性,检测芯片是否有问题;一类用于Debug;一般支持JTAG的CPU内都包含了这两个模块。 一个含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU 的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers,GPIO等等的寄存器。上面说的只是JTAG接口所具备的能力,要使用这些功能,还需要软件的配合,具体实现的功能则由具体的软件决定。例如下载程序到RAM功能。了解SOC的都知道,要使用外接的RAM,需要参照SOCDataSheet的寄存器说明,设置RAM的基地址,总线宽度,访问速度等等。有的SOC则还需要Remap,才能正常工作。运行Firmware时,这些设置由Firmware的初始化程序完成。但如果使用JTAG接口,相关的寄存器可能还处在上电值,甚至时错误值,RAM不能正常工作,所以下载必然要失败。要正常使用,先要想办法设置RAM。在ADW中,可以在Console窗口通过Let 命令设置,在AXD中可以在Console窗口通过Set 命令设置。 下面是一个设置AT91M40800的命令序列,关闭中断,设置CS0-CS3,并进行Remap,适用于AXD(ADS带的Debug) setmem 0xfffff124,0xFFFFFFFF,32 ---关闭所有中断 setmem 0xffe00000,0x0100253d,32 ---设置CS0 0xffe00004,0x02002021,32 ---设置CS1 setmem 0xffe00008,0x0300253d,32 ---设置CS2 setmem 0xffe0000C,0x0400253d,32 ---设置CS3 setmem 0xffe00020,1,32 ---Remap 如果要在ADW(SDT带的DEBUG)中使用,则要改为: let 0xfffff124=0xFFFFFFFF ---关闭所有中断

JTAG接口连接方法

我的JLINK终于用上了,哈哈,好开心,终于不用考虑是不是要借用别人的PC 机了,昨天到城隍庙电子市场忙活了一下午,终于算是满载而归,呵呵,好了,下面说一下接法,其实根本不需要什么转接板什么的,直接把相应的几根线对接就可以用了,所以要参考电路图,上面为TQ2440开发板的JTAG电路图,下面为JLINK的20针电路图,下面的JLINKV7电路图是标准接口,网上到处都能找到 10针JTAG针序20针JTAG针序信号 1,21VTref -2NC 33nTRST -4GND 55TDI -6GND 77TMS 88GND 99TCK 1010GND -11RTCK -12GND 613TDO -14GND 415RESET -16GND -17DBGRQ -18GND

-195V-Supply -20GND 实际上只需要接4跟线,4号是自连回路,不需要接,1,2接的都是1管脚,而8,10接的是GND,也可以不接 ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。 1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的? 下图是JTAG接口的信号排列示意: 接口是一个20脚的IDC插座。下表给出了具体的信号说明: 表 1 JTAG引脚说明 序号信号名方向说明 1 Vref Input 接口电平参考电压,通常可直接接电源 2 Vsupply Input 电源 3 nTRST Output (可选项) JTAG复位。在目标端应加适当的上拉电阻以防止误触发。 4 GND -- 接地 5 TDI Output Test Data In from Dragon-ICE to target. 6 GND -- 接地 7 TMS Output Test Mode Select 8 GND -- 接地 9 TCK Output Test Clock output from Dragon-ICE to the target

各种接口针脚定义

RJ45接口信号定义,以及网线连接头信号安排 以太网10/100Base-T 接口: Pin Name Description 1 TX+ Tranceive Data+ (发信号+) 2 TX- Tranceive Data- (发信号-) 3 RX+ Receive Data+ (收信号+) 4 n/c Not connected (空脚) 5 n/c Not connected (空脚) 6 RX- Receive Data- (收信号-) 7 n/c Not connected (空脚) 8 n/c Not connected (空脚) 以太网100Base-T4 接口: Pin Name Description 1 TX_D1+ Tranceive Data+ 2 TX_D1- Tranceive Data- 3 RX_D2+ Receive Data+ 4 BI_D3+ Bi-directional Data+ 5 BI_D3- Bi-directional Data- 6 RX_D2- Receive Data- 7 BI_D4+ Bi-directional Data+ 8 BI_D4- Bi-directional Data- 1 white/orange 2 orange/white 3 white/green 4 blue/white 5 white/blue 6 green/white 7 white/brown 8 brown/white 注:RJ45接口采用差分传输方式,tx+、tx-是一对双绞线,拧在一起可以减少干扰。 RJ48接口信号定义 RJ48是用于T1/E1等串行线路的接口。和以太网的RJ45是一样的。 对于接不同的传输,信号定义不一样。 RJ48口呈“凸” 这个形状,线序从左往右为87654321. 例如CT1/PRI-CSU (RJ-48C)信号定义如下 RJ-48C Pin Description 1 Receive Ring 2 Receive Tip 4 Ring

电脑主板各种接口及引脚定义

电脑主板各种接口及引脚定义,下图为常见的主板外设接口 首先是ATX 20-Pin电源接口电源接口,根据下图你可方便判断和分辨。 现在为提高CPU的供电,从P4主板开始,都有个4P接口,单独为CPU供电,在此也已经标出。

主板上CPU等网风扇接口。 主板上音频线接口。

主板SATA串口硬盘接口。 PS/2接口 鼠标和键盘绝大多数采用PS/2接口,鼠标和键盘的PS/2接口的物理外观完全相同,初学者往往容易插错,以至于业界不得不在PC'99规范中用两种不同的颜色来将其区别开,而事实上它们在工作原理上是完全相同的,从下面的PS/2接口针脚定义我们就可以看出来。

上图的分别为AT键盘(既常说的大口键盘),和PS2键盘(即小口键盘),如今市场上PS2键盘的数量越来越多了,而AT键盘已经要沦为昨日黄花了。因为键盘的定义相似,所以两者有共同的地方,各针脚定义如下: 1、DATA 数据信号 2、空 3、GND 地端 4、+5V 5、CLOCK 时钟 6 空(仅限PS2键盘) USB接口 USB(Universal Serial Bus,通用串行总线)接口是由Compaq、IBM、Microsoft 等多家公司于1994年底联合提出的接口标准,其目的是用于取代逐渐不适应外设需求的传统串、并口。1996年业界正式通过了USB1.0标准,但由于未获当时主流的Win95支持(直到Win95 OSR2才通过外挂模块提供对USB1.0的支持)而未得到普及,直到1998年USB1.1标准确立和Win98内核正式提供对USB接口的直接支持之后,USB才真正开始普及,到今天已经发展到USB2.0标准。 USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB数据线而仅仅包含与电脑相连的“A”连接头)。Negative data ,positive data

JTAG接口介绍

JTAG(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP(Test Access Port,测试访问口),通过专用的JTAG测试工具对内部节点进行测试。 目前大多数比较复杂的器件都支持JTAG协议,如ARM、DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。 JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。JTAG接口还常用于实现ISP(In-System Programmable在系统编程)功能,如对FLASH器件进行编程等。 通过JTAG接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。目前JTAG接口的连接有两种标准,即14针接口和20针接口,其定义分别如下所示。 14针JTAG接口定义: 14针JTAG接口定义引脚名称描述 1、13VCC接电源 2、4、6、8、10、14GND接地 3nTRST测试系统复位信号 5TDI测试数据串行输入 7TMS测试模式选择 9TCK测试时钟

11TDO测试数据串行输出 12NC未连接 20针JTAG接口定义引脚名称描述 1VTref目标板参考电压,接电源 2VCC接电源 3nTRST测试系统复位信号 4、6、8、10、12、14、16、18、20GND接地 5TDI测试数据串行输入 7TMS测试模式选择 9TCK测试时钟 11RTCK测试时钟返回信号 13TDO测试数据串行输出 15nRESET目标系统复位信号 17、19NC未连接 下面以S3C4510B开发板为例说明JTAG接口: 在保证电源电路、晶振电路和复位电路正常工作的前提下,可通过JTAG接口调试S3C4510B,在系统上电前,首先应检测JTAG接口的TMS、TCK、TDI、TDO信号是否已与S3C4510B 的对应引脚相连,其次应检测S3C4510B的nEWAIT引脚(Pin71)是否已上拉,ExtMREQ 引脚(Pin108)是否已下拉,对这两只引脚的处理应注意,作者遇到多起S3C4510B不能正常工作或无法与JTAG接口通信,均与没有正确处理这两只引脚有关。 给系统上电后,可通过示波器查看S3C4510B对应引脚的输出波形,判断是否已正常工作,若S3C4510B已正常工作,在使能片内PLL电路的情况下,SDCLK/MCLKO引脚(Pin77)应输出频率为50MHz的波形,同时,MDC引脚(Pin50)和其他一些引脚也应有波形输出。