加法器电路的设计

加法器电路的设计

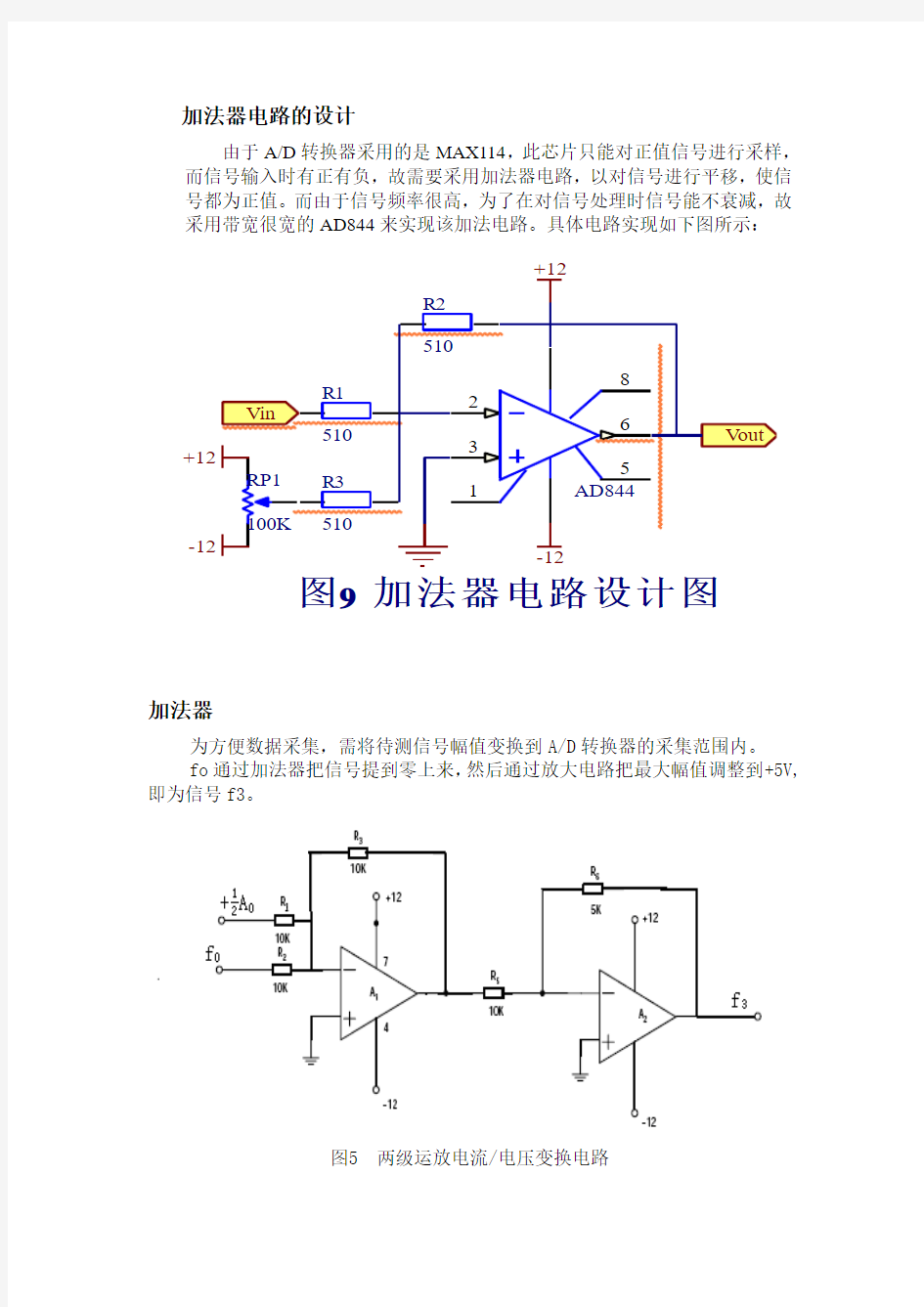

由于A/D 转换器采用的是MAX114,此芯片只能对正值信号进行采样,而信号输入时有正有负,故需要采用加法器电路,以对信号进行平移,使信号都为正值。而由于信号频率很高,为了在对信号处理时信号能不衰减,故采用带宽很宽的AD844来实现该加法电路。具体电路实现如下图所示:

加法器

为方便数据采集,需将待测信号幅值变换到A/D 转换器的采集范围内。 fo 通过加法器把信号提到零上来,然后通过放大电路把最大幅值调整到+5V,即为信号f3。

图5 两级运放电流/电压变换电路

+12

-12图9 加法器电路设计图

实验一-加法器的设计与实现讲解

实验项目二:简单计算器设计与实现基本要求: 1. 能够实现加减运算 2. 能够实现乘法运算 扩展要求: 1.能够实现除法运算 一、实验目的 利用原件例化语句完成一个8位加法器的设计。 二、实验环境 Quartus II 开发系统 三、实验内容 1、掌握层次化设计的方法; 2、掌握一位全加器工作原理; 3、掌握用VHDL文本输入法设计电子线路的详细流程; 4、掌握元件例化语句用法; 5、熟悉软硬件设计验证方法。 四、实验过程 设计思想: 8位二进制加法器可以由8个全加器通过级联的方式构成。根据全加器级联的原理,用VHDL设计一个8位二进制数的加法器,可以先设计一个一位全加器,然后利用一位全加器采用元件例化的方式实现加法器。 实验步骤: 1、设计一个全加器 新建工程,建立源文件,输入VHDL设计文件,如下图所示:

完成设计文件输入后,保存文件,对文件进行编译、仿真,以下是仿真结果,如图所示: 由图可知仿真结果正确。 2、元件例化 把VHDL设计文件转为原理图中使用的元件。在文件菜单File中选择Creat/Update选项,单击Create Symbol File for Current File 选项,系统自动生成相应的元件标号。 重复新建文件的操作,选择Block Diagram/Schmatic File 选项,新建一个原理图文件,在添加元件列表中可以看到自动生成的元件,选择full_adder这个元件添加到原理图中,如下图所示:

3、完成顶层图的设计 用生成的元件标号,完成顶层图的设计。这里有两种方法,一种是直接用原理图设计,根据原理图设计工具的使用方法,完成顶层文件的设计,这个方法比较复杂,所以这里选择另一种方法,通过VHDL设计文件。 继续建立源文件,输入VHDL设计文件,如下图所示: 依照上述步骤,保存文件,对文件进行编译、仿真,以下是仿真结果,如图所示:

集成电路设计基础_期末考试题

集成电路设计基础 2010-11年第一学期试题 一、填空题(20分) 1、目前,国内已引进了12英寸0.09um 芯片生产线,由此工艺线生产出来的集成 电路特征尺寸是0.009um (大 小),指的是右图中的W (字 母)。 2、CMOS工艺可分为p阱、n阱、双阱 三种。 在CMOS工艺中,N阱里形成的晶体管是p (PMOS,NMOS)。 3、通常情况下,在IC中各晶体管之间是由场氧来隔离的;该区域的形成用到的制造工艺是氧化工艺。 4.集成电路制造过程中,把掩膜上的图形转换成晶圆上器件结构一道工序是指光 刻,包括晶圆涂光刻胶、曝光、显影、烘干四个步骤; 其中曝光方式包括①接触式、②非接触式两种。 5、阈值电压V T是指将栅极下面的si表面从P型Si变成N型Si所必要的电压,根据阈值电压的不同,常把MOS区间分成耗尽型、增强型两种。降低V T 的措施包括:降低杂质浓度、增大Cox 两种。 二、名词解释(每词4分,共20分) ①多项目晶圆(MPW) ②摩尔定律 ③掩膜 ④光刻

⑤外延 三、说明(每题5分共10分) ①说明版图与电路图的关系。 ②说明设计规则与工艺制造的关系。 四、简答与分析题(10分) 1、数字集成电路设计划分为三个综合阶段,高级综合,逻辑综合,物理综合;解释这 三个综合阶段的任务是什么? 2、分析MOSFET尺寸能够缩小的原因。 五、综合题(共4小题,40分) 1、在版图的几何设计规则中,主要包括各层的最小宽度、层与层之间的最小间距、各 层之间的最小交叠。把下图中描述的与多晶硅层描述的有关规则进行分类: (2)属于层与层之间的最小间距的是: (3)属于各层之间的最小交叠是: 2.请提取出下图所代表的电路原理图。画出用MOSFET构成的电路。

计组-加法器实验报告

半加器、全加器、串行进位加法器以及超前进位加法器 一、实验原理 1.一位半加器 A和B异或产生和Sum,与产生进位C 2.一位全加器 将一位半加器集成封装为halfadder元件,使用两个半加器构成一位的全加器 3.4位串行进位加法器 将一位全加器集成封装为Fulladder元件,使用四个构成串行进位加法器

4.超前进位加法器(4位) ⑴AddBlock 产生并行进位链中的ti(即Cthis)和di(即Cpass),以及本位结果Sum ⑵进位链(Cmaker) 四位一组并行进位链,假设与或非门的级延迟时间为1.5ty,与非门的延迟时间为1ty,在di和ti产生之后,只需2.5ty就可产生所有全部进位

⑶超前进位加法器 将以上二者结合起来即可完成,A和B各位作为各个AddBlock的输入,低一位的进位Ci-1作为本位AddBlock的C-1的输入。各个AddBlock输出的C_this和C_pass作为对应的Cmaker的thisi和passi的输入。

二、实验器材 QuartusII仿真软件,实验箱 三、实验结果 1.串行进位加法器结果 2.超前进位加法器结果

四、实验结果分析 1.实验仿真结果显示串行加法器比超前进位加法器快,部分原因应该是电路结构优化 不到位。另外由于计算的位数比较少,超前进位加法链结构较复杂,所以优势没体现出来,反倒运作的更慢一点。当位数增加的时候,超前进位加法器会比串行的更快。 2.波形稳定之前出现上下波动,应该与“竞争冒险”出现的情况类似,门的延迟和路径 的不同导致了信号变化时到达的时间有先有后,因此在最终结果形成前出现了脉冲尖峰和低谷;另外也可能部分原因由于电路结构优化的不到位所致

模拟集成电路设计期末试卷

《模拟集成电路设计原理》期末考试 一.填空题(每空1分,共14分) 1、与其它类型的晶体管相比,MOS器件的尺寸很容易按____比例____缩小,CMOS电路被证明具有_ 较低__的制造成本。 2、放大应用时,通常使MOS管工作在_ 饱和_区,电流受栅源过驱动电压控制,我们定义_跨导_来 表示电压转换电流的能力。 3、λ为沟长调制效应系数,对于较长的沟道,λ值____较小___(较大、较小)。 4、源跟随器主要应用是起到___电压缓冲器___的作用。 5、共源共栅放大器结构的一个重要特性就是_输出阻抗_很高,因此可以做成___恒定电流源_。 6、由于_尾电流源输出阻抗为有限值_或_电路不完全对称_等因素,共模输入电平的变化会引起差动输 出的改变。 7、理想情况下,_电流镜_结构可以精确地复制电流而不受工艺和温度的影响,实际应用中,为了抑制 沟长调制效应带来的误差,可以进一步将其改进为__共源共栅电流镜__结构。 8、为方便求解,在一定条件下可用___极点—结点关联_法估算系统的极点频率。 9、与差动对结合使用的有源电流镜结构如下图所示,电路的输入电容C in为__ C F(1-A)__。 10、λ为沟长调制效应系数,λ值与沟道长度成___反比__(正比、反比)。 二.名词解释(每题3分,共15分) 1、阱 解:在CMOS工艺中,PMOS管与NMOS管必须做在同一衬底上,其中某一类器件要做在一个“局部衬底”上,这块与衬底掺杂类型相反的“局部衬底”叫做阱。 2、亚阈值导电效应 解:实际上,V GS=V TH时,一个“弱”的反型层仍然存在,并有一些源漏电流,甚至当V GS 加法器设计介绍 算术逻辑部件主要处理算术运算指令和逻辑运算指令,它的核心单元是加法器。这个加法器是影响算术逻辑部件整体性能的关键部分,因为几乎所有的算术运算和逻辑运算,都要通过它来完成。 加法器结构包括串行进位加法器(Carry Ripple Adder,CRA)、进位跳跃加法器(cany skip Adder,CKA),以及较高速度的进位选择加法器(carry select Adder,CSA)、超前进位加法器(Can 了Look—a}lead Adder,CLA)和并行前缀加法器(Parallel Prcfix Adder)等。 串行进位加法器(CRA) 串行进位加法器是最简单、最基本的加法器结构。串行进位加法器的进位像水波一样依次通过每位,因此也称为“行波进位加法器”。它每次只能进行一位运算,因此速度很慢。 如下图所示 进位跳跃加法器(CKA) 进位跳跃加法器是串行进位加法器的改进结构。它将整个加法器分为几个组,如果某组的所有进位传播信号都为“1”,则将该组的进位输入直接传送到输出,而不需要进行进位运算。这个过程好像进位做了一个跳过该组的动作,因此称为进位跳跃加法器。 为了实现跳跃进位,每组需要增加一个多路选择器和一个与门,这种结构可以提高加法器的运算速度,但是,速度的提高只有在某些特定的情况下才会出现。如下图所示 进位选择加法器(CSA) 进位选择加法器采用资源复制的基本思想,用硬件来换取速度。它将整个加法器分为几 个组,每组有两条路径,进位输入为“O”和“1”的两种情况通过两条路径同时计算。一 旦该组进位输入信号到来,通过多路选择器选择正确的进位输出与和值。如下图所示 由于采用了前瞻的思想,因此进位选择加法器的速度有很大提高。如果整个加法器分为 M 组,则运算延时可由第一组进位延时、M 个多路选择器的延时及一个和产生延时相加得到。进位选择加法器虽然具有较快的速度,但由于它采用了资源复制的方法,因此实现代价 也成倍增加。 一般的进位选择加法器每组具有相同的位数,延迟也与位数成线性关系,称为“线性进 位选择加法器”。如果不把每组设置为相同的位数,而是从低位到高位组内位数逐渐增大, 例如第一组2 位,第二组3 位,等三组4 位,等等。这种逐组位数加长的方法使加法器结构具有亚线性延迟的特性。经过计算,这种结构的延迟与位数的平方根成正比,因此称为“平 方根进位选择加法器”。 报告课设 集成电路设计方向综合课程设计课程名称 实验项目加法器 PC机、candence软件实验仪器 _ 别______系理学院 杨凯 __ ________ 姓名 ____ __________实验日期 _______________________绩成 目录 ...................................................................... 3一、概述 4 ................................................................... 1.1课题背景4................................................................. 1.2课题意义 .................................................................. 5二、设计流 程 .................................................................. 5三、课设内 容 .................................................................. 5四、实验原理 5............................................................. 4.1加法器基本原理 6........................................................ 半加器基本原理 .4.1.1 7........................................................ 全加器基本原理 .4.1.2 8................................................................ 镜像加法器 4.2. ............................................................... 10五、上机步骤: 01 ............................................................. 5.1.画电路图步骤 11 ................................................................ 5.2画版图步骤........................................................... 11.六、加法器电路图:2.................................................................. 16.1原理图: 2.......................................................... 16.2全加器电路图结构 3............................................................ 16.3自己画的电路图3................................................................ 16.4波形验证: 41 ........................................................... 6.5(瞬态)分析 TRAN41波形输出参数 .............................................................. 6.6 61管全加器网表 ........................................................... 6.728 7.................................................................. 16.8仿真波形7...................................................... 16.9编译仿真波形结果分析 ................................................................. 18七、版图设计81版图7.1 ...................................................................... 版图(L)是集成电路设计者将设计并模拟优化后的电路转化成的一系列几何图形,包含AYOUT了集成电路尺寸大小、各层拓扑定义等有关器件的所有物理信息。版图的设计有特定的规则,这些规则是集成电路制造厂家根据自己的工艺特点而制定的。不同的工艺,有不同的设计规则。版图在设计的过程中要进行定期的检查,避免错误的积累而导致难以修改。版图设计流8......................................................................... 1 程:.91版图设计规则7.2 .............................................................. 0................................................................ 2 7.3修改前版图 1................................................................ 2 修改后版图7.4 ................................................................. 22八、课设心得一、概述 集成电路是采用专门的设计技术和特殊的集成工艺技术,把构成半导体电路的晶体管、二极管、电阻、电容等基本单元器件,制作在一块半导体单晶片(例如硅或者砷化镓)或者陶瓷等绝缘基片上,并按电路要求完成元器件间的互连,再封装在一个外壳内,能完成特定的电路功能或者系统功能,所有的元器件及其间的 加法器实验报告 篇一:加法器实验报告 实验 __一__ 【实验名称】 1位加法器 【目的与要求】 1. 掌握1位全加器的设计 2. 学会1位加法器的扩展 【实验内容】 1. 设计1位全加器 2. 将1位全加器扩展为4位全加器 3. 使4位的全加器能做加减法运算 【操作步骤】 1. 1位全加器的设计 (1)写出1位全加器的真值表 (2)根据真值表写出表达式并化简 (3)画出逻辑电路 (4)用quartusII进行功能仿真,检验逻辑电路是否正确,将仿真波形截图并粘贴于此 (5)如果电路设计正确,将该电路进行封装以用于下一个环节 2. 将1位全加器扩展为4位全加器 (1)用1位全加器扩展为4位的全加器,画出电路图 (2)分别用两个4位补码的正数和负数验证加法器的正确性(注意这两 个数之和必须在4位补码的数的范围内,这两个数包括符号在内共4位),用quartusII进行功能仿真并对仿真结果进行截图。 3. 将4位的全加器改进为可进行4位加法和减法的运算器 (1)在4位加法器的基础上,对电路进行修改,使该电路不仅能进行加 法运算而且还能进行减法运算。画出该电路 (2)分别用两个4位补码的正数和负数验证该电路的正确性(注意两个 数之和必须在4位补码的数的范围内),用quartusII进行功能仿真并对仿真结果进行截图。 【附录】 篇二:加法器的基本原理实验报告 一、实验目的 1、了解加法器的基本原理。掌握组合逻辑电路在Quartus Ⅱ中的图形输入方法及文本输入方法。 2、学习和掌握半加器、全加器的工作和设计原理 3、熟悉EDA工具Quartus II和Modelsim的使用,能够熟练运用Vrilog HDL语言在Quartus II下进行工程开发、调试和仿真。 实验一半加器设计 一、实验目的 1、了解和学习Quartus II 5.1 软件设计平台。 2、了解EDA的设计过程。 3、通过实例,学习和掌握Quartus II 5.1 平台下的图形输入法 4、学习和掌握半加器的工作和设计原理。 二、实验仪器 PC机,操作系统为Windows2000/XP,本课程所用系统均为WindowsXp下同),Quartus II 5.1 设计平台。 三、实验原理 加法器是构成算术运算器的基本单元,有来自低位的进位将两个1位二进制数相力口,称为半加。实现半加运算的电路叫做半加器。 按照二进制加法运算规则可以列出如表1-1所示的半加器真值表。其中A、B是两个加数,S是相加的和,CO是相加高位的进位。将S、CO和A、B的关系写成逻 辑表达式如下: S 二AB AB = A: B CO 二AB 四、实验步骤 1、启动Quartus II 5.1 :在Windows操作系统下,单击"开始”,选择"程序”,再选择"altera ”选项下的"Quartus II 5.1 ”命令。 2、新建工程:在File菜单中选择New Project Wizard …,弹出对话框如图1-1所示 图1 — 1 在这个对话框中,第一行是需要你指定项目保存的路径,支持含中文字符的路径,第二行是 需要你为这个项目取一个名称,第三行是需要你为这个项目的顶层实体取个名称,如实验不 需要使用芯片,这三个设定好后,点击“ finish ”。(如何使用芯片及各参数设定将在实验 3 中讲到)出现如下界面 在File 菜单中选择New,出现一个对话框如图 1 — 2 图1 — 2 选择 Block Diaqram/Schematic File ,然后点击 "OK ”。 ft QuBEtus TK - £:7>uuiiKn!x mJ 5D 3i E x/tafi/|Krii/ 3/d D ? - -£Bl?i£kl .MFj tils £di L £LM * frajiiri,占■■LfriaAB tiaLi [lain Ukl? □ GS ? 筍而訂 T 旦才?曙涉C ?轿峙fe ? 0 IkCLTJ^ dm AI .TO 'i. SyriE-Hi/i Pltionti^j k /i B I-A J "Vt'-mmy 扎 CiifcdiWkniW 扎 Eiot 人行WM J Nfrlrtfl? p 暑讣1 F4t IN IK TiRii Fl EH. "V |础 1■■中■ | Mb 图1 — 3 4、 保存文件:选菜单File'Save ,在弹出的Save As 对话窗口中,指定存放文件类型、 文件夹和文件名。这一步也可以放在图形设计完成后进行。 5、 原理图设计输入: (1 )元器件符号放置 通过Edit->lnsert Symbol 插入元器件或点击图板左侧的快捷键 卜' I Symbol,或双击图板 3 、新建文件 \ l± 课设报告 课程名称集成电路设计方向综合课程设计实验项目加法器 实验仪器PC机、candence软件 系别______理学院_ 姓名______ 杨凯__ __ 实验日期____ __________ 成绩_______________________ 目录 一、概述 (3) 1.1课题背景 (4) 1.2课题意义 (4) 二、设计流程 (5) 三、课设内容 (5) 四、实验原理 (5) 4.1加法器基本原理 (5) 4.1.1 半加器基本原理 (5) 4.1.2 全加器基本原理 (6) 4.2.镜像加法器 (8) 五、上机步骤: (10) 5.1.画电路图步骤 (10) 5.2画版图步骤 (11) 六、加法器电路图: (11) 6.1原理图: (12) 6.2全加器电路图结构 (12) 6.3自己画的电路图 (13) 6.4波形验证: (13) 6.5 TRAN(瞬态)分析 (14) 6.6波形输出参数 (14) 6.728管全加器网表 (16) 6.8仿真波形 (17) 6.9编译仿真波形结果分析 (17) 七、版图设计 (18) 7.1版图 (18) 版图(L AYOUT)是集成电路设计者将设计并模拟优化后的电路转化成的一系列几何图形,包含了集成电路尺寸大小、各层拓扑定义等有关器件的所有物理信息。版图的设计有特定的规则,这些规则是集成电路制造厂家根据自己的工艺特点而制定的。不同的工艺,有不同的设计规则。版图在设计的过程中要进行定期的检查,避免错误的积累而导致难以修改。版图设计流程: (18) 7.2版图设计规则 (19) 7.3修改前版图 (20) 7.4修改后版图 (21) 八、课设心得 (22) 中文摘要和关键词 微机原理课程设计——8255,加法器设计2 本实验是对加法器的输入、运算、输出而进行的编程,利用了8255芯片,通过8255的A,B端口输入两个八位二进制数,经CPU运算后,由C端口输出. 通过编写相应程序用8086/8088的“OUT”指令可将8255的控制字送入其控制字寄存器所对应的地址,以达到将控制字送入8255的目的,以此来控制8255的工作方式以及A、B、C三个端口的输入,输出状态,格式化8255。本实验8255工作在方式0,即基本输入输出状态,A、B端口是输入状态,C端口是输入状态。再用相同方法可将8255的A、B两个端口的内容送入A、B两个端口。 通过A,B端口输入的两个二进制数经编程运算,然后在C口输出,通过循环语句实现两个二进制数求和的连续运算、输出. 关键字: 循环、工作方式、编程、运算、格式化 目录 课程设计任务书 1设计任务描述 1.1 设计目的 1.2 设计的要求 1.3对设计说明书撰写内容、格式、字数的要求 1.4设计完成后应提交成果的种类、数量、质量等方面的要求 1.5时间进度安排 2微机原理课程设计成绩评定表 3 设计思路 (3) 4 设计原理流程图.............………..….……..….………………….…..….…...…4~5 4.1主程序 4.2键盘扫描子程序 5 实际硬件接线图 (6) 6 源程序清单及注释…………..………..….….……………………….…………7~9 7主要元器件介绍………………………………………………………………10~12 7.1键盘 7.1.1键盘的工作原理 7.1.2键盘输入信息的过程 7.1.3键盘扫描(识别键)的过程 7.2 可编程并行接口8255A 7.2.1 8255简介 7.2.2 8255的控制字 参考文献 (13) 设计总结 (14) 《模拟集成电路设计》复习 答疑安排: 第13周星期二(5月29日),上午9:00-11:30,下午14:30-17:00,工三310 考试题型: 七道大题:第2章一题,第3、4章各两题,第5章一题,第6、7章共一题 考试注意事项: 所有题目采用课本P32表2.1的数据,V DD=3V,C OX=3.84 10-7F/cm2,忽略漏/源横向扩散长度L D。试题会给出所需参数值。 时刻区分大信号、小信号。 时刻注意是否考虑二级效应。 题目有“推导”两字时,需给出求解过程。 必考:画小信号等效电路 复习题 例2.2补充问题:(1)分析MOS工作区间变化情况;(2)画出I D-V DS 曲线;(3)推导线性区跨导表达式。 习题2.2注意:跨导的单位。 习题2.3补充问题:给定参数值,计算本征增益的数值。注意:画曲线时需考虑λ与L的关系。 例3.5 补充问题:画出图3.21(b)电路的小信号等效电路,推导增益表达式。 习题3.2问题(b)删去。补充问题:求R out。 习题3.12解题思路:I1→V out→V GS2→(W/L)2→A v 习题3.14 输出摆幅=V DD-V OD1-|V OD2|。 解题思路:A v,R out→g m1→(W/L)1→V OD1→|V OD2|→(W/L)2 第4章课件第49页的题目差模增益-g m1(r o1||r o3),共模增益0,共模抑制比+∞ 例4.6 习题4.18 只要求图4.38(a)-(d)。补充问题:画出半边电路。注意:画半边电路时去掉电流源M5。 习题4.25 计算过驱动电压V OD时忽略沟道长度调制效应。注意双端输出摆幅为单端时的2倍。 习题5.1问题(e)删去。问题(c)和(d)有简单的计算方法。 习题5.5问题(b)(c)删去。λ=0。 例6.4补充问题:画出低频小信号等效电路,推导低频小信号增益;写出C D、C S分别包含哪些MOS电容。 习题6.9 只要求图6.39(a)(b)(c)。 例7.11只计算热输入参考噪声电压。 习题7.11补充问题:推导小信号增益。 课题名称与技术要求 课题名称: 四位二进制加法器设计 技术要求: 1)四位二进制加数与被加数输入 2)二位数码管显示 摘要 本设计通过八个开关将A3,A2,A1,A0和B3,B2,B1,B0信号作为加数和被加数输入四位串行进位加法器相加,将输出信号S3,S2,S1,S0和向高位的进位 C3通过译码器Ⅰ译码,再将输出的Y3,Y2,Y1,Y0和X3,X2,X1,X0各自分别通过一个74LS247译码器,最后分别通过数码管BS204实现二位显示。 本设计中译码器Ⅰ由两部分组成,包括五位二进制译码器和八位二进制输出器。信号S3,S2,S1,S0和向高位的进位C3输入五位二进制-脉冲产生器,将得到的n(五位二进制数码对应的十进制数)个脉冲信号输入八位二进制输出器,使电路的后续部分得以执行。 总体论证方案与选择 设计思路:两个四位二进制数的输入可用八个开关实现,这两个二进制数经全加器求和后最多可以是五位二进制数。本题又要求用两个数码管分别显示求和结果的十进制十位和各位,因此需要两个译码器Ⅱ分别译码十位和 个位。综上所述,需要设计一个译码器Ⅰ,能将求和得到的五位二进制数译成八位,其中四位表示这个五位二进制数对应十进制数的十位,另四位表示个位。而译码器Ⅱ有现成的芯片可选用,此处可选74LS247,故设计重点就在译码器Ⅰ。 加法器选择 全加器:能对两个1位二进制数进行相加并考虑低位来的进位,即相当于3个1位二进制数相加,求得和及进位的逻辑电路称为全加器。或:不仅考虑两个一位二进制数相加,而且还考虑来自低位进位数相加的运算电路,称为全加器。 1)串行进位加法器 构成:把n位全加器串联起来,低位全加器的进位输出连接到相邻的高位全加器的进位输入。 优点:电路比较简单。 最大缺点:进位信号是由低位向高位逐级传递的,运算速度慢。 2)超前进位加法器 为了提高运算速度,必须设法减小或消除由于进位信号逐级传递所消耗的时间,于是制成了超前进位加法器。 优点:与串行进位加法器相比,(特别是位数比较大的时候)超前进位加法器的延迟时间大大缩短了。 缺点:电路比较复杂。 综上所述,由于此处位数为4(比较小),出于简单起见,这里选择串行进位加法器。 译码器Ⅱ选择 译码是编码的逆过程,将输入的每个二进制代码赋予的含意“翻译”过来,给出相应的输出信号。译码器是使用比较广泛的器材之一,主要分为:变量译码器和码制译码器,其中二进制译码器、二-十进制译码器和显示译码器三种最典型,使用十分广泛。显示译码器又分为七段译码器和八段 长安大学电子技术课程设计 课题名称______________ 班级______________ 姓名______________ 指导教师 日期______________ 前言 8位二进制加法器,它的功能主要是实现两个8位二进制数的相加,其结果的范围应该在00000000到111111110之间,即000到510之间。加法器在实际应用中占据着十分重大的地位,从我们呱呱坠地起,到小学,到初中,到高中,到大学,到工作,等等。我们能离开加法吗,不能!加法可以说是一切运算的基础,因此8位二进制加法器的设计是很有必要的。 那么我们如何设计一个8位二进制加法器呢?在实际应用中,我们通常输入的是十进制数,一个八位二进制数所对应的最大的十进制数是255,于是输入两个范围在000到255之间的数,首先通过二-十进制编码器将输入的三位十进制数的个位、十位、百位分别转换为8421BCD码,得到两个十二位字码,再通过加法器将它们相加,逢10进1,得到一个新的十二位字码,再用7447数字显示译码器将这个十二位字码还原到原来的三位十进制数。最后输出的就是一个三位十进制数,其范围在000到510之间。通过上述方法我们实现了八位二进制数的相加,从而达到了题目的要求。 为实现上述目的,我们需要查阅相关资料。通过查阅,理解以及加以运用,我们认识到了收集资料的不易性,但同时也得到了不少收获,可以说是有苦有甜。同时,虽然我们基本设计出了这个八位二进制加法器,但是不必可避免地会产生一些问题,比如说在连线上可能有更简便的途径,在元件的选用上可能还有其它更简便的方法,在控制上可能还不够精简,等等。我们希望在以后的实践中能找出更好的方法,也希望能吸取这次设计中的不足,逐渐改善。另外,在电子设计的过程中,与同组同学之间的合作配和是十分重要的。我在此次设计中也充分认识到这一点的重要性,我相信这次的电子设计能够为我们将来的工作奠定一定的基础。 实验报告 课程名称: 数字系统设计实验 II 指导老师:屈民军、唐奕 成绩:_________________ 实验名称: Lab7 快速加法器的设计与应用 实验类型: 设计型 _ 一、 实验要求 实验任务为3.3:采用“进位选择加法”技术设计32位加法器 二、 实验设计思路 “进位选择加法”是通过增大元器件数量、增加硬件面积来提高运算性能。以四位先行加法器为最基本的运算单元,并在每个单元内分别计算出初始进位为‘0’和‘1’时的结果,再通过数据选择器(根据从低一级的进位信号来判断初始进位的值)选择出正确的该四位加法结果,并且将该四位中最高位的进位输出给下一级,作为下一级的初始进位输入。 具体分析:将32位的计算分为八块,0-3位为一块,4-7位一块,依次类推。除去第一块(0-3位的计算),后7块采用进位选择,即每块均计算出初始进位为‘0’或者‘1’时的情况,然后根据低一级的进位输出,来选择正确的结果。 因此,首先要设计4位的先行进位加法器。根据书上的公式,即可实现。这里可以看到,为了提高运算速度,每一个进位的计算都直接依赖于整个加法器的最初输入,而不需要等待相邻低位的进位传递。所以,在verilog 代码中关于c[3],c[2],c[1],c[0]的公式要全部展开,而不是利用前面的进位来计算后面的进位值。 之后,就是模块调用,第一块调用一个4为先行进位加法器,后面七块全部调用两个4为先行进位加法器。 专业:信息与通信工程 姓名:陈博华 学号:3120101830 日期:2014-12-01 地点:教11-400 三、verilog代码部分 整个工程(包括测试文件)的代码有 分别为:1位全加器及其测试文件,4位先行进位加法器及其测试文件,32位快速加法器及其测试文件,和数据选择器。 其中代码 为了充分加快运算速度,,每一位的进位直接依赖于整个加法器的最初输入。 四、仿真结果及其分析 1、四位先行进位加法器的仿真 沈阳航空航天大学 课程设计报告 课程设计名称:计算机组成原理课程设计 课程设计题目:定点补码加法器的设计与实现 院(系):计算机学院 专业:计算机科学与技术 班级:14010102 学号:2011040101068 姓名:李丰 指导教师:周大海 完成日期:2014年01月10日 沈阳航空航天大学课程设计报告 目录 第1章总体设计方案 (2) 1.1设计原理 (2) 1.2设计思路 (2) 1.3设计环境 (2) 第2章详细设计方案 (4) 2.1总体方案的设计与实现 (4) 2.1.1总体方案的逻辑图 (4) 2.2功能模块的设计与实现 (5) 2.2.1求补模块的设计与实现 (5) 2.2.2加法器模块的设计与实现 (7) 第3章编程下载与硬件测试 (10) 3.1编程下载 (10) 3.2硬件测试及结果分析 (10) 参考文献 (13) 附录(电路原理图) (14) 第1章总体设计方案 1.1 设计原理 本次课程设计的题目为定点补码加法器的设计,使用Xilinx Foundation F3.1可编程器件开发工具软件,以及伟福COP2000试验箱实现目的设计。具体要求为必须用基本逻辑门实现,两相加数为7位,并含有一位符号位,采用原码输入,实现编程下载和硬件调试。 本实验输入两个原码,但是因为有符号位,不利于运算,故必须先将其转化为补码形式,再进行加法运算,然后将得到的结果再求补,从而得到正确结果。原理式为:[x]补+[y]补=[x+y]补。 1.2 设计思路 定点补码加法器的设计主要包含如下3个部分: ①原码求补;②数据相加;③结果求补并输出。 在各个部分中分别设计实现相应功能的器件,包括逻辑门电路、四位加法器等。在连接具体电路时配合相应脉冲和门电路以达到预期效果。加法器的底层、顶层的设计都采用原理图设计输入方式,经编译、调试后形成*.bit文件并下载到XCV200可编程逻辑芯片中,经硬件测试验证设计的正确性。 1.3设计环境 (1)硬件环境 伟福COP2000型计算机组成原理试验仪 伟福COP2000型计算机组成原理实验系统由实验平台,开关,软件三大部分构成,该系统提供微程序控制器和组合逻辑控制器两种控制器方式,系统还支持手动方式、联机方式、模拟方式三种工作方式,具备完善的寻址方式、指令系统和强大的模拟调试功能。 (2)EDA环境 Xilinx foundation f3.1设计软件 1、 研究模拟集成电路的重要性:(1)首先,MOSFET 的特征尺寸越来越小,本征速度越来 越快;(2)SOC 芯片发展的需求。 2、 模拟设计困难的原因:(1)模拟设计涉及到在速度、功耗、增益、精度、电源电压等多 种因素间进行折衷,而数字电路只需在速度和功耗之间折衷;(2)模拟电路对噪声、串扰和其它干扰比数字电路要敏感得多;(3)器件的二级效应对模拟电路的影响比数字电路要严重得多;(4)高性能模拟电路的设计很少能自动完成,而许多数字电路都是自动综合和布局的。 3、 鲁棒性就是系统的健壮性。它是在异常和危险情况下系统生存的关键。所谓“鲁棒性”, 是指控制系统在一定的参数摄动下,维持某些性能的特性。 4、 版图设计过程:设计规则检查(DRC )、电气规则检查(ERC )、一致性校验(LVS )、RC 分布参数提取 5、 MOS 管正常工作的基本条件是:所有衬源(B 、S )、衬漏(B 、D )pn 结必须反偏 6、 沟道为夹断条件: ?GD GS DS T DS GS TH H V =V -≤V V V -V ≥V 7、 (1)截止区:Id=0;Vgs 一.课程设计的目的: 1、学习并了解MATLAB软件。 2、尝试用Simulink建模。 3、实现对数字电路的防真设计。 4、利用全加器电路创建四位二进制加法器。 二.课程设计题目描述及要求: 利用所学的数字电路的基本知识和MUTLAB软件中Simulink的应用学习,完成对数字电路的仿真设计。用各种各样的组合逻辑电路设计全加器,输出曲线,再利用全加器设计电路创建四位二进制加法器电路图,给出输出。 三.MATLAB软件简介: MATLAB是MathWorks公司于1984年推出的一套高性能的数值计算可视化软件,集数值分析、矩阵运算、信号处理和图形显示于一体。MATLAB是由Matrix 和Laboratory单词的前三个字母组合而成的,其含义是矩阵实验室。 Simulink是MATLAB最重要的组件之一,是实现动态系统建模、仿真的一个集成环境。它支持线性和非线性系统,连续时间、离散时间,或者两者的相结合的仿真,而且系统是多进程的。Simulink是从底层开发的一个完整的仿真环境和图形界面,它把MATLAB的许多功能都设计成一个个直观的功能模块,把需要的功能模块连接起来就可以实现所需要的仿真功能。Simulink仿真应用于数字电路、数字信号处理、通信仿真、电力系统仿真、宇航仿真等领域。由于数字系统中高低电平分别用0和1表示,因此数字电路问题往往可以转化为一个数字上的逻辑问题。MATLAB提供了逻辑运算模块和各种触发器模块,可以方便的进行数字电路的设计和仿真。借助于组合电路仿真常用模块Logic and Bit Operations子库中的Local Operator模块,将其拖到所建的untitled窗口中,然后鼠标左键双击该模块弹出的Block Parameters/Logical Operator对话框,按Operator栏后的黑三角来选择所需要的门电路标识符,如:AND、OR、NAND、NOR、XOR、NOT中的一个,并依次设置所需的输入、输出端子个数,之后按OK 键确定。利用这些基本门电路组成加法器逻辑电路。 四.课程设计的内容: 1、1位全加器的设计。 所谓全加器,就是带进位输入和进位输出的加法器。1位全加器有3个输入,分别是加 CMOS数字集成电路设计课程设计报告 学院:****** 专业:****** 班级:****** 姓名:Wang Ke qin 指导老师:****** 学号:****** 日期:2012-5-30 目录 一、设计要求 (1) 二、设计思路 (1) 三、电路设计与验证 (2) (一)1位全加器的电路设计与验证 (2) 1)原理图设计 (2) 2)生成符号图 (2) 3)建立测试激励源 (2) 4)测试电路 (3) 5)波形仿真 (4) (二)4位全加器的电路设计与验证 (4) 1)原理图设计 (4) 2)生成符号图 (5) 3)建立测试激励源 (5) 4)测试电路 (6) 5)波形仿真 (6) (三)8位全加器的电路设计与验证 (7) 1)原理图设计 (7) 2)生成符号图 (7) 3)测试激励源 (8) 4)测试电路 (8) 5)波形仿真 (9) 6)电路参数 (11) 四、版图设计与验证 (13) (一)1位全加器的版图设计与验证 (13) 1)1位全加器的版图设计 (13) 2)1位全加器的DRC规则验证 (14) 3)1位全加器的LVS验证 (14) 4)错误及解决办法 (14) (二)4位全加器的版图设计与验证 (15) 1)4位全加器的版图设计 (15) 2)4位全加器的DRC规则验证 (16) 3)4位全加器的LVS验证 (16) 4)错误及解决办法 (16) (三)8位全加器的版图设计与验证 (17) 1)8位全加器的版图设计 (17) 2)8位全加器的DRC规则验证 (17) 3)8位全加器的LVS验证 (18) 4)错误及解决办法 (18) 五、设计总结 (18) [转贴] 模拟集成电路设计的九个层次来源: 一篇好文章, 摘录于此,以示激励. 一段 你刚开始进入这行,对PMOS/NMOS/BJT什么的只不过有个大概的了解,各种器件的特性你也不太清楚,具体设计成什么样的电路你也没什么主意,你的电路图主要看国内杂志上的文章,或者按照教科书上现成的电路,你总觉得他们说得都有道理。你做的电路主要是小规模的模块,做点差分运放,或者带隙基准的仿真什么的你就计算着发文章,生怕到时候论文凑不够。总的来说,基本上看见运放还是发怵。你觉得spice 是一个非常难以使用而且古怪的东西。 二段 你开始知道什么叫电路设计,天天捧着本教科书在草稿纸上狂算一气。你也经常开始提起一些技术参数,Vdsat、lamda、early voltage、GWB、ft之类的。总觉得有时候电路和手算得差不多,有时候又觉得差别挺大。你也开始关心电压,温度和工艺的变化。例如低电压、低功耗系统什么的。或者是超高速高精度的什么东东,时不时也来上两句。你设计电路时开始计划着要去tape out,虽然tape out看起来还是挺遥远的。这个阶段中,你觉得spice很强大,但经常会因为AC仿真结果不对而大伤脑筋。 三段 你已经和PVT斗争了一段时间了,但总的来说基本上还是没有几次成功的设计经验。你觉得要设计出真正能用的电路真的很难,你急着想建立自己的信心,可你不知道该怎么办。你开始阅读一些JSSC或者博士论文什么的,可你觉得他们说的是一回事,真正的芯片或者又不是那么回事。你觉得Vdsat什么的指标实在不够精确,仿真器的缺省设置也不够满足你的要求,于是你试着仿真器调整参数,或者试着换一换仿真器,但是可它们给出的结果仍然是有时准有时不准。你上论坛,希望得到高手的指导。可他们也是语焉不详,说得东西有时对有时不对。这个阶段中,你觉得spice虽然很好,但是帮助手册写的太不清楚了。 四段 你有过比较重大的流片失败经历了。你知道要做好一个电路,需要精益求精,需要战战兢兢的仔细检查每一个细节。你发现在设计过程中有很多不曾设想过的问题,想要做好电路需要完整的把握每一个方面。于是你开始系统地重新学习在大学毕业时已经卖掉的课本。你把能能找到的相关资料都仔细的看了一边,希望能从中找到一些更有启发性的想法。你已经清楚地知道了你需要达到的电路指标和性能,你也知道了电路设计本质上是需要做很多合理的折中。可你搞不清这个“合理”是怎么确定的,不同指标之间的折中如何选择才好。你觉得要设计出一个适当的能够正常工作的电路真的太难了,你不相信在这个世界上有人可以做到他们宣称的那么好,因为聪明如你都觉得面对如此纷杂的选择束手无策,他们怎么可能做得到?这个阶段中,你觉得spice功能还是太有限了,而且经常对着"time step too small"的出错信息发呆,偶尔情况下你还会创造出巨大的仿真文件让所有人和电脑崩溃。 五段 你觉得很多竞争对手的东西不过如此而已。你开始有一套比较熟悉的设计方法。但是你不知道如何更加优化你手头的工具。你已经使用过一些别人编好的脚本语言,但经常碰到很多问题的时候不能想起来用awk 或者perl搞定。你开始大量的占用服务器的仿真时间,你相信经过大量的仿真,你可以清楚地把你设计的模块调整到合适的样子。有时候你觉得做电路设计简直是太无聊了,实在不行的话,你在考虑是不是该放弃了。这个阶段中,你觉得spice好是好,但是比起fast spice系列的仿真器来,还是差远了;你开始不相信AC仿真,取而代之的是大量的transient仿真。 六段 你开始明白在这个世界中只有最合适的设计,没有最好的设计。你开始有一套真正属于自己的设计方法,你会倾向于某一种或两种仿真工具,并能够熟练的使用他们评价你的设计。你开始在设计中考虑PVT的变化,你知道一个电路从开始到现在的演化过程,并能够针对不同的应用对他们进行裁减。你开始关注功耗加法器设计介绍

加法器电路设计全加器

加法器实验报告

实验一半加器的设计

加法器电路设计 全加器

微机原理加法器课程设计1

《模拟集成电路设计》复习

四位二进制加法器课程设计

八位二进制加法器课程设计

快速加法器的设计与应用

加法器课设

模拟集成电路复习

利用全加器电路创建四位二进制加法器

CMOS数字集成电路设计_八位加法器实验报告

模拟集成电路设计的九个层次