-课程设计二锁相环设计

引言

锁相环路(PLL)是一种能跟踪输入信号相位的闭环自动控制系统。它在无线电技术的各个领域得到了很广泛的应用。

最初,DeBellescize于1932年提出同步检波理论,首次公开发表了对锁相环路的描述,但并未引起普遍的重视。直至1947年,锁相环路才第一次应用于电视接收机水平和垂直扫描的同步。从此,锁相环路开始得到了应用。由于技术上的复杂性以及较高的成本,应用锁相环路的领域主要在航天方面,包括轨道卫星的测速定轨和深空探测等。性能要求较高的精密测量仪器和通信设备有时也用到它。到70年代,随着集成电路技术的发展,逐渐出现了集成的环路部件、通用单片集成锁相环路以及多种专用集成锁相环路,锁相环路逐渐变成了一个成本低、使用简便的多功能主件,这就为锁相技术在更广泛的领域应用提供了条件。至今,普遍应用锁相技术的主要有调制解调、频率合成、电视机彩色副载波提取、FM立体声解码等等。随着数字技术的发展,相应出现了各种数字锁相环路,它们在数字信号传输的载波同步、位同步、相位解调等方面发挥了重要的作用。

锁相环路所以能得到如此广泛的应用,是由其独特的优良性能所决定的。它具有载波跟踪特性,作为一个窄带跟踪滤波器,可提取淹没在噪声之中的信号;用高稳定的参考振荡器锁定,可作提供一系列频率高稳定的频率源;可进行高精度的相位与频率测量等等。它具有调制跟踪特性,可制成高性能的调制器解调器。它具有低门限特性,可大大改善模拟信号和数字信号的解调质量。

1 锁相环的基本知识

1.1 锁相环的原理

锁相环就是自动控制完成同步。能够实现两个电信号相位同步的自动控制系统叫做锁相环路,简称锁相环。锁相环是一个系统跟踪另一个系统的装置,更精确的说,就是一个系统中由振荡器产生的输出信号在频率和相位上与参考信号或输入信号同步。

当输入信号和环路的输出信号存在相位差的时,在锁相环控制机构的控制下,VCO 的输出信号和PD 的输入信号的相差减至最小。因此,在这个控制系统中,输出信号相位其实是锁定到参考信号或输入信号的相位上的。故此称为锁相环。

锁相环是一个行为自动跟踪系统因而当环路锁定时,不存在输入信号和输出信号的频率差,只存在如前所说的最小相位差。

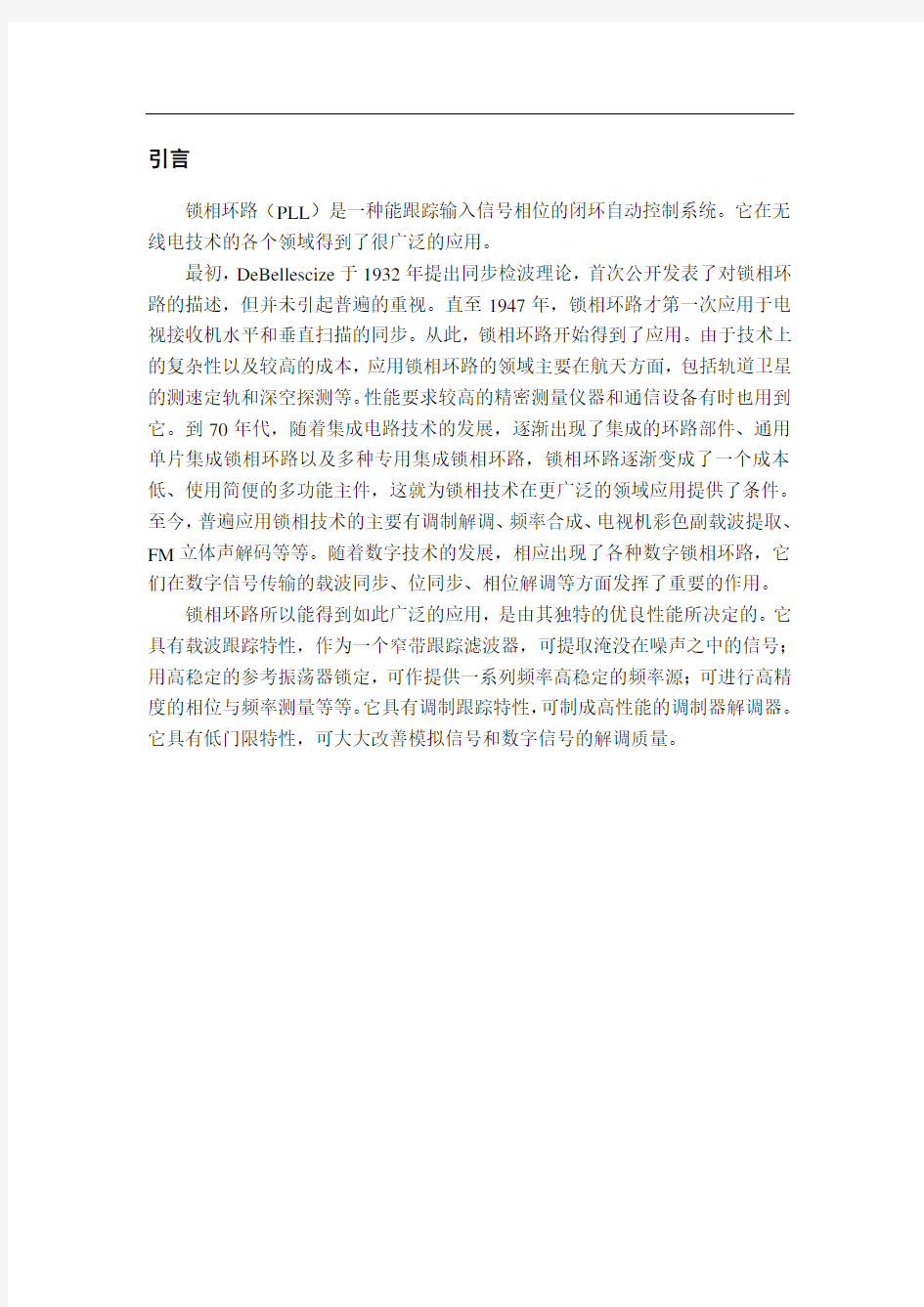

图1所示为最基本的锁相环(PLL )方框图。PLL 包括三个基本部件:鉴相器PD 、环路滤波器LF 、压控振荡器VCO 。

图 1-1

鉴相器是相对比较装置,他将输入信号2()t u 和参考信号1()t u 的相位进行比较,产生对应于两个信号的相位差e θ的误差电压()d t u 。环路滤波器的作用是滤除()d U t 中的高频成分和噪音,以保证环路的性能,增加环路的稳定性。压控振荡器受控制电压()e t u 的控制,使压控振荡器的频率向参考信号的频率靠近,也就是是差拍频率越来越低,直到消除频差而锁定。

不同类型的锁相环,性能差异较大。大多数锁相环系统使用VCO 很相似。LF 一般分为RC 积分滤波器、RC 比例积分滤波器和有源滤波器。LF 类型不同,环路特性也有差异。

1.1.1 鉴相器

PD 有线性和数字两种类型。线性为模拟比较型:数字型为逻辑电路,例如与异门鉴相器。

PD 是PLL 中很关键的一个部件,主要指标有:鉴相特性、鉴相增益d K 和工作频率及输出阻抗。

模拟鉴相器:PD 的鉴相器特有正弦型、三角形和锯齿形等等多种。PD 可以看做一个乘法器。假设鉴相器的输入信号和输出信号的顺势值是互为正交的正弦波信号,并且具有相同的频率1ω:

1111()sin()u t U w t θ=+

2212()cos()u t U w t θ=+

则PD 输出信号()d t u 为:

12121212112()()()[sin()sin(2)]2

m d m m K U U u t K u t u t K U U w t θθθθ==-+++ 式中:1U 、2U 分别为1()t u 和2()t u 的幅度;

1θ、2θ分别为1()t u 和2()t u 的初相位;

m K 为PD 自身的增益系数。

上式揭示了()d t u 是交流和直流成分的叠加。交流成分几乎完全被LF 滤掉,因此只考虑直流或者()d t u 的平均成分,上式变为:

12()sin()sin d d d e u t K K θθθ=-=

式中:d K 表示鉴相器的鉴相增益,单位为V/rad ;

12e θθθ=-表示两个信号的相位差。

对于在鉴相器中输出信号漏入输入信号的现象。泄露增加了LF 的负担,同时因为LF 滤除能力的限制,使得VCO 输出信号变成了输入的调制信号,降低了输出信号的频谱纯度、增大了输出信号的相位抖动。鉴相器的工作频率决定了锁相环能工作的最高输入频率。这种鉴相器可以在很低的频率下工作,同时,不采用变压器,输出电压较大,并且有良好的温度特性,应用十分广泛。

数字鉴相器:由数字电路组成的鉴相器叫数字鉴相器。主要由门电路和触发器构成。TTL 、CMOS 集成电路中的与门、与非门、或门、或非门、同或门、异或门、D 触发器以及RS 触发器等都可以直接用作数字鉴相器。单片PLL 集成电路CD4046中有2个数字鉴相器;异或门鉴相器PD1和边沿触发型鉴相器PD2。

PD1:异或门鉴相器。下图是异或门鉴相器的鉴相特性:

图 1-2

由图可见,异或门鉴相器具有三角形鉴相特性,其鉴相增益为

/d dm K V π=±

图1-3

PD2:触发式鉴相器。鉴相特性见下图:

图1-3

如图所示,用两个输入脉冲信号去触发一个触发器,触发器的输出脉宽代表了两个输入脉冲相位差的信息。触发器输出脉冲滤波后呈直流,直流大小就代表了两个脉冲的相位差。

1.1.2 环路滤波器

LF的作用如前所述,常见的LF有三种,其彻底函数以及频率特性如下:

1、RC积分滤波器

传递函数为:

1

()1/1

()

()1/1

c

d

V S SC

F s

V S R SC Sτ

===

++

式中:RC

τ=为滤波时间常数。

将s jω

=代人上式得到频率响应为:

1

1

()

()1

F jw

jwπ

=

+

2、无源比例滤波器

传递函数为:

22

2

1212

()1/1

()

()1/()1

c

d

V S R SC S

F S

V S R R SC S

τ

ττ

++

===

++++

式中:11R C

τ=

22

R C

τ=

频率响应为:

2

2

12

1

()

()1

jw

F jw

jw

τ

ττ

+

=

++

3、有源滤波器

传递函数为:

2321()(1)()()[(1)]1

c d V S A S F S V S S A τττ-+=

=+++ 式中:11R C τ=

22R C τ=

频率响应为:

2321(1)()[(1)]1A jw F jw jw A τττ-+=+++ 相比而言,有源滤波器有突出的优点:

(1) 对直流输入有A 倍放大;

(2) 当A>>1时,有源比例滤波器为理想环路滤波器。

1.1.3 压控振荡器

压控制振荡器(VCO ),是输出信号频率随输入控制电压变化的振荡器。

1、VCO 的技术要求

(1) 中心频率及频率变化范围

(2) 频率稳定度

(3) 相位噪声

(4) 压控线性度

(5) 压控灵敏度

控制压控频率的变化,通常可以:

(1) 改变振荡器的元件参数

(2) 改变振荡器的器件参数

(3) 改变定时元件的参数

2、VCO 的数学模型

VCO 是一个电压—频率变换装置。在环路中作为被控振荡器,它的振荡频率应随输入控制电压()c t u 线性变化,其变换关系为:

00()()r c w t w K u t =+

式中:()r t ω是受控后的瞬时角频率;

0K 为压控灵敏度。

下图示出了VCO 的控制特性曲线,实线为实际控制特性。可见,在以0ω 为中心的一个区域内,两者是吻合的。在分析环路时看作线性部件。在实用的压控振荡器的控制特性0K 中,大部分0K 为正值,但也有少数为负值,在使用

时一定要主要和PD 的特性合理匹配,否则无法构成相位负反馈系统。对VCO ,有:

20()()c d t K u t dt

θ= 2000()()()/t

c c t K u

d K u t P θττ==?

转化成S 域则有:

02()()c K u S s S

θ= 环路输出的相位实际上是输入控制电压对时间的积分,所以VCO 是一个理想的积分环节。其控制电压—输出频率(C o U ω-)特性曲线如下:

图1-4

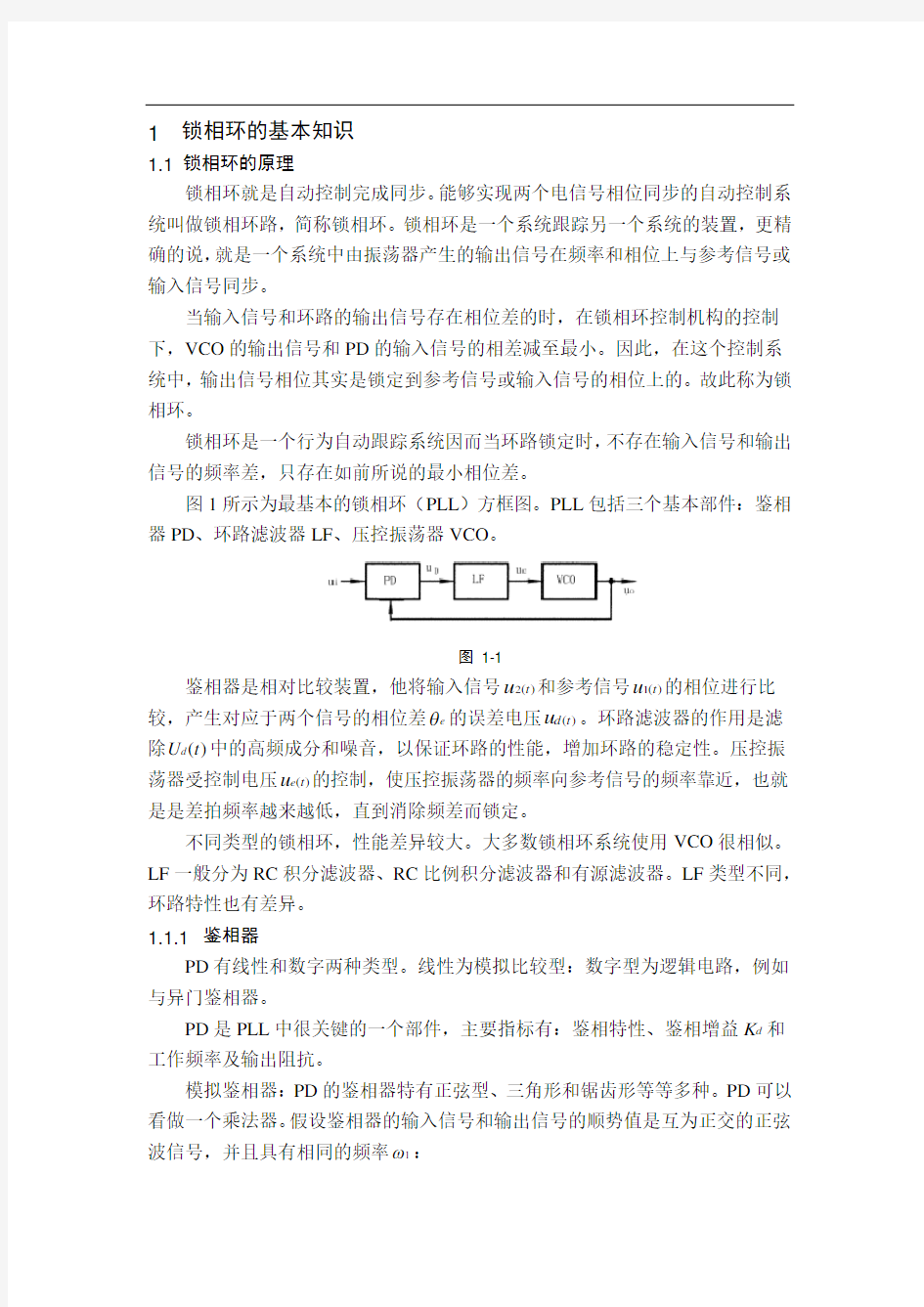

1.2 CD4046的工作原理

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS 锁相环集成电路,其特点是电源电压范围宽(为3V -18V ),输入阻抗高(约100M Ω),动态功耗小,在中心频率f0为10kHz 下功耗仅为600μW ,属微功耗器件。下图是CD4046的引脚排列,采用16脚双列直插式,各引脚功能如下:

图1-5

1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

图1-6是CD4046内部电原理框图,主要由相位比较Ⅰ、Ⅱ、压控振荡器(VCO)、线性放大器、源跟随器、整形电路等部分构成。

图1-6

比较器Ⅰ是一个或门,产生相位差信号(相位比较器1输出),并在压控振荡器的输出信号中心频率处保持90°相移不变。只要输入信号和比较信号(占空比都为50%)的相位差保持恒定,压控振荡器输出信号的中心频率就跟踪输入信号的频率,这也是锁相环锁相的本质。输入和输出信号的波形如图1-7所示。

UML课程设计-源代码

(object Petal version 47 _written "Rose 8.0.0303.1400" charSet 134) (object Design "Logical View" is_unit TRUE is_loaded TRUE attributes (list Attribute_Set (object Attribute tool "Java" name "IDE" value "Internal Editor") (object Attribute tool "Java" name "UserDefineTagName1" value "") (object Attribute tool "Java" name "UserDefineTagText1" value "") (object Attribute tool "Java" name "UserDefineTagApply1" value "") (object Attribute tool "Java" name "UserDefineTagName2" value "") (object Attribute tool "Java" name "UserDefineTagText2" value "") (object Attribute tool "Java" name "UserDefineTagApply2" value "") (object Attribute tool "Java" name "UserDefineTagName3" value "") (object Attribute tool "Java"

集成电路课程设计——锁相环CD4046设计频率合成器

集成电路课程设计——锁相环CD4046设计频率合成器

集 成 电 路 实 验 报 告 学号:110800316 姓名:苏毅坚指导老师:罗国新 2011年1月

锁相环CD4046设计频率合成器 实验目的:设计一个基于锁相环CD4046设计频率合成器 范围是10k~100K,步进为1K 设计和制作步骤: 确定电路形式,画出电路图。 计算电路元件参数并选取元件。 组装焊接电路。 调试并测量电路性能。 确定电路组成方案 原理框图如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N,从而就得到N倍参考频率的稳定输出。晶体振荡器输出的信号频率 f1,经固定分频后(M分频) 得到基准频率f1’,输入锁相环 的相位比较器(PC)。锁相环 的VCO输出信号 经可编程分频器(N分频)后输入到PC的另一端,这两个信号进行相位比较,当锁相环路锁定后得到: f1/M=f1’=f2/N 故f2=Nf’1 (f’1为基准频率) 当N变化时,就可以得到一系列的输出频率 f2。 设计方法 (一)、振荡源的设计 用CMOS与非门和1M晶体组成 1MHz振荡器,如图14。图中Rf 使 F1工作于线性放大区。晶体的等效 电感,C1、C2构成谐振回路。C1、 C2可利用器件的分布电容不另接。 F1、F2、F3使用CD4049。

(二)、N分频的设计 N分频采用CD40103进行分频。CD40103是BCD码8位分频器。采用8位拨码开关控制分频大小。输入的二进制大小即为分频器N分频。图中RP1为1K排阻 (三)、1KHZ标准信号源设计(即M分频的设计) 根据4518的输出波形图,可以看出4518包含二分频、四分频、十分频,用二片CD4518(共4个计数器)组成一个1000分频器,也就是三个十分频器,这样信号变为2Khz.再经过双D触发器,这样就可把2MHz的晶振信号变成500hz 的标准信号。如下图所示: (四) 4046锁相环的设计 锁相环4046为主芯片。电路图如下:500Hz 信号从14脚输入。 3脚4脚接N分频电路,即40103分频电路。13脚接低通滤波器。 锁相环参数设计 本设计中,M固定,N可变。基准频率f’1 定为1KHz,改变N值,使N=1~999,则可产生

基于PLC的六路抢答器系统设计

电气及自动化课程设计报告 题目:基于PLC的六路抢答器系统设计 课程:PLC原理与应用 学生姓名: 学生学号: 年级:14级 专业:自动化 班级:2班

指导教师: 机械与电气工程学院制 2017年6月 目录 1课程设计的任务和要求 (1) 1.1课程设计的任务 (1) 1.2课程设计的要求 (1) 2.PLC控制器的原理与组成 (1) 2.1PLC硬件系统 (1) 2.2PLC工作原理 (3) 2.3六人抢答器基本组成 (4) 2.4六人抢答器工作原理 (4) 3六人抢答器系统设计方案制定 (5) 3.1PLC选型 (5) 3.2六人抢答器系统的I/O口分配 (6) 4六人抢答器系统的软件设计 (7) 4.1PLC编程语言 (7) 4.2抢答器系统程序 (7)

4.2.1主持人控制端 (7) 4.2.2抢答成功与抢答犯规指示灯显示 (9) 4.2.3七段数码管显示 (9) 4.2.4蜂鸣器电路 (11) 5六人抢答器系统程序仿真 (12) 5.1抢答成功仿真 (12) 5.2抢答犯规及抢答超时仿真 (12) 5.3加减分及数码管显示 (13) 5.4抢答超时 (14) 6总结及心得体会 (14) 参考文献 (15)

基于PLC的六路抢答器系统设计 机械与电气工程学院自动化专业 1课程设计的任务和要求 1.1课程设计的任务 使用西门子S7-200PLC编写程序实现六路抢答器的系统设计并使用仿真软件进行其功能的实现。 1.2课程设计的要求 (1)主持人控制功能,具有开始抢答按钮和复位按钮; (2)主持人未按下开始抢答按钮时抢答为违规抢答,违规指示灯亮,蜂鸣器响; (3)抢答延时,超过20S无人抢答时此题作废,蜂鸣器长鸣; (4)抢答成功后,抢答成功指示灯亮,数码管显示抢答成功的队伍编号; (5)在抢答成功后,主持人根据回答的正确与否可以对该队伍进行加减分控制; (6)每次正确抢答时,只有第一位按下抢答按钮的队伍为有效抢答。 2.PLC控制器的原理与组成 2.1PLC硬件系统 可编程控制器,英文称ProgrammableLogicController,简称PLC。PLC是基于电子计算机,且适用于工业现场工作的电控制器。它源于继电控制装置,但它不像继电装置那样,通过电路的物理过程实现控制,而主要靠运行存储于PLC内存中的程序,进行入出信息变换实现控制。PLC基于电子计算机,但并不等同于普通计算机。普遍计算机进行入出信息变换,多只考虑信息本身,信息的入出,只要人机界面好就可以了。而PLC则还要考虑信息入出的可靠性、实时性,以及信息的使用等问题。特别要考虑怎么适应于工业环境,如便于安装,抗干扰等问题[1]。

三路抢答器设计

数字电路课程设计 一、设计任务和要求: 1. 抢答器同时供3名选手抢答,分别用3个按钮D1、D2、D3表示。 2. 设置一个系统清除和抢答控制开关S,该开关由主持人控制。 3. 抢答器具有锁存与显示功能。即选手按动按钮,锁存相应的编号,并在LED数 码管上显示,选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人 将系统清除为止。 4. 抢答器具有定时抢答功能,且一次抢答的时间为8秒。当主持人启动"开始"键后, 定时器进行计时(0-7)。 5.主持人没有闭合开关之前,有人抢答,数码管显示对应的选手编号,且红灯亮,当 所有选手闭合自己对应的开关时,编号数码管清为0。 6. 参赛选手在设定的时间内进行抢答,抢答有效,计数器停止工作,显示器上显示 选手的编号和抢答的时间,绿灯亮,并保持到主持人将系统清除为止。 7. 如果定时时间已到,无人抢答,本次抢答无效,定时显示器上显示8,且黄灯亮以 示警告时间已到,若有人抢答,显示抢答人组号并锁存,直到主持人将系统清零, 即黄灯灭,两个数码管显示都为0。

二、 实验框图: 1、设计方案 : 抢答器具有锁存、定时、显示功能。抢答之前,两个数码管显示为0,即主持人没有按下开始按钮之前,有人抢答,亮红灯给以警告,数码管显示对应的选手编号,当选手闭合自己的开关时,对应数码管显示为0;当主持人按下开始按钮后,进行抢答,若有人抢答,锁存器锁存选手号和抢答时的时间,同时亮绿灯,直到主持人清零,系统才能再次正常工作;如果时间已到,没有人回答,黄灯亮,即在8秒的时刻,如果有选手抢答,锁存器锁存选手号,数码管并将选手号显示出来,直到主持人清零。 2、系统框图 : 当主持人宣布开始,定时电路开始秒脉冲电路的作用而进行计时,并通过译码器在数码管中显示。当某选手按开关键时,通过控制电路控制锁存器的使能端,并在锁存器中锁存,在输出端产生相应的开关电平信息,然后在译码器中译码,将编码器输出的8421BCD 转换为数码管需要的逻辑状态。最后在显示电路中显示出所按键选手的号码。 161全加器 抢答按钮 75锁存器 48译码器 显示译码 555秒脉冲产生器器 48译码器 显示译码 控制电路 主持人开关 报警灯

基于锁相环的FM发射机设计(高频电子线路课程设计)(附程序)

通信线路课程设计报告 基于锁相环的FM发射机设计与总结报告 学院计算机与电子信息学院 专业 班级 小组成员

摘要 本设计利用基于晶体管设计的科皮斯振荡器,通过控制电压达到控制FM和PLL,最大限度的实现了调频(FM)发射机的功能。该发射机的发射功率为500mW,可调频率在88~108MHz之间,传输距离在200米左右。通过本课程设计,达到了学习高频电子线路的目的。 Abstract The design of Kepi Si-based transistor oscillator design, by controlling the voltage to control the FM and PLL, maximum to achieve the FM transmitter function. The transmitter's transmission power is 500mW, adjustable between 88 ~ 108MHz frequency, transmission distance of 200 meters. Through the curriculum design to achieve the purpose of studying high-frequency electronic circuits.

一、整体方案论证 本设计使用基于晶体管T1设计的Colpitts振荡器。这是一种通过控制电压从而达到控制FM和PLL控制的方案。为了获得良好的工作效果,T1晶体管本应该为HF晶体管。但是在本例中,我选用了既便宜又通用的BC817晶体管。该振荡器需要利用LC震荡电路来达到良好的谐振效果。在本例中,LC振荡电路由C1、C2、C2、L1以及变容二极管BB139组成。由图可见电感线圈平行于由C1、C2串联组成的电路,变容二极管和C3有相同的组成方法。图中易知,C3的值决定了VCO的调节范围,即C3的值越大,VCO 的电压调节范围也就越大。由于变容二极管的容量受到加在它两边的电压的控制,因此她的容积收到电压变化的影响。因此,电压的变化将直接决定震荡频率的变化。

六路抢答器论文

六路数字抢答器设计方法 王亚静 摘要:有许多比赛活动中为了准确、公正、直观的判断出第一抢答者,通常设置一台抢答器,通过灯光等手段指示出第一抢答者。同时,还可以设置记分、犯规及奖惩记录等多种功能。电路具有第一抢答信号的鉴别和锁存功能。在主持人将系统复位并发出抢答指令后,开始抢答,如有参赛者按抢答开关,则该组指示灯亮显示出抢答者的组别。此时,电路应具备自锁功能,使其他组的抢答开关不起作用。 关键词:第一抢答者 抢答器 锁存 复位 自锁功能 一.设计任务与技术要求 1、设计任务 设计制作一个可供6组选手参加比赛的数字式竞赛抢答器。 2、技术要求 (1) 抢答器同时供6名选手或6个代表队比赛,分别用6个按钮S1、S2、S3、S4、S5、S6表示。 (2) 设置一个系统清除和抢答控制开关S0,该开关由主持人控制。 (3)抢答器具有锁存与显示功能。即具有第一个抢答信号的鉴别和数据锁存的功能。抢答开始后,若选手按动抢答按钮,锁存相应编号,相应灯亮起,并封锁输入编码电路,禁止其他选手抢答。抢答选手的编号一直保持到主持人将系统清零为止。 二.总体方案设计及电路的工作原理: 1. 总体方案 数字式抢答器原理框图如图1所示。它由主体电路组成。主体电路完成基本的抢答功能,即开始抢答后,当选手按动抢答键时,能亮起相应灯泡同时横封锁输入电路,禁止其他选手抢答。

图1 2.工作原理 工作原理为:接通电源后,主持人将开关拨到"清零"状态,抢答器处于禁止状态,编号二极管灭灯;主持人将开关置“开始”状态,宣布"开始"抢答器工作。选手抢答时,抢答器完成:优先判断、编号锁存、二极管发光显示。如果再次抢答必须由主持人再次操作"清除"和"开始"状态开关。计数输入由秒脉冲发生器提供。 三.单元电路的设计及电路图 1.抢答电路 抢答电路的功能有两个:一是能分辨出选手按键的先后,并锁存优先抢答者的编号,供显示电路用;二是要使其他选手的按键操作无效。这里选用6D触发器74LS174,其电路图如图2所示。 图2 其工作原理是: 当开关S置于"开始"时,抢答器处于等待工作状态,当有选手将键按下时(如按下S1),74LS174的输出Q1=1,二极管D1发光。此外,Q1=1,经非门过74HC30输出为高电平,74LS174处于禁止状态,封锁其他按键的输入,保证了抢答者的优先性。如有再次抢答需由主持人将 S0开关重新置“清零”, 6D触发器74LS174的CLR端为低电平,输出端(Q1~Q6)全部为低电平,于是二极管灭灯;然后再进行下一轮抢答。 2.反馈电路 这部分电路是用8与非门74HC30和6个非门构成,电路图如图3.

三路抢答器课程设计

设计题目 三路抢答器的PLC控制 1 主要内容 该抢答器作为智力竞赛的品判装置,根据应答者抢答情况自动设定答题时间,并根据答题情况用灯光、声音显示其答题正确、错误及违规,在主持人的操作下,对答题者所显示的分数值进行加分、减分或违规扣分。 2 具体要求 1.主持人提出问题按下启动按钮(开始抢答)后,若10s内无人抢答,则有声音提示,说明该题无人抢答,自动作废。 2.主持人提出问题在未按下启动按钮(开始抢答)之前抢答,则违规,抢答器报出违规信号,并作减分处理。 3.主持人提出问题按下启动按钮(开始抢答)后,第一个按下按钮的信号有效,后按下的按钮信号无效。 4.主持人按下计时按钮,开始计时。答题时间为1min,答题过程中有灯光提示时间,时间到并有声音指示。 5.抢答器有数码显示器显示各答题者的分数,由主持人控制,答对者加10分,答错者减10分,违规者扣5分,减分计算中若出现负分作0分处理。 6.答题完毕按下复位按钮,恢复抢答器原始状态,为下一轮抢答做好准备。 答题过程中灯光、音响的安排及注意事项见课程设计指导书。 在上述具体的要求下,完成硬件电路的制作和接线,PLC控制程序的设计及联机调试,直至满足要求。 3 进度安排

1.理解课程设计内容及设计要求,查阅资料(第一周的星期一)。 2. PLC外围硬件电路的制作和接线,构思设计方案(第一周的星期二至星期三)。 3. PLC控制程序设计、程序调试及系统的总体调试,撰写课程设计报告(第一周的星期四至第二周星期四)。 4. 课程设计答辩、批改设计报告,登载成绩(第二周星期五)。 4 完成后应上交的材料 PLC外围硬件连接电路、程序清单及课程设计总结报告。 6 总评成绩 指导教师签名日期年月日系主任审核日期年月日 目录 绪论 (3) 第一章系统设计内容及要求 (1) 第二章硬件设计 (3) 2.1硬件选取 (3) 2.1.1 三菱PLC可编程控制器 (3) 2.1.2 按钮板块 (3)

5_Java课程设计源代码

package zhouchuan; import java.applet.*; import java.awt.*; import java.awt.event.*; import https://www.360docs.net/doc/bb8706676.html,.*; public class zhouchuan extends Applet implements ActionListener { AudioClip clip; Button buttonPlay, buttonLoop, buttonStop; public void init(){ try{ URL url=new URL("file:"+"F://ding.wav"); clip=getAudioClip(url);}catch(Exception e){ } buttonPlay=new Button("开始播放"); buttonLoop=new Button("循环播放"); buttonStop=new Button("停止播放"); buttonPlay.addActionListener(this); buttonStop.addActionListener(this); buttonLoop.addActionListener(this); add(buttonPlay); add(buttonLoop); add(buttonStop); } public void stop(){ clip.stop(); } public void actionPerformed(ActionEvent e){ if(e.getSource()==buttonPlay) clip.play(); else if(e.getSource()==buttonLoop) clip.loop();

集成电路锁相环设计报告

锁相环CD4046设计频率合成器 ------集成电路考试实验设计报告 学校:福州大学 学院:物理与信息工程学院 班级:09级信息工程类2班 姓名:吴志强学号:110900636 姓名:吴鑫学号:110900635

目录 一、设计和制作任务 (3) 二、主要技术指标 (3) 三、确定电路组成方案 (3) 四、设计方法 (3) (一)、振荡源的设计 (3) (二)、N分频的设计 (3) (三)、10HZ标准信号源设计(即M分频的设计) (5) 五、锁相环参数设计 (6) 六、调试步骤 (6) 七、参考文献 (7) 附录:各芯片的管脚图 (7)

锁相环CD4046设计频率合成器 一、设计和制作任务 1.确定电路形式,画出电路图。 2.计算电路元件参数并选取元件。 3.组装焊接电路。 4.调试并测量电路性能。 5.写出课程设计报告书 二、主要技术指标 1.频率步进 10Hz 2.频率范围:1kHz—10kHz 3.电源电压 Vcc=5V 三、确定电路组成方案 原理框图如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N,从而就得到N倍参考频率的稳定输出。 晶体振荡器输出的信号频率f1, 经固定分频后(M分频)得到 基准频率f1’,输入锁相环的相 位比较器(PC)。锁相环的VCO 输出信号经可编程分频器(N分频) 后输入到PC的另一端,这两个信号进行相位比较,当锁相环路锁定后得到:f1/M=f1’=f2/N 故f2=Nf’1 (f’1为基准频率) 当N变化时,或者N/M变化时,就可以得到一系列的输出频率f2。 四、设计方法 (一)、振荡源的设计 用CMOS与非门和1M晶体组成 1MHz振荡器,如图14。图中Rf 使 F1工作于线性放大区。晶体的等效 电感,C1、C2构成谐振回路。C1、 C2可利用器件的分布电容不另接。 F1、F2、F3使用CD4049。 (二)、N分频的设计 用三片4522组成1——10kHZ频率合成器 CD1522的二一十进制1/N减计数器。其引脚见附录。其中D1-D4是预置端,Q1

基于PLC的六路抢答器系统设计课程设计

课程设计说明书

题目: 基于 PLC 的六路抢答器系统设计

毕业设计(论文)原创性声明和使用授权说明

原创性声明

本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教

师的指导下进行的研究工作及取得的成果。尽我所知,除文中特别加

以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研

究成果,也不包含我为获得

及其它教育机构的学位或学历

而使用过的材料。对本研究提供过帮助和做出过贡献的个人或集体,

均已在文中作了明确的说明并表示了谢意。

作 者 签 名:

日 期:

指导教师签名:

日 期:

使用授权说明

本人完全了解

大学关于收集、保存、使用毕业设计(论

文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电

子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供

目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制

手段保存论文;在不以赢利为目的前提下,学校可以公布论文的部分

或全部内容。

作者签名:

日 期:

学位论文原创性声明

本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研 究所取得的研究成果。除了文中特别加以标注引用的内容外,本论文 不包含任何其他个人或集体已经发表或撰写的成果作品。对本文的研 究做出重要贡献的个人和集体,均已在文中以明确方式标明。本人完 全意识到本声明的法律后果由本人承担。

作者签名:

日期: 年 月 日

学位论文版权使用授权书

本学位论文作者完全了解学校有关保留、使用学位论文的规定,

同意学校保留并向国家有关部门或机构送交论文的复印件和电子版,

允许论文被查阅和借阅。本人授权

大学可以将本学位

论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩

印或扫描等复制手段保存和汇编本学位论文。

涉密论文按学校规定处理。

作者签名: 导师签名:

日期: 年 月 日 日期: 年 月 日

8路抢答器的设计报告(数字电路课程设计)资料

《数字电子技术》课程设计报告 8路智力抢答器 设计与制作 设计要求: 1、可同时供8名选手或8个代表队参加比赛; 2、主持人控制系统的清零(编号显示数码管灭灯)和抢答 的开始; 3、抢答器具有数据锁存和显示的功能; 4、抢答器具有定时抢答的功能,且一次抢答的时间可以由 主持人设定; 5、具有报警功能。 成绩:评阅人: XX科技学院理学院

8路智力抢答器 设计与制作 8路智力抢答器是一种用数字电路技术实现由主持人控制、定时抢答、报警功能的装置。他是在规定的时间内进行抢答。一旦有人抢答,显示器上会同时显示抢答时间和抢答选手号码。当超出规定时间时,即使抢答,不会显示选手号码。 8路智力抢答器包括组合逻辑电路和时序电路。通过此次设计与制作,进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法.且由于8路智力抢答器包括组合逻辑电路和时叙电路.通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法。 一、设计要求 (一)设计指标 1、计一个智力竞赛抢答器,可同时供8名选手或8个代表队参加比赛,他们的编号分别是0、1、 2、 3、 4、 5、 6、7,各用一个抢答按钮,按钮的编号与选手的编号相对应,分别是S0——S7。 2、给节目主持人设置一个控制开关,用来控制系统的清零(编号显示数码管灭灯)和抢答的开始。 3、抢答器具有数据锁存和显示的功能。抢答开始后,若有选手按动抢答按钮,编号立即锁存,并在LED数码管行显示出选手的编号,

同时扬声器给出音响提示。此外,要封锁输入电路,禁止其他选手抢答。优先抢答选手的编号一直保持到主持人将系统清零为止。 4、抢答器具有定时抢答的功能,且一次抢答的时间可以由主持人设定(如30s)。当节目主持人启动“开始”键后,要求定时器立即减计时,并用显示器显示,同时扬声器发出短暂的声响。 5、参赛选手在设定的时间内抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答时刻的时间,并保持到主持人将系统清零为止。 6、如果定时抢答的时间已到,却没有选手抢答时,本次抢答无效,系统短暂报警,并封锁输入电路,禁止选手超时后抢答,时间显示器上显示00。 (二)设计要求 1、画出电路原理图(或仿真电路图); 2、元器件及参数选择; 3、电路仿真与调试; (三)制作要求自行装配和调试,并能发现问题和解决问题。 (四)编写设计报告写出设计与制作的全过程,附上有关资料和图纸,有心得体会。 二、原理框图 抢答器系统原理框图如下所示。它由主体电路和扩展电路两部分组成,主体电路完成基本抢答后,选手按动抢答键时,能显示选手的编号,同时能封锁输入电路,禁止其他选手抢答,扩展电路完成定时

数据库课程设计源代码

use kjq111007307 /*创建一个部门信息表 包含“部门号,部门名,部门经理,人数”属性列*/ create table department (depart_no char(2)primary key, depart_name char(30)not null, depart_manage char(6)not null, depart_people int not null ) /*创建一个职位信息表 包含“职位,基本薪资,福利,失业保险,住房公积金”属性列*/ create table position (pos char(30)primary key, basesalary float not null, benefits float not null, insurances float not null, housing_funds float not null ) /*创建一个职工信息表 包含"职工号,职工名,性别,年龄,学历,部门号,职位"属性列*/ create table staff_message (staff_no char(4)primary key, staff_name char(10)not null, staff_sex char(2)check(staff_sex in('男','女')), staff_age int not null, staff_edu char(10)not null, staff_dep char(2)not null, staff_job char(30)not null, foreign key(staff_dep)references department(depart_no), foreign key(staff_job)references position(pos) ) /*创建一个员工考勤表 包含“职工号,年月,迟到,缺勤,加班”属性列*/ create table staff_days (staff_no char(4), month_date char(6), staff_late int not null, staff_absent int not null, workoverdays int not null, primary key(staff_no,month_date) ) /*创建一个薪资表 包含“职工号,年月,奖金,罚金,真实薪资”属性列*/ create table salary (staff_no char(4),

《PLC课程设计》(---九路抢答器)指导书

广东工贸职业技术学院 2010~2011学年第二学期 PLC课程设计指导书 题目:九路抢答(PLC可编程控制器应用) 课程名称《PLC及组态课程设计》专业电子信息适用年级 09级 班级 09电信班1、2 指导教师 _侯益坤、伍勤谟 · 一、课程设计的目的 PLC的课程设计是在完成本课程内容的课堂教学和实践之后进行的。目的是通过对一个实际应用课题的设计,初步掌握PLC控制系统的设计方法,从了解设计要求,运用所学知识并查阅有关技术资料进行系统设计,到模拟安装调试,然后整理有关技术资料,编写设计说明书,使学生得到一次系统的训练,从而对本课程理解更深刻,更清楚,更重要的是提高应用理论知识解决实际问题的能力。 课程设计应以培养学生的能力为主,要求学生在独立完成设计任务的同时,注意多方面能力的培养和提高,主要包括以下几方面: (1)综合运用专业及基础知识解决实际工程技术的能力。 (2)独立工作的能力和创造能力。 — (3)查阅技术资料和各种工具书的能力。 (4)工程绘图能力。

(5)撰写技术报告和编制技术资料的能力。 因此,在课程设计教学中,应以学生为主体,让其充分发挥自主性和创造性。教师的作用主要体现在工作方法的指导和思维方法的引导,以及设计技术把关上面。 二、系统方案设计要求说明 在很多竞赛活动中,经常用到抢答器。对抢答器的控制要求是:当多个输入信号输入时,抢答器只接收第一个到来的信号,而不接收后面到来的输入信号并使第一个到来的输入信号相应的灯或铃有反应。 本系统中设有9个抢答输入按钮、一个复位按钮、一个开始按钮,一个七段数码管,一个蜂鸣器,一个3S兰灯,一个5S黄灯,一个红色违规指示灯。 】 本系统可提供九个抢答台,在主持人的主持下,参赛人通过抢先按下按钮回答问题。 在抢答开始前,主持人应按下复位按钮使系统复位,做好抢答准备。 当主持人说开始,并同时按下开始按钮,抢答开始,并限定抢答时间为10s。 若抢答者在抢答开始前抢先输入,则属违规要显示该台台号,同时蜂鸣器以秒的周期响, 红色违规指示以1秒的周期闪烁,以便扣分惩罚。 若在开始之后到3s之内第一个按下抢答输入,由七段显示器显示该台台号,同时3s兰灯点亮、蜂鸣器声以秒的周期响。以便答对之后给予基本加分和对应兰灯点亮额外奖励加分。 若在3s之后到5s之内第一个按下抢答输入,由七段显示器显示该台台号,同时5s黄灯点亮、蜂鸣器声以秒的周期响。以便答对之后给予基本加分和对应黄灯点亮额外奖励加分。 若在5s之后10s之内第一个按下抢答输入,由七段显示器显示该台台号,蜂鸣器声以秒的周期响。以便答对给予基本加分

三路抢答器的设计与仿真

《基础强化训练》报告书 题目:三路抢答器 专业班级:电子0903 学生姓名: 指导教师: 武汉理工大学信息工程学院 2011 年7 月8 日

基础强化训练任务书 学生姓名:专业班级: 指导教师:工作单位:武汉理工大学 题目:三路抢答器的PCB板设计 一、训练目的 主要目的就是对学生进行基础课程、基本技能、基本动手能力的强化训练,提高学生的基础理论知识、基本动手能力,提高人才培养的基本素质。 二、训练内容和要求 1、基础课程和基本技能强化训练 (1)设计一个三路抢答器电路; (2)对所设计电路的基本原理进行分析; 2、文献检索与利用、论文撰写规范强化训练 要求学生掌握基本的文献检索方法,科学查找和利用文献资料,同时要求学生获得正确地撰写论文的基本能力,其中包括基本格式、基本排版技巧和文献参考资料的写法、公式编排、图表规范制作、中英文摘要的写法等训练。 3、基本动手能力和知识应用能力强化训练 (1)学习PROTEL软件; (2)绘制电路的原理图和PCB版图,要求图纸绘制清晰、布线合理、符合绘图规范; 4、查阅至少5篇参考文献,按《武汉理工大学课程设计工作规范》要求撰写基础强化训练报告书,全文用A4纸打印。 三、初始条件 计算机;Microsoft Office Word 软件;PROTEL软件 四、时间安排 1、2011年7 月11日集中,作基础强化训练具体实施计划与报告格式要求的说明; 学生查阅相关资料,学习电路的工作原理。 2、2011 年7 月11 日,电路设计与分析。 3、2011 年7 月12日至2011 年7 月14日,相关电路原理图和PCB版图的绘制。 4、2011年7 月15日上交基础强化训练成果及报告,进行答辩。 指导教师签名:年月日系主任(或责任教师)签名:年月日

教师课程管理系统(c++课程设计源代码)

#include

声音传输系统的设计——课程设计

电子技术课程设计说明书 题目:声音传输系统 学生姓名:陈君 学号: 200906040215 院(系):电气与信息工程学院 专业:测控技术与仪器 指导教师:戴庆瑜 2011 年 11 月18日

目录 1 选题背景................................................................................................................................ 1.1 指导思想 (1) 1.2 方案论证 (1) 1.3 基本设计任务 (1) 1.4 发挥设计任务 (1) 1.5电路特点 (2) 2 电路设计................................................................................................................................ 2.1 总体方框图 (3) 2.2 工作原理 (3) 3 各主要电路及部件工作原理................................................................................................ 3.1 555构成多谐振荡器简要说明 (4) 3. 2音频功率放大器LM386简要说明 (4) 3.3LM567简要说明 (5) 4 原理总图 (6) 5 元器件清单 (6) 6 调试过程及测试数据............................................................................................................ 6.1 通电前检查 (7) 6.2 通电检查 (7) 6.2.1电源的检查 (7) 6.2.2 555输出电路调试 (7) 6.2.3 LM386的调试 (7) 6.2.4 LM567的调试 (7) 6.3 结果分析 (7) 7 小结 (7) 8 设计体会及今后的改进意见 (11) 8.1 体会 (7) 8.2 本方案特点及存在的问题 (8) 8.3 改进意见 (8) 参考文献 (8)

六路抢答器设计报告

六路数字抢答器设计报告 目录 一、任务设计和要求 (2) 二、设计方案与论证 (4) 三、电路设计计算与分析 (5) 3.1 主持人控制电路 (5) 3.2 10S倒计时电路 (7) 3.3 控制显示电路 (10) 3.4 主要元器件介绍 (12) 四、总结与心得 (18) 五、附录 (19) 附录一:元器件清单 (19) 附录二:六路抢答器原理图 (20) 附录三:六路抢答器的仿真 (21) 六、参考文献 (22) 1

一、设计任务和要求 六路数字抢答器的设计任务如下: 1.主持人按动启动按钮,抢答开始,同时开始10秒倒计时。 2.6名抢答选手编号分别为1-6,各自控制一个按钮进行抢答,有人按下时扬声器给出声音提示,倒计时电路停止计时,同时显示抢答选手的号码。 3.选用七段LED作为显示器。 4.完成电路的理论设计。 5.参数的计算和有关器件的选择。 6. 对电路进行仿真。 7.撰写设计报告书一份:A3图纸1张。报告书要求写明以下内容:(B5纸) (1)总体方案的选择和设计 (2)各个单元电路的选择和设计 (3)仿真过程的实现 课程设计要求如下: 课程设计大体可分成以下三个阶段: 1.设计与计算阶段 学生根据课程设计任务、要求和条件进行总体方案的设计,通过论证和选择,确定总体方案。此后是对方案中单元电路 2

进行选择和设计计算,包括元器件的选用和电路参数的计算。最后画出总体电路图,选用元件一览表。 2.计算机仿真及电路制版 运用仿真软件EWB或MULTISIM对设计电路进行仿真,排除电路故障、调整元器件参数、修改电路,使之达到设计指标要求。最后使用PROTEL软件完成对电路的PCB制版(选作)。 3.撰写设计报告阶段 设计报告是学生对课程设计全过程的系统总结。学生应按规定的格式撰写设计报告。设计报告的主要内容有: 1)课题名称。 2)设计任务和要求。 3)方案选择与论证。 4)原理框图,总体电路图、计算机电路仿真图,以及它们的说明;单元电路设计与计算说明;元器件选择和电路参数计算的说明等。 5)收获体会、存在问题和进一步的改进意见等。 3

课程设计三路抢答器

三人抢答计时器 一、摘要 智力竞赛抢答计时器是一名公正的裁判员,它的任务是从若干名参赛者中确定出最先的抢答者,并要求参赛者在规定的时间里回答完问题。 二、设计要求 1.设计一个三人参加的智力竞赛抢答计时器。 2.当有某一参赛者首先按下抢答开关时,相应显示灯亮并伴有声响。此时,抢答器不再接收其他输入的信号。 3.电路具有回答问题时间控制功能。要求回答问题的时间小于等于100秒(显示0~99),时间显示采用倒计时方式。当达到限定时间时,发出声响以示警告。 三、给定条件及元器件 1.要求电路主要选用中规模CMOS集成电路CC 4000 系列。 2.电源电压为5 ~ 10 V 。 3.本设计要求在数字电路实验箱上完成。 四、设计内容 1.电路各部分的组成和工作原理。 2.元件器的选取及其电路图和功能。 3.电路各部分的调试方法。 4.在整机电路的设计调试过程中,遇到什么问,其原因及解决的办法。 五、电路组成和工作原理

图(一) 根据上面所说的功能要求,智力竞赛抢答计时系统的组成框如图(一)所示。 它主要由六部分组成; 1、抢答器——是三人抢答计时器的核心。当参赛者的任意一位首先按下抢答开关时,抢答器即刻接受该信号,指使相应发光二级管亮(或音响电路发出声音),与此同时,封锁住其他参赛者的输入信号。 2、抢答控制电路——由三个开关组成。三名参赛者各控制一个,拨动开关使相应控制端的信号为高电平或低电平。 3、清零装置——供比赛开始前裁判员使用。它能保证比赛前触发器统一清零,避免电路的误动作和抢答过程的不公平。 4、显示声响电路——比赛开始,当某一参赛者按下抢答器开关时,触发器接受该信号,在封锁其他开关信号的同时,使该路的发光二极管发出亮光和蜂鸣器发出声响,以引起人们的注意。 5、计时显示声响电路——是对抢答者回答问题时间进行控制的电路。若规定回答问题时间小于等于100秒(显示为0—99),那么显示装置应该是一个二位数字显示的计数系统。 6、振荡电路——它应该提供给抢答器,计时系统和声响电路工作的控制脉冲。

c语言课程设计源代码

c语言课程设计源代码标准化管理处编码[BBX968T-XBB8968-NNJ668-MM9N]

学校运动会管理系统问题描述: (1) 初始化输入:N-参赛院系总数,M-男子竞赛项目数,W-女子竞赛项目数; (2) 各项目名次取法有如下几种: 取前5名:第1名得分 7,第2名得分 5,第3名得分3,第4名得分2,第5名得分 1; (3) 由程序提醒用户填写比赛结果,输入各项目获奖运动员的信息。 (4) 所有信息记录完毕后,用户可以查询各个院系或个人的比赛成绩,生成团体总分报表,查看参赛院系信息、获奖运动员、比赛项目信息等。 程序代码: #include<> #include<> #define N 3 #define M 3 #define W 3 char* n_number[3]={"1","院系2","院系3"}; char* m_number[3]={"1","男项2","男项3"};

char* w_number[3]={"女项1","女项2","女项3"}; int size=2; struct student { char num[10]; char name[20]; char xiangmu[20]; int score; char ximing[20]; }stu[100],temp; void input() um,&stu[i].name,&stu[i].xiangmu,&stu[i].score,&stu[i].ximing); iming,n_number[0])==0) iming); iming,n_number[h])==0) for(int s=0;s 西华大学课程设计说明书现代测试课程设计正文(高速数字锁相环路设计)

前 言

锁相环路(PLL)是一个相位误差控制系统,是将输入信号(参考信号)和输出信号之间 的相位进行比较,产生相位误差电压来调整输出信号的相位,使输出信号频率与参考信号频 率相同。 信号锁相技术广泛应用于自动化控制等领域。利用该技术可以产生同步于被锁输入信号 的整数倍频或者分数倍频的输出控制信号。锁相环的基本结构是由鉴相、环路滤波、可控振 荡器和 M 倍分频等模块组成的一个反馈环路。输入的被锁信号首先与同步倍频信号经过 M 倍 分频后产生的锁相信号进行鉴相处理,输出相位误差信号。环路滤波模块通常具有低通特性, 它将相位误差信号转化为稳定的控制信号,从而控制可控振荡器模块,产生稳定的频率信号 输出。这个频率信号就是所需的同步倍频信号。如果整个反馈环路锁相稳定,锁相环输出的 同步倍频信号的频率就是其输入的被锁信号频率的 M 倍。假如被锁信号在输入鉴相模块之前 又先被分频了 L 倍,则锁相获得的同步倍频信号的频率就是被锁信号频率的 M/L 倍。 锁相环路的应用十分广泛。在稳频技术中的应用,如:锁相倍频器,锁相分频器,锁相 混频器,锁相合成器等;在调制解调技术中的应用,如:锁相调频和鉴频,同步检波等。除 了以上所介绍的锁相环路的应用外,它还应用于空间技术(例如,由于各种原因使地面接收 的空间信号十分微弱,采用锁相接收机可使接收机接收微弱空间信号的能力大大加强)等方 面。由于锁相环路易集成化,锁相环路已成为继集成运放之后,又一个用途广泛的多功能集 成电路。 目前锁相环应用广泛,比如:在通信中应用于调制解调自动频率微调等系统;在雷达中 应用于天线自动跟踪与精密辅角偏转测量等系统;在空间技术中主要应用于测速定轨、测距 与遥测数据获取等系统;在电视机中应用于电视机同步、门限扩展解调的同步检波。

1